**OPT3001**

SBOS681B-JULY 2014-REVISED DECEMBER 2014

# **OPT3001 Ambient Light Sensor (ALS)**

#### **Features**

- Precision Optical Filtering to Match Human Eye:

- Rejects > 99% (typ) of IR

- Automatic Full-Scale Setting Feature Simplifies Software and Ensures Proper Configuration

- Measurements: 0.01 lux to 83k lux

- 23-Bit Effective Dynamic Range with Automatic Gain Ranging

- 12 Binary-Weighted Full-Scale Range Settings: < 0.2% (typ) Matching Between Ranges

- Low Operating Current: 1.8 µA (typ)

- Operating Temperature Range: -40°C to +85°C

- Wide Power-Supply Range: 1.6 V to 3.6 V

- 5.5-V Tolerant I/O

- Flexible Interrupt System

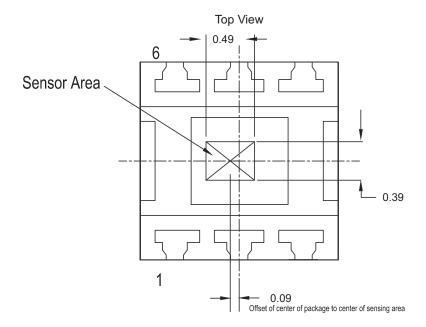

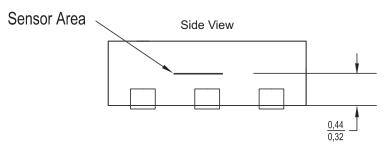

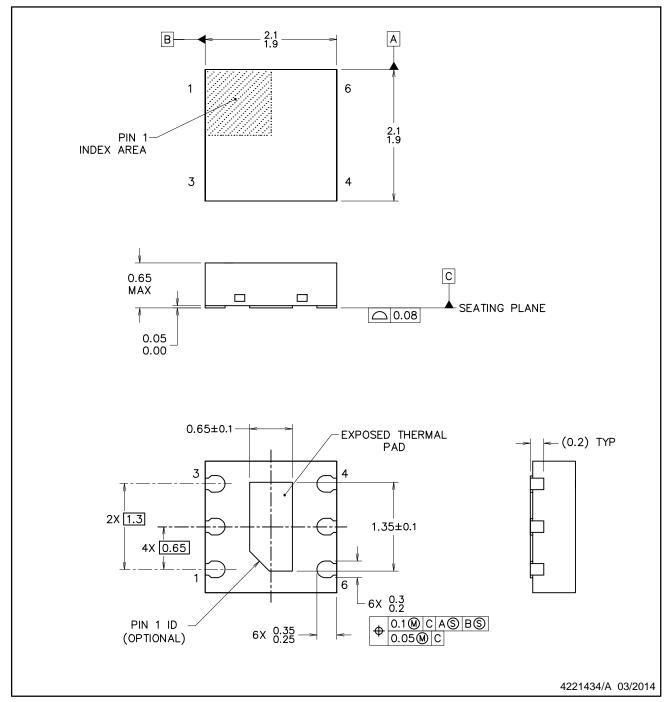

- Small-Form Factor: 2.0 mm x 2.0 mm x 0.65 mm

### **Applications**

- Display Backlight Controls

- **Lighting Control Systems**

- **Tablet and Notebook Computers**

- Thermostats and Home Automation Appliances

- Point-of-Sale Terminals

- Outdoor Traffic and Street Lights

- Cameras

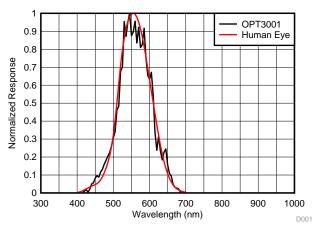

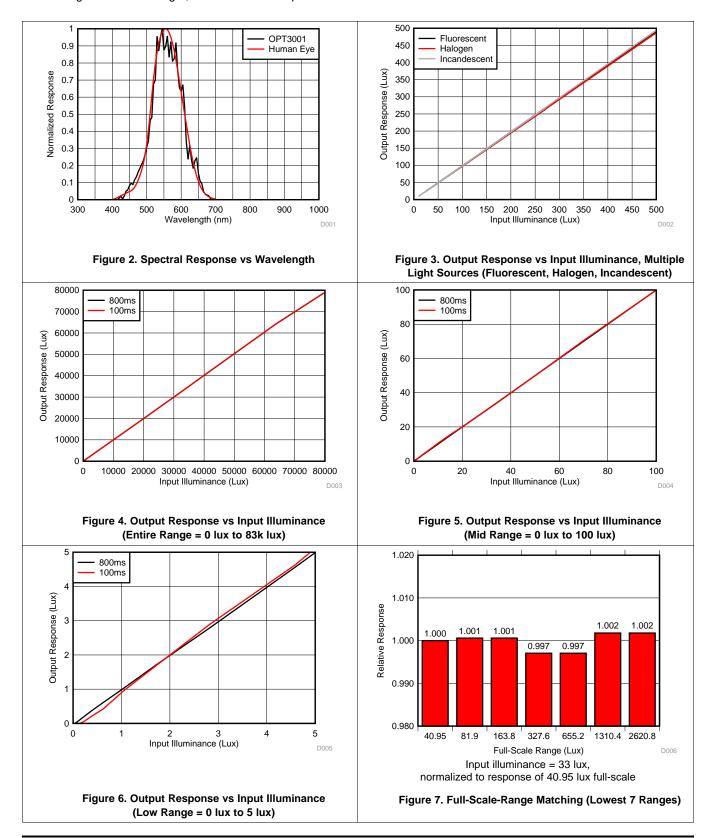

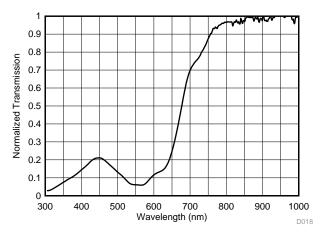

### Spectral Response: The OPT3001 and Human Eye

### 3 Description

The OPT3001 is a sensor that measures the intensity of visible light. The spectral response of the sensor tightly matches the photopic response of the human eye and includes significant infrared rejection.

The OPT3001 is a single-chip lux meter, measuring the intensity of light as visible by the human eye. The precision spectral response and strong IR rejection of the device enables the OPT3001 to accurately meter the intensity of light as seen by the human eye regardless of light source. The strong IR rejection also aids in maintaining high accuracy when industrial design calls for mounting the sensor under dark glass for aesthetics. The OPT3001 is designed for systems that create light-based experiences for humans, and an ideal preferred replacement for photodiodes, photoresistors, or other ambient light sensors with less human eye matching and IR rejection.

Measurements can be made from 0.01 lux up to 83k lux without manually selecting full-scale ranges by using the built-in, full-scale setting feature. This capability allows light measurement over a 23-bit effective dynamic range.

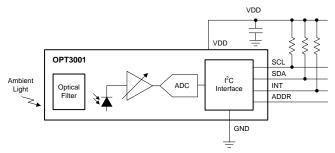

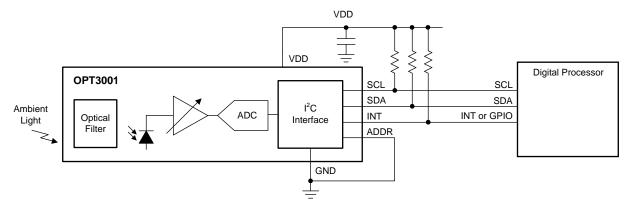

The digital operation is flexible for system integration. Measurements can be either continuous or singleshot. The control and interrupt system features autonomous operation, allowing the processor to sleep while the sensor searches for appropriate wake-up events to report via the interrupt pin. The digital output is reported over an I<sup>2</sup>C- and SMBuscompatible, two-wire serial interface.

The low power consumption and low power-supply voltage capability of the OPT3001 enhance the battery life of battery-powered systems.

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE  | BODY SIZE (NOM)   |  |  |

|-------------|----------|-------------------|--|--|

| OPT3001     | USON (6) | 2.00 mm x 2.00 mm |  |  |

(1) For all available packages, see the package option addendum at the end of the datasheet.

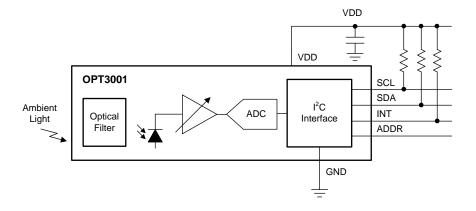

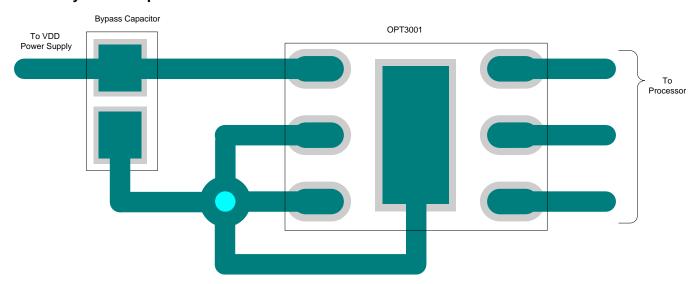

### **Block Diagram**

# **Table of Contents**

| 1 Features                                                      | 19             |

|-----------------------------------------------------------------|----------------|

| 3 Description                                                   |                |

|                                                                 | ~              |

| A B 4.1 Application Information                                 |                |

| 4 Revision History                                              | 27             |

| 5 Pin Configuration and Functions                               | 28             |

| 6 Specifications4 8.3 Do's and Don'ts                           | 31             |

| 6.1 Absolute Maximum Ratings                                    | ns 32          |

| 6.2 ESD Ratings                                                 | 33             |

| 6.3 Recommended Operating Conditions                            |                |

| 6.4 Thermal Information                                         | 33             |

| 6.5 Electrical Characteristics 5 11 Device and Documentation Su | pport 34       |

| 6.6 Timing Requirements 6 11.1 Documentation Support            | 34             |

| 6.7 Typical Characteristics                                     |                |

| 7 Detailed Description                                          | n 34           |

| 7.1 Overview                                                    | 34             |

| 7.2 Functional Block Diagram                                    | rderable       |

| 7.3 Feature Description                                         | 34             |

| 7.4 Device Functional Modes                                     | nmendations 34 |

| 12.2 DNP (S-PDSO-N6) Mechanica                                  | al Drawings 35 |

# 4 Revision History

| Changes from Revision A (October 2014) to Revision B                           | Page |

|--------------------------------------------------------------------------------|------|

| Changed Handling Ratings table to ESD Ratings table                            |      |

| Added missing link to Electrical Interface section in Serial Interface section | 12   |

| Added application information to Application and Implementation section        | 27   |

| Added new documents to Related Documentation section                           | 34   |

| Added Soldering and Handling Recommendations section                           |      |

| Changes from Original (July 2014) to Revision A                                | Page |

| Changed data sheet from product preview to production data                     | 1    |

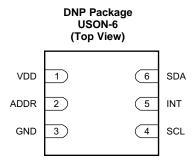

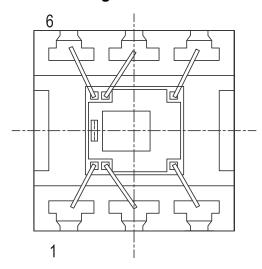

# 5 Pin Configuration and Functions

**Table 1. Pin Functions**

| P   | IN   |                      | DESCRIPTION                                                                            |  |  |  |

|-----|------|----------------------|----------------------------------------------------------------------------------------|--|--|--|

| NO. | NAME | I/O                  | DESCRIPTION                                                                            |  |  |  |

| 1   | VDD  | Power                | Device power. Connect to a 1.6-V to 3.6-V supply.                                      |  |  |  |

| 2   | ADDR | Digital input        | Address pin. This pin sets the LSBs of the I <sup>2</sup> C address.                   |  |  |  |

| 3   | GND  | Power                | Ground                                                                                 |  |  |  |

| 4   | SCL  | Digital input        | I <sup>2</sup> C clock. Connect with a 10-kΩ resistor to a 1.6-V to 5.5-V supply.      |  |  |  |

| 5   | INT  | Digital output       | Interrupt output open-drain. Connect with a 10-kΩ resistor to a 1.6-V to 5.5-V supply. |  |  |  |

| 6   | SDA  | Digital input/output | $I^2$ C data. Connect with a 10-kΩ resistor to a 1.6-V to 5.5-V supply.                |  |  |  |

## 6 Specifications

### 6.1 Absolute Maximum Ratings<sup>(1)</sup>

|                      |                                | MIN  | MAX                 | UNIT |

|----------------------|--------------------------------|------|---------------------|------|

| Voltage              | VDD to GND                     | -0.5 | 6                   | V    |

|                      | SDA, SCL, INT, and ADDR to GND | -0.5 | 6                   | V    |

| Current into any pin | ·                              |      | 10                  | mA   |

| Temperature          | Junction                       |      | 150                 | °C   |

|                      | Storage, T <sub>stg</sub>      | -65  | +150 <sup>(2)</sup> | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) Long exposure to temperatures higher than 105°C can cause package discoloration, spectral distortion, and measurement inaccuracy.

### 6.2 ESD Ratings

|                    |               |                                                                     | VALUE | UNIT |

|--------------------|---------------|---------------------------------------------------------------------|-------|------|

| V                  | Electrostatic | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)              | ±2000 | V    |

| V <sub>(ESD)</sub> | discharge     | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2) | ±500  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

### 6.3 Recommended Operating Conditions

|                                | MIN | NOM MAX | UNIT |

|--------------------------------|-----|---------|------|

| Operating temperature          | -40 | 85      | °C   |

| Operating power-supply voltage | 1.6 | 3.6     | V    |

### 6.4 Thermal Information

|                        |                                              | OPT3001    |       |

|------------------------|----------------------------------------------|------------|-------|

|                        | THERMAL METRIC <sup>(1)</sup>                | DNP (USON) | UNIT  |

|                        |                                              | 6 PINS     |       |

| $R_{\theta JA}$        | Junction-to-ambient thermal resistance       | 71.2       |       |

| R <sub>0</sub> JC(top) | Junction-to-case (top) thermal resistance    | 45.7       |       |

| $R_{\theta JB}$        | Junction-to-board thermal resistance         | 42.2       | 90044 |

| Ψлт                    | Junction-to-top characterization parameter   | 2.4        | °C/W  |

| ΨЈВ                    | Junction-to-board characterization parameter | 42.8       |       |

| R <sub>0JC(bot)</sub>  | Junction-to-case (bottom) thermal resistance | 17.0       |       |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

#### 6.5 Electrical Characteristics

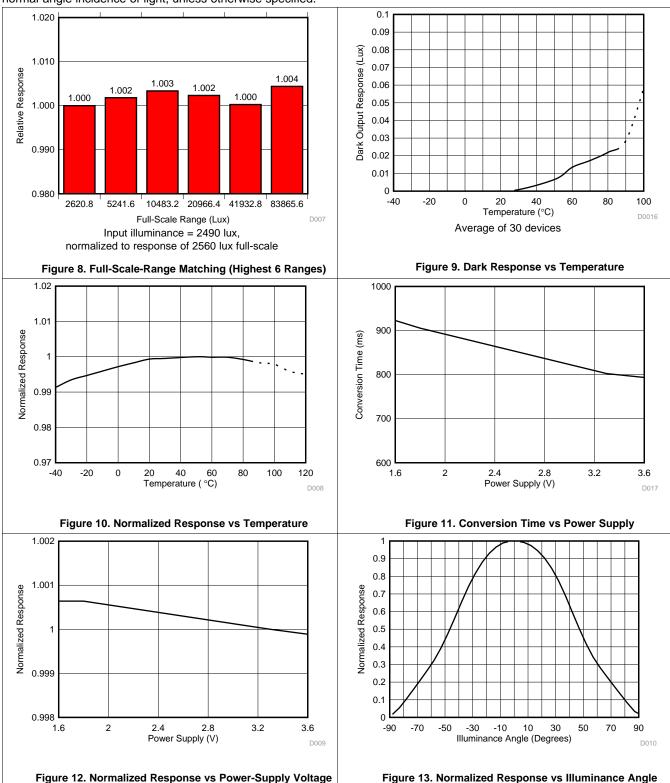

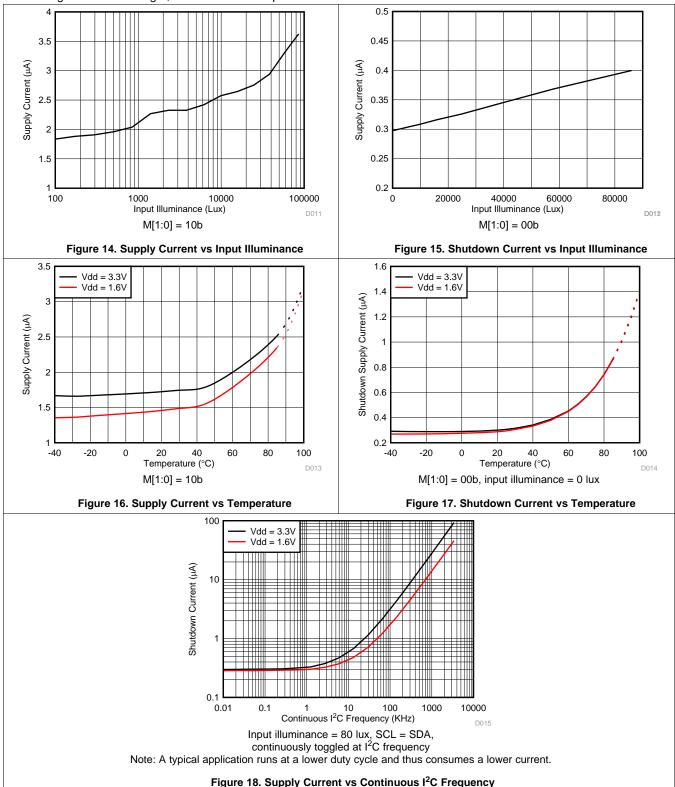

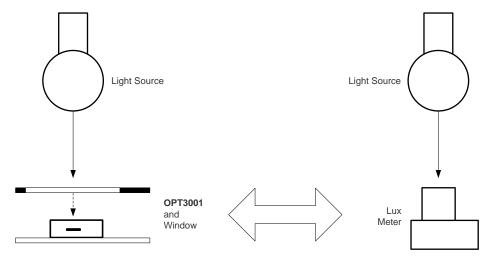

At  $T_A = 25$ °C,  $V_{DD} = 3.3$  V, 800-ms conversion time (CT = 1)<sup>(1)</sup>, automatic full-scale range (RN[3:0] = 1100b<sup>(1)</sup>), white LED, and normal-angle incidence of light, unless otherwise specified.

|                 | PARAMETER                                                   | TE                                             | EST CONDITIONS                                                      | MIN                   | TYP     | MAX                   | UNIT               |

|-----------------|-------------------------------------------------------------|------------------------------------------------|---------------------------------------------------------------------|-----------------------|---------|-----------------------|--------------------|

| OPTICAL         |                                                             |                                                |                                                                     |                       |         |                       |                    |

|                 | Peak irradiance spectral responsivity                       |                                                |                                                                     |                       | 550     |                       | nm                 |

|                 | Resolution (LSB)                                            | Lowest full-scal                               | e range, RN[3:0] = 0000b <sup>(1)</sup>                             |                       | 0.01    |                       | lux                |

|                 | Full-scale illuminance                                      |                                                |                                                                     |                       | 83865.6 |                       | lux                |

|                 | Management and an extensity and other                       | 0.64 lux per AD                                | 0.64 lux per ADC code, 2620.80 lux full-scale                       | 2812                  | 3125    | 3437                  | ADC codes          |

|                 | Measurement output result                                   | (RN[3:0] = 0110                                | )) <sup>(1)</sup> , 2000 lux input <sup>(2)</sup>                   | 1800                  | 2000    | 2200                  | lux                |

|                 | Relative accuracy between gain ranges (3)                   |                                                |                                                                     |                       | 0.2%    |                       |                    |

|                 | Infrared response (850 nm) <sup>(2)</sup>                   |                                                |                                                                     |                       | 0.2%    |                       |                    |

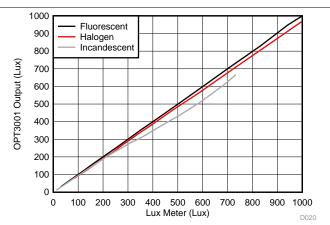

|                 | Light source variation (incandescent, halogen, fluorescent) | Bare device, no                                | cover glass                                                         |                       | 4%      |                       |                    |

|                 | Linearity                                                   | Input illuminand                               | e > 40 lux                                                          |                       | 2%      |                       |                    |

|                 | Linearity                                                   | Input illuminand                               | e < 40 lux                                                          |                       | 5%      |                       |                    |

|                 | Measurement drift across temperature                        | Input illuminand                               | e = 2000 lux                                                        |                       | 0.01    |                       | %/°C               |

|                 | Dark condition, ADC output                                  | 0.01 lux per AD                                | Coodo                                                               |                       | 0       | 3                     | ADC codes          |

|                 | Dark condition, ADC output                                  | 0.01 lux pei AD                                | C code                                                              |                       | 0       | 0.03                  | lux                |

|                 | Half-power angle                                            | 50% of full-pow                                | er reading                                                          |                       | 47      |                       | degrees            |

| PSRR            | Power-supply rejection ratio                                | V <sub>DD</sub> at 3.6 V an                    | d 1.6 V                                                             |                       | 0.1     |                       | %/V <sup>(4)</sup> |

| POWER SU        | PPLY                                                        |                                                |                                                                     |                       |         |                       |                    |

| $V_{DD}$        | Operating range                                             |                                                |                                                                     | 1.6                   |         | 3.6                   | V                  |

| $V_{I^2C}$      | Operating range of I <sup>2</sup> C pull-up resistor        | $I^2C$ pull-up resistor, $V_{DD} \le V_{I^2C}$ |                                                                     | 1.6                   |         | 5.5                   | ٧                  |

|                 |                                                             |                                                | Active, $V_{DD} = 3.6 \text{ V}$                                    |                       | 1.8     | 2.5                   | μΑ                 |

|                 | Quiescent current                                           | Dark                                           | Shutdown (M[1:0] = 00) <sup>(1)</sup> ,<br>$V_{DD} = 3.6 \text{ V}$ |                       | 0.3     | 0.47                  | μΑ                 |

| lα              | Quiescent current                                           |                                                | Active, V <sub>DD</sub> = 3.6 V                                     |                       | 3.7     |                       | μΑ                 |

|                 |                                                             | Full-scale lux                                 | Shutdown,<br>(M[1:0] = 00) <sup>(1)</sup>                           |                       | 0.4     |                       | μΑ                 |

| POR             | Power-on-reset threshold                                    | T <sub>A</sub> = 25°C                          |                                                                     |                       | 0.8     |                       | V                  |

| DIGITAL         |                                                             |                                                |                                                                     |                       |         |                       |                    |

|                 | I/O pin capacitance                                         |                                                |                                                                     |                       | 3       |                       | pF                 |

|                 | Total integration time <sup>(5)</sup>                       | $(CT = 1)^{(1)}$ , 800                         | -ms mode, fixed lux range                                           | 720                   | 800     | 880                   | ms                 |

|                 | rotal integration time **                                   | $(CT = 0)^{(1)}, 100$                          | -ms mode, fixed lux range                                           | 90                    | 100     | 110                   | ms                 |

| V <sub>IL</sub> | Low-level input voltage<br>(SDA, SCL, and ADDR)             |                                                |                                                                     | 0                     |         | 0.3 × V <sub>DD</sub> | V                  |

| V <sub>IH</sub> | High-level input voltage (SDA, SCL, and ADDR)               |                                                |                                                                     | 0.7 × V <sub>DD</sub> |         | 5.5                   | V                  |

| I <sub>IL</sub> | Low-level input current (SDA, SCL, and ADDR)                |                                                |                                                                     |                       | 0.01    | 0.25(6)               | μA                 |

| V <sub>OL</sub> | Low-level output voltage (SDA and INT)                      | I <sub>OL</sub> = 3 mA                         |                                                                     |                       |         | 0.32                  | V                  |

| I <sub>ZH</sub> | Output logic high, high-Z leakage current (SDA, INT)        | Pin at V <sub>DD</sub>                         |                                                                     |                       | 0.01    | 0.25 <sup>(6)</sup>   | μA                 |

| TEMPERAT        | URE                                                         |                                                |                                                                     |                       |         |                       |                    |

|                 | Specified temperature range                                 |                                                |                                                                     | -40                   |         | 85                    | °C                 |

- Refers to a control field within the configuration register.

- Tested with the white LED calibrated to 2k lux and an 850-nm LED.

- Characterized by measuring fixed near-full-scale light levels on the higher adjacent full-scale range setting.

PSRR is the percent change of the measured lux output from its current value, divided by the change in power supply voltage, as characterized by results from 3.6-V and 1.6-V power supplies.

- The conversion time, from start of conversion until the data are ready to be read, is the integration time plus 3 ms.

- (6) The specified leakage current is dominated by the production test equipment limitations. Typical values are much smaller.

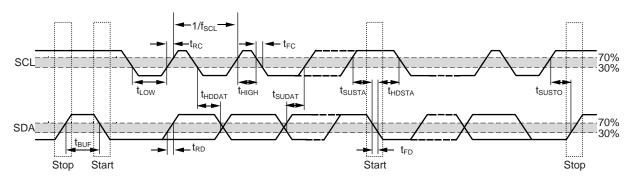

# 6.6 Timing Requirements<sup>(1)</sup>

|                                     |                                                                                                            | MIN  | TYP | MAX | UNIT |

|-------------------------------------|------------------------------------------------------------------------------------------------------------|------|-----|-----|------|

| I <sup>2</sup> C FAST MOD           | E                                                                                                          |      |     |     |      |

| f <sub>SCL</sub>                    | SCL operating frequency                                                                                    | 0.01 |     | 0.4 | MHz  |

| t <sub>BUF</sub>                    | Bus free time between stop and start                                                                       | 1300 |     |     | ns   |

| t <sub>HDSTA</sub>                  | Hold time after repeated start                                                                             | 600  |     |     | ns   |

| t <sub>SUSTA</sub>                  | Setup time for repeated start                                                                              | 600  |     |     | ns   |

| t <sub>SUSTO</sub>                  | Setup time for stop                                                                                        | 600  |     |     | ns   |

| t <sub>HDDAT</sub>                  | Data hold time                                                                                             | 20   |     | 900 | ns   |

| t <sub>SUDAT</sub>                  | Data setup time                                                                                            | 100  |     |     | ns   |

| $t_{LOW}$                           | SCL clock low period                                                                                       | 1300 |     |     | ns   |

| t <sub>HIGH</sub>                   | SCL clock high period                                                                                      | 600  |     |     | ns   |

| t <sub>RC</sub> and t <sub>FC</sub> | Clock rise and fall time                                                                                   |      |     | 300 | ns   |

| t <sub>RD</sub> and t <sub>FD</sub> | Data rise and fall time                                                                                    |      |     | 300 | ns   |

| t <sub>TIMEO</sub>                  | Bus timeout period. If the SCL line is held low for this duration of time, the bus state machine is reset. |      | 28  |     | ms   |

| I <sup>2</sup> C HIGH-SPEE          | ED MODE                                                                                                    |      |     |     |      |

| f <sub>SCL</sub>                    | SCL operating frequency                                                                                    | 0.01 |     | 2.6 | MHz  |

| t <sub>BUF</sub>                    | Bus free time between stop and start                                                                       | 160  |     |     | ns   |

| t <sub>HDSTA</sub>                  | Hold time after repeated start                                                                             | 160  |     |     | ns   |

| t <sub>SUSTA</sub>                  | Setup time for repeated start                                                                              | 160  |     |     | ns   |

| t <sub>SUSTO</sub>                  | Setup time for stop                                                                                        | 160  |     |     | ns   |

| t <sub>HDDAT</sub>                  | Data hold time                                                                                             | 20   |     | 140 | ns   |

| t <sub>SUDAT</sub>                  | Data setup time                                                                                            | 20   |     |     | ns   |

| t <sub>LOW</sub>                    | SCL clock low period                                                                                       | 240  |     |     | ns   |

| t <sub>HIGH</sub>                   | SCL clock high period                                                                                      | 60   |     |     | ns   |

| t <sub>RC</sub> and t <sub>FC</sub> | Clock rise and fall time                                                                                   |      |     | 40  | ns   |

| t <sub>RD</sub> and t <sub>FD</sub> | Data rise and fall time                                                                                    |      |     | 80  | ns   |

| t <sub>TIMEO</sub>                  | Bus timeout period. If the SCL line is held low for this duration of time, the bus state machine is reset. |      | 28  |     | ms   |

(1) All timing parameters are referenced to low and high voltage thresholds of 30% and 70%, respectively, of final settled value.

Figure 1. I<sup>2</sup>C Detailed Timing Diagram

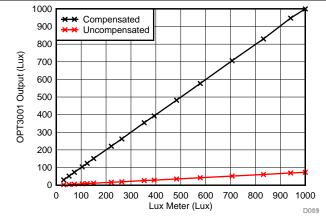

### 6.7 Typical Characteristics

At  $T_A = 25$ °C,  $V_{DD} = 3.3$  V, 800-ms conversion time (CT = 1), automatic full-scale range (RN[3:0] = 1100b), white LED, and normal-angle incidence of light, unless otherwise specified.

Submit Documentation Feedback

# **Typical Characteristics (continued)**

At  $T_A = 25$ °C,  $V_{DD} = 3.3$  V, 800-ms conversion time (CT = 1), automatic full-scale range (RN[3:0] = 1100b), white LED, and normal-angle incidence of light, unless otherwise specified.

Submit Documentation Feedback

Copyright © 2014, Texas Instruments Incorporated

### **Typical Characteristics (continued)**

At  $T_A = 25$ °C,  $V_{DD} = 3.3$  V, 800-ms conversion time (CT = 1), automatic full-scale range (RN[3:0] = 1100b), white LED, and normal-angle incidence of light, unless otherwise specified.

### 7 Detailed Description

#### 7.1 Overview

The OPT3001 measures the ambient light that illuminates the device. This device measures light with a spectral response very closely matched to the human eye, and with very good infrared rejection.

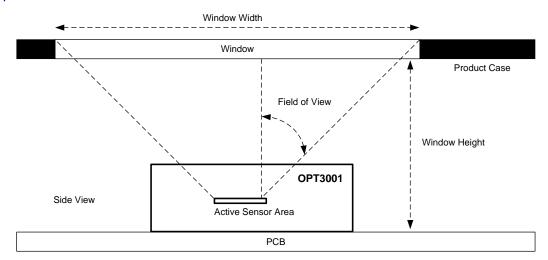

Matching the sensor spectral response to that of the human eye response is vital because ambient light sensors are used to measure and help create ideal human lighting experiences. Strong rejection of infrared light, which a human does not see, is a crucial component of this matching. This matching makes the OPT3001 especially good for operation underneath windows that are visibly dark, but infrared transmissive.

The OPT3001 is fully self-contained to measure the ambient light and report the result in lux digitally over the I<sup>2</sup>C bus. The result can also be used to alert a system and interrupt a processor with the INT pin. The result can also be summarized with a programmable window comparison and communicated with the INT pin.

The OPT3001 can be configured into an automatic full-scale, range-setting mode that always selects the optimal full-scale range setting for the lighting conditions. This mode frees the user from having to program their software for potential iterative cycles of measurement and readjustment of the full-scale range until optimal for any given measurement. The device can be commanded to operate continuously or in single-shot measurement modes.

The device integrates its result over either 100 ms or 800 ms, so the effects of 50-Hz and 60-Hz noise sources from typical light bulbs are nominally reduced to a minimum.

The device starts up in a low-power shutdown state, such that the OPT3001 only consumes active-operation power after being programmed into an active state.

The OPT3001 optical filtering system is not excessively sensitive to non-ideal particles and micro-shadows on the optical surface. This reduced sensitivity is a result of the relatively minor device dependency on uniform-density optical illumination of the sensor area for infrared rejection. Proper optical surface cleanliness is always recommended for best results on all optical devices.

### 7.2 Functional Block Diagram

Copyright © 2014, Texas Instruments Incorporated Product Folder Links: *OPT3001*

### 7.3 Feature Description

### 7.3.1 Human Eye Matching

The OPT3001 spectral response closely matches that of the human eye. If the ambient light sensor measurement is used to help create a good human experience, or create optical conditions that are optimal for a human, the sensor must measure the same spectrum of light that a human sees.

The device also has excellent infrared light (IR) rejection. This IR rejection is especially important because many real-world lighting sources have significant infrared content that humans do not see. If the sensor measures infrared light that the human eye does not see, then a true human experience is not accurately represented.

Furthermore, if the ambient light sensor is hidden underneath a dark window (such that the end-product user cannot see the sensor) the infrared rejection of the OPT3001 becomes significantly more important because many dark windows attenuate visible light but transmit infrared light. This attenuation of visible light and lack of attenuation of IR light amplifies the ratio of the infrared light to visible light that illuminates the sensor. Results can still be well matched to the human eye under this condition because of the high infrared rejection of the OPT3001.

#### 7.3.2 Automatic Full-Scale Range Setting

The OPT3001 has an automatic full-scale range setting feature that eliminates the need to predict and set the optimal range for the device. In this mode, the OPT3001 automatically selects the optimal full-scale range for the given lighting condition. The OPT3001 has a high degree of result matching between the full-scale range settings. This matching eliminates the problem of varying results or the need for range-specific, user-calibrated gain factors when different full-scale ranges are chosen. For further details, see the *Automatic Full-Scale Setting Mode* section.

#### 7.3.3 Interrupt Operation, INT Pin, and Interrupt Reporting Mechanisms

The device has an interrupt reporting system that allows the processor connected to the I<sup>2</sup>C bus to go to sleep, or otherwise ignore the device results, until a user-defined event occurs that requires possible action. Alternatively, this same mechanism can also be used with any system that can take advantage of a single digital signal that indicates whether the light is above or below levels of interest.

The interrupt event conditions are controlled by the high-limit and low-limit registers, as well as the configuration register latch and fault count fields. The results of comparing the result register with the high-limit register and low-limit register are referred to as *fault events*. The fault count register dictates how many consecutive same-result fault events are required to trigger an interrupt event and subsequently change the state of the interrupt reporting mechanisms, which are the INT pin, the flag high field, and the flag low field. The latch field allows a choice between a latched window-style comparison and a transparent hysteresis-style comparison.

The INT pin has an open-drain output, which requires the use of a pull-up resistor. This open-drain output allows multiple devices with open-drain INT pins to be connected to the same line, thus creating a logical *NOR* or *AND* function between the devices. The polarity of the INT pin can be controlled with the polarity of interrupt field in the configuration register. When the POL field is set to 0, the pin operates in an active low behavior that pulls the pin low when the INT pin becomes active. When the POL field is set to 1, the pin operates in an active high behavior and becomes high impedance, thus allowing the pin to go high when the INT pin becomes active.

Additional details of the interrupt reporting registers are described in the *Interrupt Reporting Mechanism Modes* and *Internal Registers* sections.

### **Feature Description (continued)**

#### 7.3.4 I<sup>2</sup>C Bus Overview

The OPT3001 offers compatibility with both  $I^2C$  and SMBus interfaces. The  $I^2C$  and SMBus protocols are essentially compatible with one another. The  $I^2C$  interface is used throughout this document as the primary example with the SMBus protocol specified only when a difference between the two protocols is discussed.

The OPT3001 is connected to the bus with two pins: an SCL clock input pin and an SDA open-drain bidirectional data pin. The bus must be controlled by a master device that generates the serial clock (SCL), controls the bus access, and generates start and stop conditions. To address a specific device, the master initiates a start condition by pulling the data signal line (SDA) from a high logic level to a low logic level while SCL is high. All slaves on the bus shift in the slave address byte on the SCL rising edge, with the last bit indicating whether a read or write operation is intended. During the ninth clock pulse, the slave being addressed responds to the master by generating an acknowledge bit by pulling SDA low.

Data transfer is then initiated and eight bits of data are sent, followed by an acknowledge bit. During data transfer, SDA must remain stable while SCL is high. Any change in SDA while SCL is high is interpreted as a start or stop condition. When all data are transferred, the master generates a stop condition, indicated by pulling SDA from low to high while SCL is high. The OPT3001 includes a 28-ms timeout on the I<sup>2</sup>C interface to prevent locking up the bus. If the SCL line is held low for this duration of time, the bus state machine is reset.

#### 7.3.4.1 Serial Bus Address

To communicate with the OPT3001, the master must first initiate an I<sup>2</sup>C start command. Then, the master must address slave devices via a slave address byte. The slave address byte consists of seven address bits and a direction bit that indicates whether the action is to be a read or write operation.

Four I<sup>2</sup>C addresses are possible by connecting the ADDR pin to one of four pins: GND, VDD, SDA, or SCL. Table 2 summarizes the possible addresses with the corresponding ADDR pin configuration. The state of the ADDR pin is sampled on every bus communication and must be driven or connected to the desired level before any activity on the interface occurs.

DEVICE I²C ADDRESS

ADDR PIN

1000100

GND

1000101

VDD

1000110

SDA

1000111

SCL

Table 2. Possible I<sup>2</sup>C Addresses with Corresponding ADDR Configuration

#### 7.3.4.2 Serial Interface

The OPT3001 operates as a slave device on both the  $I^2C$  bus and SMBus. Connections to the bus are made via the SCL clock input line and the SDA open-drain I/O line. The OPT3001 supports the transmission protocol for standard mode (up to 100 kHz), fast mode (up to 400 kHz), and high-speed mode (up to 2.6 MHz). All data bytes are transmitted most-significant bits first.

The SDA and SCL pins feature integrated spike-suppression filters and Schmitt triggers to minimize the effects of input spikes and bus noise. See the *Electrical Interface* section for further details of the I<sup>2</sup>C bus noise immunity.

#### 7.4 Device Functional Modes

### 7.4.1 Automatic Full-Scale Setting Mode

The OPT3001 has an automatic full-scale-range setting mode that eliminates the need for a user to predict and set the optimal range for the device. This mode is entered when the configuration register range number field (RN[3:0]) is set to 1100b.

The first measurement that the device takes in auto-range mode is a 10-ms range assessment measurement. The device then determines the appropriate full-scale range to take its first full measurement.

For subsequent measurements, the full-scale range is set by the result of the previous measurement. If a measurement is towards the low side of full-scale, the full-scale range is decreased by one or two settings for the next measurement. If a measurement is towards the upper side of full-scale, the full-scale range is increased by one setting for the next measurement.

If the measurement exceeds the full-scale range, resulting from a fast increasing optical transient event, the current measurement is aborted. This invalid measurement is not reported. A 10-ms measurement is taken to assess and properly reset the full-scale range. Then, a new measurement is taken with this proper full-scale range. Therefore, during a fast increasing optical transient in this mode, a measurement can possibly take longer to complete and report than indicated by the configuration register conversion time field (CT).

#### 7.4.2 Interrupt Reporting Mechanism Modes

There are two major types of interrupt reporting mechanism modes: latched window-style comparison mode and transparent hysteresis-style comparison mode. The configuration register latch field (L) (see the configuration register, bit 4) controls which of these two modes is used. An end-of-conversion mode is also associated with each major mode type. The end-of-conversion mode is active when the two most significant bits of the threshold low register are set to 11b. The mechanisms report via the flag high and flag low fields, the conversion ready field, and the INT pin.

#### 7.4.2.1 Latched Window-Style Comparison Mode

The latched window-style comparison mode is typically selected when using the OPT3001 to interrupt an external processor. In this mode, a fault is recognized when the input signal is above the high-limit register or below the low-limit register. When the consecutive fault events trigger the interrupt reporting mechanisms, these mechanisms are latched, thus reporting whether the fault is the result of a high or low comparison. These mechanisms remain latched until the configuration register is read, which clears the INT pin and flag high and flag low fields. The SMBus alert response protocol, described in detail in the SMBus Alert Response section, clears the pin but does not clear the flag high and flag low fields. The behavior of this mode, along with the conversion ready flag, is summarized in Table 3. Note that Table 3 does not apply when the two threshold low register MSBs (see the Transparent Hysteresis-Style Comparison Mode section for clarification on the MSBs) are set to 11b.

#### **Device Functional Modes (continued)**

Table 3. Latched Window-Style Comparison Mode: Flag Setting and Clearing Summary (1)(2)

| OPERATION                                                                                                                                            | FLAG HIGH<br>FIELD | FLAG LOW<br>FIELD | INT PIN <sup>(3)</sup> | CONVERSION READY FIELD |

|------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-------------------|------------------------|------------------------|

| The result register is above the high-limit register for fault count times. See the Result Register and the High-Limit Register for further details. | 1                  | Х                 | Active                 | 1                      |

| The result register is below the low-limit register for fault count times. See the Result Register and the Low-Limit Register for further details.   | Х                  | 1                 | Active                 | 1                      |

| The conversion is complete with fault count criterion not met                                                                                        | X                  | X                 | X                      | 1                      |

| Configuration register read <sup>(4)</sup>                                                                                                           | 0                  | 0                 | Inactive               | 0                      |

| Configuration register write, M[1:0] = 00b (shutdown)                                                                                                | X                  | X                 | X                      | X                      |

| Configuration register write, M[1:0] > 00b (not shutdown)                                                                                            | Х                  | Х                 | Х                      | 0                      |

| SMBus alert response protocol                                                                                                                        | X                  | Х                 | Inactive               | X                      |

- (1) X = no change from the previous state.

- (2) The high-limit register is assumed to be greater than the low-limit register. If this assumption is incorrect, the flag high field and flag low field can take on different behaviors.

- (3) The INT pin depends on the setting of the polarity field (POL). The INT pin is low when the pin state is active and POL = 0 (active low) or when the pin state is inactive and POL = 1 (active high).

- (4) Immediately after the configuration register is read, the device automatically resets the conversion ready field to its 0 state. Thus, if two configuration register reads are performed immediately after a conversion completion, the first reads 1 and the second reads 0.

#### 7.4.2.2 Transparent Hysteresis-Style Comparison Mode

The transparent hysteresis-style comparison mode is typically used when a single digital signal is desired that indicates whether the input light is higher than or lower than a light level of interest. If the result register is higher than the high-limit register for a consecutive number of events set by the fault count field, the INT line is set to active, the flag high field is set to 1, and the flag low field is set to 0. If the result register is lower than the low-limit register for a consecutive number of events set by the fault count field, the INT line is set to inactive, the flag low field is set to 1, and the flag high field is set to 0. The INT pin and flag high and flag low fields do not change state with configuration reads and writes. The INT pin and flag fields continually report the appropriate comparison of the light to the low-limit and high-limit registers. The device does not respond to the SMBus alert response protocol while in either of the two transparent comparison modes (configuration register, latch field = 0). The behavior of this mode, along with the conversion ready is summarized in Table 4. Note that Table 4 does not apply when the two threshold low register MSBs (LE[3:2] from Table 12) are set to 11.

Table 4. Transparent Hysteresis-Style Comparison Mode: Flag Setting and Clearing Summary (1)(2)

| OPERATION                                                                                                                                            | FLAG HIGH<br>FIELD | FLAG LOW<br>FIELD | INT PIN <sup>(3)</sup> | CONVERSION READY FIELD |

|------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-------------------|------------------------|------------------------|

| The result register is above the high-limit register for fault count times. See the Result Register and the High-Limit Register for further details. | 1                  | 0                 | Active                 | 1                      |

| The result register is below the low-limit register for fault count times. See the Result Register and the Low-Limit Register for further details.   | 0                  | 1                 | Inactive               | 1                      |

| The conversion is complete with fault count criterion not met                                                                                        | Х                  | X                 | Х                      | 1                      |

| Configuration register read <sup>(4)</sup>                                                                                                           | Х                  | Х                 | Х                      | 0                      |

| Configuration register write, M[1:0] = 00b (shutdown)                                                                                                | Х                  | Х                 | Х                      | Х                      |

| Configuration register write, M[1:0] > 00b (not shutdown)                                                                                            | Х                  | Х                 | Х                      | 0                      |

| SMBus alert response protocol                                                                                                                        | Х                  | Х                 | Х                      | Х                      |

- (1) X = no change from the previous state.

- (2) The high-limit register is assumed to be greater than the low-limit register. If this assumption is incorrect, the flag high field and flag low field can take on different behaviors.

- (3) The INT pin depends on the setting of the polarity field (POL). The INT pin is low when the pin state is active and POL = 0 (active low) or when the pin state is inactive and POL = 1 (active high).

- (4) Immediately after the configuration register is read, the device automatically resets the conversion ready field to its 0 state. Thus, if two configuration register reads are performed immediately after a conversion completion, the first reads 1 and the second reads 0.

#### 7.4.2.3 End-of-Conversion Mode

An end-of-conversion indicator mode can be used when every measurement is desired to be read by the processor, prompted by the INT pin going active on every measurement completion. This mode is entered by setting the most significant two bits of the low-limit register (LE[3:2] from the Low-Limit Register) to 11b. This end-of-conversion mode is typically used in conjunction with the latched window-style comparison mode. The INT pin becomes inactive when the configuration register is read or the configuration register is written with a non-shutdown parameter or in response to an SMBus alert response. Table 5 summarizes the interrupt reporting mechanisms as a result of various operations.

Table 5. End-of-Conversion Mode while in Latched Window-Style Comparison Mode: Flag Setting and Clearing Summary<sup>(1)</sup>

| OPERATION                                                                                                                                            | FLAG HIGH<br>FIELD | FLAG LOW<br>FIELD | INT PIN <sup>(2)</sup> | CONVERSION READY FIELD |

|------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-------------------|------------------------|------------------------|

| The result register is above the high-limit register for fault count times. See the Result Register and the High-Limit Register for further details. | 1                  | X                 | Active                 | 1                      |

| The result register is below the low-limit register for fault count times. See the Result Register and the Low-Limit Register for further details.   | X                  | 1                 | Active                 | 1                      |

| The conversion is complete with fault count criterion not met                                                                                        | X                  | X                 | Active                 | 1                      |

| Configuration register read <sup>(3)</sup>                                                                                                           | 0                  | 0                 | Inactive               | 0                      |

| Configuration register write, M[1:0] = 00b (shutdown)                                                                                                | Х                  | Х                 | Х                      | X                      |

| Configuration register write, M[1:0] > 00b (not shutdown)                                                                                            | Х                  | Х                 | Х                      | 0                      |

| SMBus alert response protocol                                                                                                                        | X                  | X                 | Inactive               | X                      |

- (1) X = no change from the previous state.

- (2) The INT pin depends on the setting of the polarity field (POL). The INT pin is low when the pin state is active and POL = 0 (active low) or when the pin state is inactive and POL = 1 (active high).

- (3) Immediately after the configuration register is read, the device automatically resets the conversion ready field to its 0 state. Thus, if two configuration register reads are performed immediately after a conversion completion, the first reads 1 and the second reads 0.

Note that when transitioning from end-of-conversion mode to the standard comparison modes (that is, programming LE[3:2] from 11b to 00b) while the configuration register latch field (L) is 1, a subsequent write to the configuration register latch field (L) to 0 is necessary in order to properly clear the INT pin. The latch field can then be set back to 1 if desired.

#### 7.4.2.4 End-of-Conversion and Transparent Hysteresis-Style Comparison Mode

The combination of end-of-conversion mode and transparent hysteresis-style comparison mode can also be programmed simultaneously. The behavior of this combination is shown in Table 6.

Table 6. End-Of-Conversion Mode while in Transparent Hysteresis-Style Comparison Mode: Flag Setting and Clearing Summary<sup>(1)</sup>

| OPERATION                                                                                                                                            | FLAG HIGH<br>FIELD | FLAG LOW<br>FIELD | INT PIN <sup>(2)</sup> | CONVERSION READY FIELD |

|------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-------------------|------------------------|------------------------|

| The result register is above the high-limit register for fault count times. See the Result Register and the High-Limit Register for further details. | 1                  | 0                 | Active                 | 1                      |

| The result register is below the low-limit register for fault count times. See the Result Register and the Low-Limit Register for further details.   | 0                  | 1                 | Active                 | 1                      |

| The conversion is complete with fault count criterion not met                                                                                        | X                  | X                 | Active                 | 1                      |

| Configuration register read <sup>(3)</sup>                                                                                                           | X                  | X                 | Inactive               | 0                      |

| Configuration register write, M[1:0] = 00b (shutdown)                                                                                                | X                  | X                 | X                      | X                      |

| Configuration register write, M[1:0] > 00b (not shutdown)                                                                                            | X                  | X                 | Inactive               | 0                      |

| SMBus alert response protocol                                                                                                                        | X                  | X                 | X                      | X                      |

- (1) X = no change from the previous state.

- (2) The INT pin depends on the setting of the polarity field (POL). The INT pin is low when the pin state is active and POL = 0 (active low) or when the pin state is inactive and POL = 1 (active high).

- (3) Immediately after the configuration register is read, the device automatically resets the conversion ready field to its 0 state. Thus, if two configuration register reads are performed immediately after a conversion completion, the first reads 1 and the second reads 0.

### 7.5 Programming

The OPT3001 supports the transmission protocol for standard mode (up to 100 kHz), fast mode (up to 400 kHz), and high-speed mode (up to 2.6 MHz). Fast and standard modes are described as the default protocol, referred to as F/S. High-speed mode is described in the High-Speed PC Mode section.

#### 7.5.1 Writing and Reading

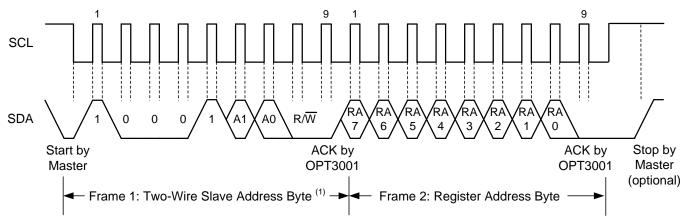

Accessing a specific register on the OPT3001 is accomplished by writing the appropriate register address during the I<sup>2</sup>C transaction sequence. Refer to Table 7 for a complete list of registers and their corresponding register addresses. The value for the register address (as shown in Figure 19) is the first byte transferred after the slave address byte with the R/W bit low.

(1) The value of the slave address byte is determined by the ADDR pin setting; see Table 2.

Figure 19. Setting the I<sup>2</sup>C Register Address

Writing to a register begins with the first byte transmitted by the master. This byte is the slave address with the R/W bit low. The OPT3001 then acknowledges receipt of a valid address. The next byte transmitted by the master is the address of the register that data are to be written to. The next two bytes are written to the register addressed by the register address. The OPT3001 acknowledges receipt of each data byte. The master may terminate the data transfer by generating a start or stop condition.

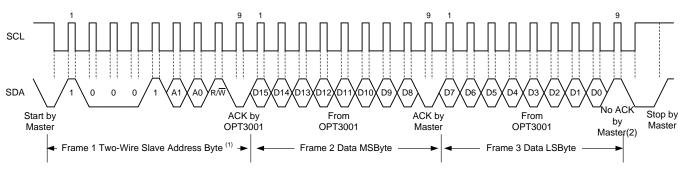

When reading from the OPT3001, the last value stored in the register address by a write operation determines which register is read during a read operation. To change the register address for a read operation, a new partial  $I^2C$  write transaction must be initiated. This partial write is accomplished by issuing a slave address byte with the R/W bit low, followed by the register address byte and a stop command. The master then generates a start condition and sends the slave address byte with the R/W bit high to initiate the read command. The next byte is transmitted by the slave and is the most significant byte of the register indicated by the register address. This byte is followed by an acknowledge from the master; then the slave transmits the least significant byte. The master acknowledges receipt of the data byte. The master may terminate the data transfer by generating a not-acknowledge after receiving any data byte, or by generating a start or stop condition. If repeated reads from the same register are desired, continually sending the register address bytes is not necessary; the OPT3001 retains the register address until that number is changed by the next write operation.

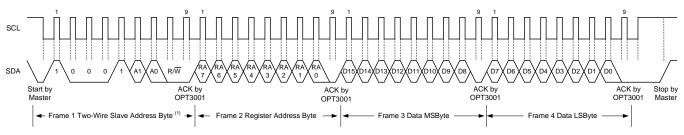

### **Programming (continued)**

Figure 20 and Figure 21 show the write and read operation timing diagrams, respectively. Note that register bytes are sent most significant byte first, followed by the least significant byte.

(1) The value of the slave address byte is determined by the setting of the ADDR pin; see Table 2.

### Figure 20. I<sup>2</sup>C Write Example

- (1) The value of the slave address byte is determined by the ADDR pin setting; see Table 2.

- (2) An ACK by the master can also be sent.

Figure 21. I<sup>2</sup>C Read Example

### 7.5.1.1 High-Speed I<sup>2</sup>C Mode

When the bus is idle, both the SDA and SCL lines are pulled high by the pull-up resistors or active pull-up devices. The master generates a start condition followed by a valid serial byte containing the high-speed (HS) master code 0000 1XXXb. This transmission is made in either standard mode or fast mode (up to 400 kHz). The OPT3001 does not acknowledge the HS master code but does recognize the code and switches its internal filters to support a 2.6-MHz operation.

The master then generates a repeated start condition (a repeated start condition has the same timing as the start condition). After this repeated start condition, the protocol is the same as F/S mode, except that transmission speeds up to 2.6 MHz are allowed. Instead of using a stop condition, use repeated start conditions to secure the bus in HS mode. A stop condition ends the HS mode and switches all internal filters of the OPT3001 to support the F/S mode.

#### 7.5.1.2 General-Call Reset Command

The  $I^2C$  general-call reset allows the host controller in one command to reset all devices on the bus that respond to the general-call reset command. The general call is initiated by writing to the  $I^2C$  address 0 (0000 0000b). The reset command is initiated when the subsequent second address byte is 06h (0000 0110b). With this transaction, the device issues an acknowledge bit and sets all of its registers to the power-on-reset default condition.

### **Programming (continued)**

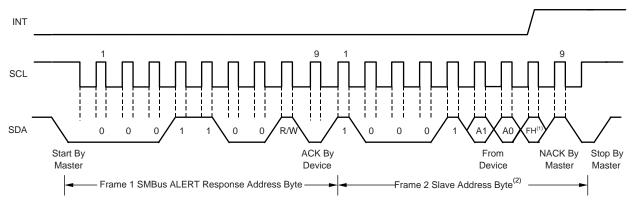

#### 7.5.1.3 SMBus Alert Response

The SMBus alert response provides a quick identification for which device issued the interrupt. Without this alert response capability, the processor does not know which device pulled the interrupt line when there are multiple slave devices connected.

The OPT3001 is designed to respond to the SMBus alert response address, when in the latched window-style comparison mode (configuration register, latch field = 1). The OPT3001 does not respond to the SMBus alert response when in transparent mode (configuration register, latch field = 0).

The response behavior of the OPT3001 to the SMBus alert response is shown in Figure 22. When the interrupt line to the processor is pulled to active, the master can broadcast the alert response slave address (0001 1001b). Following this alert response, any slave devices that generated an alert identify themselves by acknowledging the alert response and sending their respective I<sup>2</sup>C address on the bus. The alert response can activate several different slave devices simultaneously. If more than one slave attempts to respond, bus arbitration rules apply. The device with the lowest address wins the arbitration. If the OPT3001 loses the arbitration, the device does not acknowledge the I<sup>2</sup>C transaction and its INT pin remains in an active state, prompting the I<sup>2</sup>C master processor to issue a subsequent SMBus alert response. When the OPT3001 wins the arbitration, the device acknowledges the transaction and sets its INT pin to inactive. The master can issue that same command again, as many times as necessary to clear the INT pin. See the Interrupt Reporting Mechanism Modes section for additional details of how the flags and INT pin are controlled. The master can obtain information about the source of the OPT3001 interrupt from the address broadcast in the above process. The flag high field (configuration register, bit 6) is sent as the final LSB of the address to provide the master additional information about the cause of the OPT3001 interrupt. If the master requires additional information, the result register or the configuration register can be queried. The flag high and flag low fields are not cleared upon an SMBus alert response.

- (1) FH is the flag high field (FH) in the configuration register (see Table 11).

- (2) A1 and A0 are determined by the ADDR pin; see Table 2.

Figure 22. Timing Diagram for SMBus Alert Response

## 7.6 Register Maps

### 7.6.1 Internal Registers

The device is operated over the I<sup>2</sup>C bus with registers that contain configuration, status, and result information. All registers are 16 bits long.

There are four main registers: result, configuration, low-limit, and high-limit. There are also two ID registers: manufacturer ID and device ID. Table 7 lists these registers.

Table 7. Register Map

| REGISTER        | ADDRESS<br>(Hex) <sup>(1)</sup> | BIT 15 | BIT 14 | BIT 13 | BIT 12 | BIT 11 | BIT 10 | BIT 9 | BIT 8 | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|-----------------|---------------------------------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| Result          | 00h                             | E3     | E2     | E1     | E0     | R11    | R10    | R9    | R8    | R7    | R6    | R5    | R4    | R3    | R2    | R1    | R0    |

| Configuration   | 01h                             | RN3    | RN2    | RN1    | RN0    | СТ     | M1     | MO    | OVF   | CRF   | FH    | FL    | L     | POL   | ME    | FC1   | FC0   |

| Low Limit       | 02h                             | LE3    | LE2    | LE1    | LE0    | TL11   | TL10   | TL9   | TL8   | TL7   | TL6   | TL5   | TL4   | TL3   | TL2   | TL1   | TL0   |

| High Limit      | 03h                             | HE3    | HE2    | HE1    | HE0    | TH11   | TH10   | TH9   | TH8   | TH7   | TH6   | TH5   | TH4   | TH3   | TH2   | TH1   | TH0   |

| Manufacturer ID | 7Eh                             | ID15   | ID14   | ID13   | ID12   | ID11   | ID10   | ID9   | ID8   | ID7   | ID6   | ID5   | ID4   | ID3   | ID2   | ID1   | ID0   |

| Device ID       | 7Fh                             | DID15  | DID14  | DID13  | DID12  | DID11  | DID10  | DID9  | DID8  | DID7  | DID6  | DID5  | DID4  | DID3  | DID2  | DID1  | DID0  |

<sup>(1)</sup> Register offset and register address are used interchangeably.

#### 7.6.1.1 Register Descriptions

#### **NOTE**

Register offset and register address are used interchangeably.

#### 7.6.1.1.1 Result Register (offset = 00h)

This register contains the result of the most recent light to digital conversion. This 16-bit register has two fields: a 4-bit exponent and a 12-bit mantissa.

Figure 23. Result Register (Read-Only)

| 15 | 14 | 13 | 12 | 11  | 10  | 9  | 8  |

|----|----|----|----|-----|-----|----|----|

| E3 | E2 | E1 | E0 | R11 | R10 | R9 | R8 |

| R  | R  | R  | R  | R   | R   | R  | R  |

| 7  | 6  | 5  | 4  | 3   | 2   | 1  | 0  |

| R7 | R6 | R5 | R4 | R3  | R2  | R1 | R0 |

| R  | R  | R  | R  | R   | R   | R  | R  |

LEGEND: R = Read only

**Table 8. Result Register Field Descriptions**

| Bit   | Field   | Туре | Reset | Description                                                                                   |

|-------|---------|------|-------|-----------------------------------------------------------------------------------------------|

| 15:12 | E[3:0]  | R    | 0h    | Exponent. These bits are the exponent bits. Table 9 provides further details.                 |

| 11:0  | R[11:0] | R    | 000h  | Fractional result.  These bits are the result in straight binary coding (zero to full-scale). |

Table 9. Full-Scale Range and LSB Size as a Function of Exponent Level

| E3 | E2 | E1 | E0 | FULL-SCALE RANGE (lux) | LSB SIZE (lux per LSB) |

|----|----|----|----|------------------------|------------------------|

| 0  | 0  | 0  | 0  | 40.95                  | 0.01                   |

| 0  | 0  | 0  | 1  | 81.90                  | 0.02                   |

| 0  | 0  | 1  | 0  | 163.80                 | 0.04                   |

| 0  | 0  | 1  | 1  | 327.60                 | 0.08                   |

| 0  | 1  | 0  | 0  | 655.20                 | 0.16                   |

| 0  | 1  | 0  | 1  | 1310.40                | 0.32                   |

| 0  | 1  | 1  | 0  | 2620.80                | 0.64                   |

| 0  | 1  | 1  | 1  | 5241.60                | 1.28                   |

| 1  | 0  | 0  | 0  | 10483.20               | 2.56                   |

| 1  | 0  | 0  | 1  | 20966.40               | 5.12                   |

| 1  | 0  | 1  | 0  | 41932.80               | 10.24                  |

| 1  | 0  | 1  | 1  | 83865.60               | 20.48                  |

The formula to translate this register into lux is given in Equation 1:

$$lux = LSB\_Size \times R[11:0]$$

(1)

where:

LSB\_Size =

$$0.01 \times 2^{E[3:0]}$$

(2)

LSB\_Size can also be taken from Table 9. The complete lux equation is shown in Equation 3:

$$lux = 0.01 \times (2^{E[3:0]}) \times R[11:0]$$

(3)

A series of result register output examples with the corresponding LSB weight and resulting lux are given in Table 10. Note that many combinations of exponents (E[3:0]) and fractional results (R[11:0]) can map onto the same lux result, as shown in the examples of Table 10.

Table 10. Examples of Decoding the Result Register into lux

| RESULT REGISTER<br>(Bits 15:0, Binary) | EXPONENT<br>(E[3:0], Hex) | FRACTIONAL<br>RESULT<br>(R[11:0], Hex) | LSB WEIGHT<br>(lux, Decimal) | RESULTING LUX<br>(Decimal) |

|----------------------------------------|---------------------------|----------------------------------------|------------------------------|----------------------------|

| 0000 0000 0000 0001b                   | 00h                       | 001h                                   | 0.01                         | 0.01                       |

| 0000 1111 1111 1111b                   | 00h                       | FFFh                                   | 0.01                         | 40.95                      |

| 0011 0100 0101 0110b                   | 03h                       | 456h                                   | 0.08                         | 88.80                      |

| 0111 1000 1001 1010b                   | 07h                       | 89Ah                                   | 1.28                         | 2818.56                    |

| 1000 1000 0000 0000b                   | 08h                       | 800h                                   | 2.56                         | 5242.88                    |

| 1001 0100 0000 0000b                   | 09h                       | 400h                                   | 5.12                         | 5242.88                    |

| 1010 0010 0000 0000b                   | 0Ah                       | 200h                                   | 10.24                        | 5242.88                    |

| 1011 0001 0000 0000b                   | 0Bh                       | 100h                                   | 20.48                        | 5242.88                    |

| 1011 0000 0000 0001b                   | 0Bh                       | 001h                                   | 20.48                        | 20.48                      |

| 1011 1111 1111 1111b                   | 0Bh                       | FFFh                                   | 20.48                        | 83865.60                   |

Note that the exponent field can be disabled (set to zero) by enabling the exponent mask (configuration register, ME field = 1) and manually programming the full-scale range (configuration register, RN[3:0] < 1100b (0Ch)), allowing for simpler operation in a manually-programmed, full-scale mode. Calculating lux from the result register contents only requires multiplying the result register by the LSB weight (in lux) associated with the specific programmed full-scale range (see Table 9). See the Low-Limit Register for details.

See the configuration register conversion time field (CT, bit 11) description for more information on lux resolution as a function of conversion time.

#### 7.6.1.1.2 Configuration Register (offset = 01h) [reset = C810h]

This register controls the major operational modes of the device. This register has 11 fields, which are documented below. If a measurement conversion is in progress when the configuration register is written, the active measurement conversion immediately aborts. If the new configuration register directs a new conversion, that conversion is subsequently started.

Figure 24. Configuration Register

| 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| RN3 | RN2 | RN1 | RN0 | СТ  | M1  | MO  | OVF |

| R/W | R   |

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| CRF | FH  | FL  | L   | POL | ME  | FC1 | FC0 |

| R   | R   | R   | R/W | R/W | R/W | R/W | R/W |

LEGEND: R/W = Read/Write; R = Read only

**Table 11. Configuration Register Field Descriptions**

| Bit   | Field   | Туре | Reset | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------|---------|------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:12 | RN[3:0] | R/W  | 1100b | Range number field (read or write). The range number field selects the full-scale lux range of the device. The format of this field is the same as the result register exponent field (E[3:0]); see Table 9. When RN[3:0] is set to 1100b (0Ch), the device operates in automatic full-scale setting mode, as described in the Automatic Full-Scale Setting Mode section. In this mode, the automatically chosen range is reported in the result exponent (register 00h, E[3:0]). The device powers up as 1100 in automatic full-scale setting mode. Codes 1101b, 1110b, and 1111b (0Dh, 0Eh, and 0Fh) are reserved for future use. |

# **Table 11. Configuration Register Field Descriptions (continued)**

| Bit  | Field  | Туре | Reset | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------|--------|------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11   | СТ     | R/W  | 1b    | Conversion time field (read or write). The conversion time field determines the length of the light to digital conversion process. The choices are 100 ms and 800 ms. A longer integration time allows for a lower noise measurement.  The conversion time also relates to the effective resolution of the data conversion process. The 800-ms conversion time allows for the fully specified lux resolution. The 100-ms conversion time with full-scale ranges above 0101b for E[3:0] in the result and configuration registers also allows for the fully specified lux resolution. The 100-ms conversion time with full-scale ranges below and including 0101b for E[3:0] can reduce the effective result resolution by up to three bits, as a function of the selected full-scale range. Range 0101b reduces by one bit. Ranges 0100b, 0011b, 0010b, and 0001b reduces by two bits. Range 0000b reduces by three bits. The result register format and associated LSB weight does not change as a function of the conversion time. 0 = 100 ms 1 = 800 ms                                                                                                                                                                                                                                                                                                                                                                                                                      |