# 18-Bit SoftSpan I<sub>OUT</sub> DAC with Parallel I/O

#### **FEATURES**

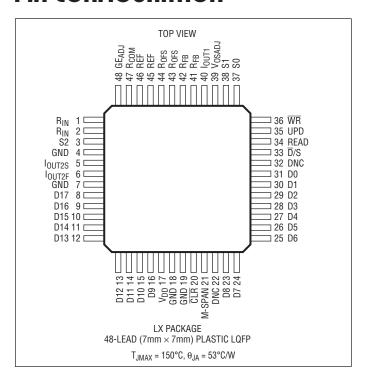

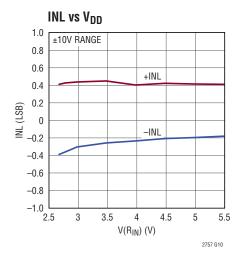

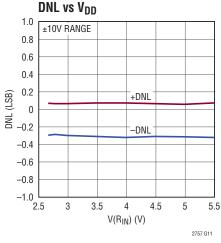

- Maximum 18-Bit INL Error: ±1 LSB Over Temperature

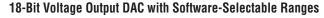

- Program or Pin-Strap Six Output Ranges: 0V to 5V, 0V to 10V, -2.5V to 7.5V, ±2.5V, ±5V, ±10V

- Guaranteed Monotonic Over Temperature

- Low Glitch Impulse 1.4nV•s (3V), 3nV•s (5V)

- 18-Bit Settling Time: 2.1µs

- 2.7V to 5.5V Single Supply Operation

- Reference Current Constant for All Codes

- Voltage-Controlled Offset and Gain Trims

- Parallel Interface with Readback of All Registers

- Clear and Power-On-Reset to 0V Regardless of Output Range

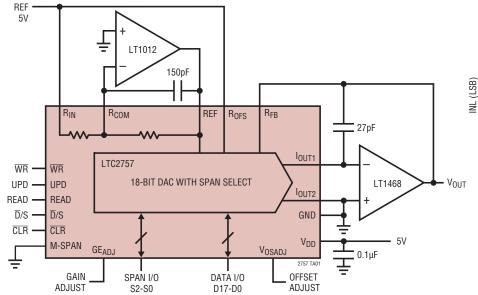

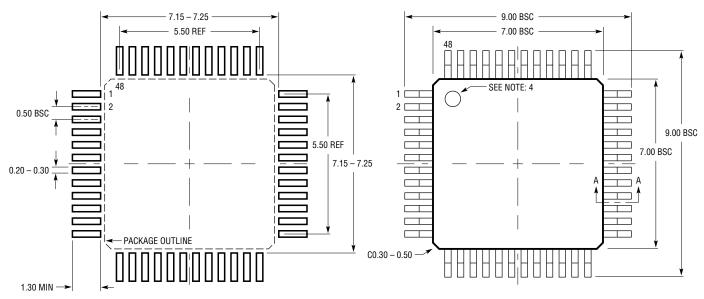

- 48-Pin 7mm × 7mm LQFP Package

#### **APPLICATIONS**

- Instrumentation

- Medical Devices

- Automatic Test Equipment

- Process Control and Industrial Automation

#### DESCRIPTION

The LTC®2757 is an 18-bit multiplying parallel-input, current-output digital-to-analog converter that provides full 18-bit performance—INL and DNL of  $\pm 1$ LSB maximum—over temperature without any adjustments. 18-bit monotonicity is guaranteed in all performance grades. This SoftSpan<sup>TM</sup> DAC operates from a single 3V to 5V supply and offers six output ranges (up to  $\pm 1$ 0V) that can be programmed through the parallel interface or pin-strapped for operation in a single range.

In addition to its precision DC specifications, the LTC2757 also offers excellent AC specifications, including 2.1µs full-scale settling to 1LSB and 1.4nV•s glitch impulse.

The LTC2757 uses a bidirectional input/output parallel interface that allows readback of any on-chip register, including DAC output-range settings; and a  $\overline{\text{CLR}}$  pin and power-on reset circuit that each reset the DAC output to OV regardless of output range.

LT, LT, LTC, LTM, Linear Technology and the Linear logo are registered trademarks of Linear Technology Corporation. SoftSpan is a trademark of Linear Technology Corporation.

All other trademarks are the property of their respective owners.

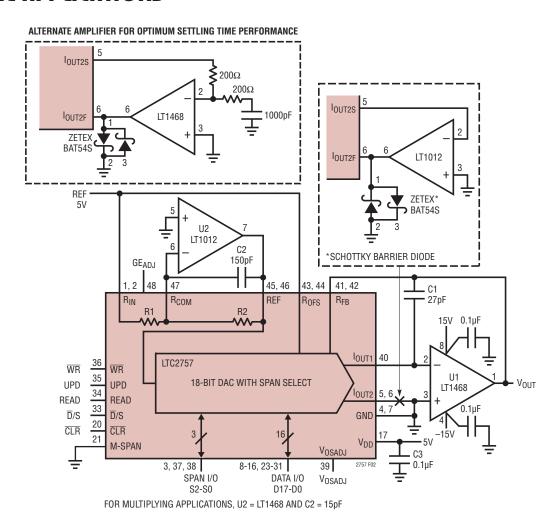

#### TYPICAL APPLICATION

#### 1.0 ±10V RANGE 8.0 0.6 0.4 0.2 -0.2-0.4-0.6■ 90°C -0.8 ■ 25°C ■ -45°C -1.0 65536 131072 196608 262143 CODE

LTC2757 Integral Nonlinearity

2757f

2757 TA01b

### **ABSOLUTE MAXIMUM RATINGS**

#### (Notes 1, 2)

| I <sub>OUT1</sub> , I <sub>OUT2</sub> , R <sub>COM</sub> to GND±0.3V                                           |

|----------------------------------------------------------------------------------------------------------------|

| R <sub>FB</sub> , R <sub>OFS</sub> , R <sub>IN</sub> , REF, V <sub>OSADJ</sub> , GE <sub>ADJ</sub> to GND ±15V |

| V <sub>DD</sub> to GND0.3V to 7V                                                                               |

| S2, S1, S0,                                                                                                    |

| D17-D0 to GND $-0.3V$ to $V_{DD} + 0.3V$ (7V Max)                                                              |

| WR, UPD, D/S, READ,                                                                                            |

| M-SPAN, CLR to GND0.3V to 7V                                                                                   |

| Operating Temperature Range                                                                                    |

| LTC2757C0°C to 70°C                                                                                            |

| LTC2757I40°C to 85°C                                                                                           |

| Maximum Junction Temperature 150°C                                                                             |

| Storage Temperature Range65°C to 150°C                                                                         |

| Lead Temperature (Soldering, 10 sec)300°C                                                                      |

#### PIN CONFIGURATION

## ORDER INFORMATION

| LEAD FREE FINISH | PART MARKING* | PACKAGE DESCRIPTION              | TEMPERATURE RANGE |

|------------------|---------------|----------------------------------|-------------------|

| LTC2757BCLX#PBF  | LTC2757LX     | 48-Lead (7mm × 7mm) Plastic LQFP | 0°C to 70°C       |

| LTC2757BILX#PBF  | LTC2757LX     | 48-Lead (7mm × 7mm) Plastic LQFP | -40°C to 85°C     |

| LTC2757ACLX#PBF  | LTC2757LX     | 48-Lead (7mm × 7mm) Plastic LQFP | 0°C to 70°C       |

| LTC2757AILX#PBF  | LTC2757LX     | 48-Lead (7mm × 7mm) Plastic LQFP | -40°C to 85°C     |

Consult LTC Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container. Consult LTC Marketing for information on non-standard lead based finish parts.

For more information on lead free part marking, go to: http://www.linear.com/leadfree/

This product is only offered in trays. For more information go to: http://www.linear.com/packaging/

# **ELECTRICAL CHARACTERISTICS** $V_{DD} = 5V$ , $V(R_{IN}) = 5V$ unless otherwise specified. The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25$ °C.

| ·                 |                                      |                                                               | LTC2757B |     |       | LTC2757A   |     |               |            |        |

|-------------------|--------------------------------------|---------------------------------------------------------------|----------|-----|-------|------------|-----|---------------|------------|--------|

| SYMBOL            | PARAMETER                            | CONDITIONS                                                    |          | MIN | TYP   | MAX        | MIN | TYP           | MAX        | UNITS  |

| Static Per        | formance                             |                                                               |          | ,   |       |            |     |               |            |        |

|                   | Resolution                           |                                                               | •        | 18  |       |            | 18  |               |            | Bits   |

|                   | Monotonicity                         |                                                               | •        | 18  |       |            | 18  |               |            | Bits   |

| DNL               | Differential Nonlinearity            |                                                               | •        |     |       | ±1         |     | ±0.4          | ±1         | LSB    |

| INL               | Integral Nonlinearity                |                                                               | •        |     |       | ±2         |     | ±0.4          | ±1         | LSB    |

| GE                | Gain Error                           | GE <sub>ADJ</sub> : OV, All Output Ranges                     | •        |     |       | ±48        |     | ±5            | ±32        | LSB    |

| GE <sub>TC</sub>  | Gain Error Temperature Coefficient   | (Note 3)                                                      |          |     | ±0.25 |            |     | ±0.25         |            | ppm/°C |

| BZE               | Bipolar Zero Error                   | All Bipolar Ranges                                            | •        |     |       | ±36        |     | ±3            | ±24        | LSB    |

| BZS <sub>TC</sub> | Bipolar Zero Temperature Coefficient | (Note 3)                                                      |          |     | ±0.15 |            |     | ±0.15         |            | ppm/°C |

| PSR               | Power Supply Rejection               | V <sub>DD</sub> = 5V, ±10%<br>V <sub>DD</sub> = 3V, ±10%      | •        |     |       | ±1.6<br>±4 |     | ±0.15<br>±0.4 | ±0.8<br>±2 | LSB/V  |

| I <sub>LKG</sub>  | I <sub>OUT1</sub> Leakage Current    | T <sub>A</sub> = 25°C<br>T <sub>MIN</sub> to T <sub>MAX</sub> | •        |     | ±0.05 | ±2<br>±5   |     | ±0.05         | ±2<br>±5   | nA     |

# $V_{DD} = 5V$ , $V(R_{IN}) = 5V$ unless otherwise specified. The ullet denotes specifications that apply over the full operating temperature range, otherwise specifications are at $T_A = 25$ °C.

| SYMBOL              | PARAMETER                        | CONDITIONS                                                     |   | MIN  | TYP      | MAX | UNITS        |

|---------------------|----------------------------------|----------------------------------------------------------------|---|------|----------|-----|--------------|

| Analog Pi           | 18                               |                                                                |   |      |          |     |              |

| R1, R2              | Reference Inverting Resistors    | (Note 4)                                                       | • | 16   | 20       |     | kΩ           |

| R <sub>REF</sub>    | DAC Input Resistance             | (Note 5)                                                       | • | 8    | 10       |     | kΩ           |

| R <sub>FB</sub>     | Feedback Resistor                | (Note 6)                                                       | • | 8    | 10       |     | kΩ           |

| R <sub>OFS</sub>    | Bipolar Offset Resistor          | (Note 6)                                                       | • | 16   | 20       |     | kΩ           |

| R <sub>VOSADJ</sub> | Offset Adjust Resistor           |                                                                | • | 1024 | 1280     |     | kΩ           |

| R <sub>GEADJ</sub>  | Gain Adjust Resistor             |                                                                | • | 2048 | 2560     |     | kΩ           |

| C <sub>IOUT1</sub>  | Output Capacitance               | Full-Scale<br>Zero-Scale                                       |   |      | 90<br>40 |     | pF<br>pF     |

| Dynamic F           | Performance                      |                                                                |   |      |          |     |              |

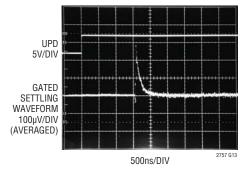

|                     | Output Settling Time             | Span Code = 000, 10V Step (Note 7)<br>To ±0.0004% FS           |   |      | 2.1      |     | μѕ           |

|                     | Glitch Impulse                   | V <sub>DD</sub> = 5V (Note 8)<br>V <sub>DD</sub> = 3V (Note 8) |   |      | 3<br>1.4 |     | nV•s<br>nV•s |

|                     | Digital-to-Analog Glitch Impulse | V <sub>DD</sub> = 5V (Note 9)<br>V <sub>DD</sub> = 3V (Note 9) |   |      | 4<br>1.8 |     | nV•s<br>nV•s |

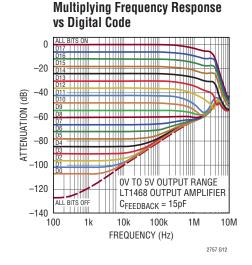

|                     | Reference Multiplying Bandwidth  | 0V to 5V Range, Code = Full-Scale, -3dB Bandwidth              |   |      | 1        |     | MHz          |

|                     | Multiplying Feedthrough Error    | 0V to 5V Range, V <sub>REF</sub> = ±10V, 10kHz Sine Wave       |   |      | 0.4      |     | mV           |

| THD                 | Total Harmonic Distortion        | (Note 10) Multiplying                                          |   |      | -110     |     | dB           |

|                     | Output Noise Voltage Density     | (Note 11) at I <sub>OUT1</sub>                                 |   |      | 13       |     | nV/√Hz       |

# **ELECTRICAL CHARACTERISTICS** $V_{DD} = 5V$ , $V(R_{IN}) = 5V$ unless otherwise specified. The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25$ °C.

| SYMBOL          | PARAMETER                       | CONDITIONS                                                                           |   | MIN                   | TYP | MAX        | UNITS |

|-----------------|---------------------------------|--------------------------------------------------------------------------------------|---|-----------------------|-----|------------|-------|

| Power Sup       | pply                            |                                                                                      |   |                       |     |            |       |

| $V_{DD}$        | Supply Voltage                  |                                                                                      | • | 2.7                   |     | 5.5        | V     |

| $I_{DD}$        | Supply Current, V <sub>DD</sub> | Digital Inputs = 0V or V <sub>DD</sub>                                               | • |                       | 0.5 | 1          | μА    |

| Digital Inp     | outs                            |                                                                                      |   |                       |     |            |       |

| V <sub>IH</sub> | Digital Input High Voltage      | $\begin{array}{l} 3.3V \leq V_{DD} \leq 5.5V \\ 2.7V \leq V_{DD} < 3.3V \end{array}$ | • | 2.4<br>2              |     |            | V     |

| V <sub>IL</sub> | Digital Input Low Voltage       | $4.5V < V_{DD} \le 5.5V$<br>$2.7V \le V_{DD} \le 4.5V$                               | • |                       |     | 0.8<br>0.6 | V     |

|                 | Hysteresis Voltage              |                                                                                      |   |                       | 0.1 |            | V     |

| I <sub>IN</sub> | Digital Input Current           | V <sub>IN</sub> = GND to V <sub>DD</sub>                                             | • |                       |     | ±1         | μА    |

| C <sub>IN</sub> | Digital Input Capacitance       | V <sub>IN</sub> = 0V (Note 12)                                                       | • |                       |     | 6          | pF    |

| Digital Ou      | tputs                           |                                                                                      | • |                       |     |            |       |

| V <sub>OH</sub> | I <sub>OH</sub> = 200μA         |                                                                                      | • | V <sub>DD</sub> - 0.4 |     |            | V     |

| $V_{0L}$        | I <sub>OL</sub> = 200μA         |                                                                                      | • |                       |     | 0.4        | V     |

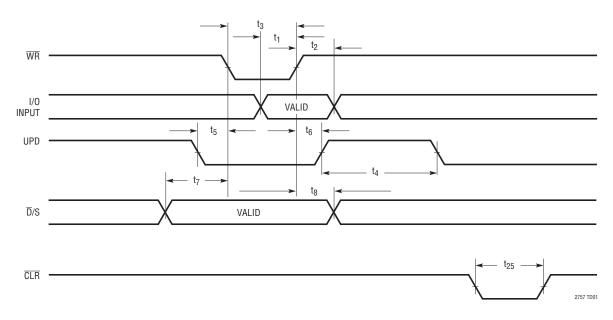

# **TIMING CHARACTERISTICS** $V_{DD} = 5V$ , $V(R_{IN}) = 5V$ unless otherwise specified. The $\bullet$ denotes specifications that apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ .

| SYMBOL           | PARAMETER                                 | CONDITIONS            |   | MIN | TYP | MAX | UNITS |

|------------------|-------------------------------------------|-----------------------|---|-----|-----|-----|-------|

| $V_{DD} = 4.5V$  | to 5.5V                                   |                       |   | ,   |     |     |       |

| Write and l      | Jpdate Timing                             |                       |   |     |     |     |       |

| t <sub>1</sub>   | I/O Valid to WR Rising Edge Set-Up        |                       | • | 9   |     |     | ns    |

| $\overline{t_2}$ | I/O Valid to WR Rising Edge Hold          |                       | • | 9   |     |     | ns    |

| t <sub>3</sub>   | WR Pulse Width                            |                       | • | 20  |     |     | ns    |

| t <sub>4</sub>   | UPD Pulse Width                           |                       | • | 20  |     |     | ns    |

| t <sub>5</sub>   | UPD Falling Edge to WR Falling Edge       | No Data Shoot-Through | • | 0   |     |     | ns    |

| t <sub>6</sub>   | WR Rising Edge to UPD Rising Edge         | (Note 12)             | • | 0   |     |     | ns    |

| t <sub>7</sub>   | D/S Valid to WR Falling Edge Set-Up Time  |                       | • | 9   |     |     | ns    |

| t <sub>8</sub>   | WR Rising Edge to D/S Valid Hold Time     |                       | • | 9   |     |     | ns    |

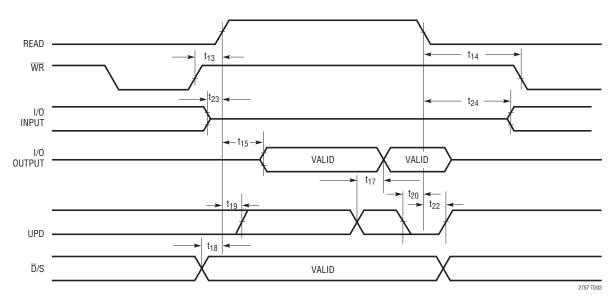

| Readback 1       | - Timing                                  |                       | ' |     |     |     |       |

| t <sub>13</sub>  | WR Rising Edge to READ Rising Edge        |                       | • | 9   |     |     | ns    |

| t <sub>14</sub>  | READ Falling Edge to WR Falling Edge      | (Note 12)             | • | 20  |     |     | ns    |

| t <sub>15</sub>  | READ Rising Edge to I/O Propagation Delay | C <sub>L</sub> = 10pF | • |     |     | 30  | ns    |

| t <sub>17</sub>  | UPD Valid to I/O Propagation Delay        | C <sub>L</sub> = 10pF | • |     |     | 30  | ns    |

| t <sub>18</sub>  | D/S Valid to READ Rising Edge             | (Note 12)             | • | 9   |     |     | ns    |

| t <sub>19</sub>  | READ Rising Edge to UPD Rising Edge       | No Update             | • | 9   |     |     | ns    |

| t <sub>20</sub>  | UPD Falling Edge to READ Falling Edge     | No Update             | • | 9   |     |     | ns    |

| t <sub>22</sub>  | READ Falling Edge to UPD Rising Edge      | (Note 12)             | • | 9   |     |     | ns    |

| t <sub>23</sub>  | I/O Bus Hi-Z to READ Rising Edge          | (Note 12)             | • | 0   |     |     | ns    |

| t <sub>24</sub>  | READ Falling Edge to I/O Bus Active       | (Note 12)             | • | 20  |     |     | ns    |

|                  | ,                                         | -                     |   |     |     |     | 2757f |

4

**TIMING CHARACTERISTICS**  $V_{DD} = 5V$ ,  $V(R_{IN}) = 5V$  unless otherwise specified. The  $\bullet$  denotes specifications that apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ .

| SYMBOL           | PARAMETER                                 | CONDITIONS            |   | MIN | TYP | MAX | UNITS |

|------------------|-------------------------------------------|-----------------------|---|-----|-----|-----|-------|

| CLR Timing       | J                                         | -                     |   |     |     |     |       |

| t <sub>25</sub>  | CLR Pulse Width Low                       |                       | • | 20  |     |     | ns    |

| $V_{DD} = 2.7V$  | to 3.3V                                   | -                     |   |     |     |     |       |

| Write and l      | Jpdate Timing                             |                       |   |     |     |     |       |

| t <sub>1</sub>   | I/O Valid to WR Rising Edge Set-Up        |                       | • | 18  |     |     | ns    |

| t <sub>2</sub>   | I/O Valid to WR Rising Edge Hold          |                       | • | 18  |     |     | ns    |

| t <sub>3</sub>   | WR Pulse Width                            |                       | • | 30  |     |     | ns    |

| $\overline{t_4}$ | UPD Pulse Width                           |                       | • | 30  |     |     | ns    |

| t <sub>5</sub>   | UPD Falling Edge to WR Falling Edge       | No Data Shoot-Through | • | 0   |     |     | ns    |

| t <sub>6</sub>   | WR Rising Edge to UPD Rising Edge         | (Note 12)             | • | 0   |     |     | ns    |

| t <sub>7</sub>   | D/S Valid to WR Falling Edge Set-Up Time  |                       | • | 18  |     |     | ns    |

| t <sub>8</sub>   | WR Rising Edge to D/S Valid Hold Time     |                       | • | 18  |     |     | ns    |

| Readback 1       |                                           | -                     |   |     |     |     |       |

| t <sub>13</sub>  | WR Rising Edge to Read Rising Edge        |                       | • | 18  |     |     | ns    |

| t <sub>14</sub>  | Read Falling Edge to WR Falling Edge      | (Note 12)             | • | 40  |     |     | ns    |

| t <sub>15</sub>  | Read Rising Edge to I/O Propagation Delay | C <sub>L</sub> = 10pF | • |     |     | 48  | ns    |

| t <sub>17</sub>  | UPD Valid to I/O Propagation Delay        | C <sub>L</sub> = 10pF | • |     |     | 48  | ns    |

| t <sub>18</sub>  | D/S Valid to Read Rising Edge             | (Note 12)             | • | 18  |     |     | ns    |

| t <sub>19</sub>  | Read Rising Edge to UPD Rising Edge       | No Update             | • | 9   |     |     | ns    |

| t <sub>20</sub>  | UPD Falling Edge to Read Falling Edge     | No Update             | • | 9   |     |     | ns    |

| t <sub>22</sub>  | READ Falling Edge to UPD Rising Edge      | (Note 12)             | • | 18  |     |     | ns    |

| t <sub>23</sub>  | I/O Bus Hi-Z to Read Rising Edge          | (Note 12)             | • | 0   |     |     | ns    |

| t <sub>24</sub>  | Read Falling Edge to I/O Bus Active       | (Note 12)             | • | 40  | -   |     | ns    |

| CLR Timing       | ı                                         |                       |   |     |     |     |       |

| t <sub>25</sub>  | CLR Pulse Width Low                       |                       | • | 30  |     |     | ns    |

|                  |                                           |                       |   |     |     |     |       |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** Continuous operation above the specified maximum operating junction temperature may impair device reliability.

**Note 3:** Temperature Coefficient is calculated by dividing the maximum change in the parameter by the specified temperature range.

Note 4: R1 is measured from  $R_{\mbox{\scriptsize IN}}$  to  $R_{\mbox{\scriptsize COM}};$  R2 is measured from REF to  $R_{\mbox{\scriptsize COM}}$

**Note 5:** Parallel combination of the resistances from REF to  $I_{OUT1}$  and from REF to  $I_{OUT2}$ . DAC input resistance is independent of code.

**Note 6**: Because of the proprietary SoftSpan switching architecture, the measured resistance looking into each of the specified pins is constant for all output ranges if the  $I_{OUT1}$  and  $I_{OUT2}$  pins are held at ground.

**Note 7:** Using LT1468 with  $C_{FEEDBACK} = 27pF$ . A  $\pm 0.0004\%$  settling time of 1.8 $\mu$ s can be achieved by optimizing the time constant on an individual basis. See Application Note 120, 1ppm Settling Time Measurement for a Monolithic 18-Bit DAC.

**Note 8:** Measured at the major carry transition, 0V to 5V range. Output amplifier: LT1468;  $C_{FB} = 50 pE$

**Note 9:** Zero-code to full-code transition; REF = 0V. Falling transition is similar or better.

**Note 10:** REF =  $6V_{RMS}$  at 1kHz. 0V to 5V range. DAC code = FS. Output amplifier = LT1468.

**Note 11:** Calculation from  $V_n = \sqrt{4kTRB}$ , where k = 1.38E-23 J/°K (Boltzmann constant), R = resistance ( $\Omega$ ), T = temperature (°K), and B = bandwidth (Hz).

Note 12: Guaranteed by design. Not production tested.

#### TYPICAL PERFORMANCE CHARACTERISTICS

$V_{DD} = 5V$ ,  $V(R_{IN}) = 5V$ ,  $T_A = 25$ °C, unless otherwise noted.

2

$V(R_{\mathsf{IN}}) \ (V)$

4 6 8 10

2757 G08

LINEAR

6 8

-2 0 2 4

$V(R_{IN})$  (V)

-10 -8 -6

2757f

2757 G09

-16

-40

-20

20

TEMPERATURE (°C)

40

60

8085

2757 G07

-10 -8 -6

-4 -2 0

#### TYPICAL PERFORMANCE CHARACTERISTICS

$V_{DD} = 5V$ ,  $V(R_{IN}) = 5V$ ,  $T_A = 25$ °C, unless otherwise noted.

#### **Settling Full-Scale Step**

$\begin{array}{l} LT1468 \ AMP; \ C_{FEEDBACK} = 20 pF \\ OV \ TO \ 10V \ STEP \\ V_{REF} = -10V; \ SPAN \ CODE = 000 \\ t_{SETTLE} = 1.8 \mu s \ to \ 0.0004\% \ (18 \ BITS) \end{array}$

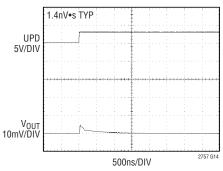

#### Mid-Scale Glitch ( $V_{DD} = 3V$ )

OV TO 5V RANGE LT1468 OUTPUT AMPLIFIER C<sub>FEEDBACK</sub> = 50pF RISING MAJOR CARRY TRANSITION. FALLING TRANSITION IS SIMILAR OR BETTER.

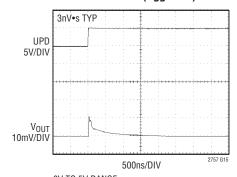

#### Mid-Scale Glitch $(V_{DD} = 5V)$

0V TO 5V RANGE LT1468 OUTPUT AMPLIFIER CFEEDBACK = 50pF RISING MAJOR CARRY TRANSITION. FALLING TRANSITION IS SIMILAR OR BETTER.

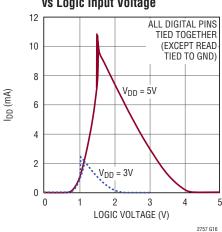

## Supply Current vs Logic Input Voltage

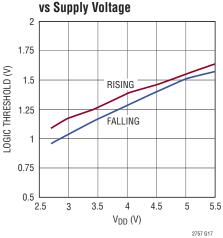

## Logic Threshold

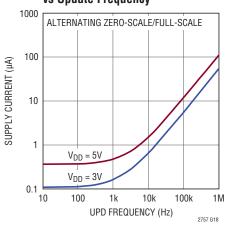

# Supply Current vs Update Frequency

#### PIN FUNCTIONS

$R_{IN}$  (Pins 1, 2): Input Resistor for External Reference Inverting Amplifier. Normally tied to the external reference voltage. Typically 5V; accepts up to  $\pm 15$ V. These pins are internally shorted together.

**S2 (Pin 3):** Span I/O Bit 2. Pins S0, S1 and S2 are used to program and to read back the output range of the DAC. See Table 2.

**GND** (Pins 4, 7, 18, 19): Ground. Tie to ground.

**I<sub>OUT2S</sub>**, **I<sub>OUT2F</sub>** (**Pins 5, 6**): DAC Output Current Complement Sense and Force Pins. Tie to ground via a clean, low-impedance path. These pins may also be used with a precision ground buffer amp as a Kelvin sensing pair (see the Typical Applications section).

**D17-D9 (Pins 8-16):** DAC Input/Output Data Bits. These I/O pins set and read back the DAC code. D17 (Pin 8) is the MSB.

**V<sub>DD</sub>** (**Pin 17**): Positive Supply Input.  $2.7V \le V_{DD} \le 5.5V$ . Requires a  $0.1\mu F$  bypass capacitor to GND.

**CLR** (**Pin 20**): Asynchronous Clear Input. When  $\overline{\text{CLR}}$  is asserted low, the DAC output resets to  $V_{OUT} = 0V$ . The LTC2757 selects the appropriate reset code according to the active output range—zero-scale for 0V to 5V and 0V to 10V spans, half scale for ±2.5V, ±5V and ±10V spans, or quarter scale for -2.5V to 7.5V span.

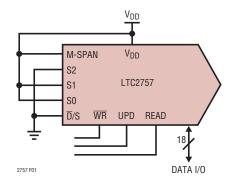

**M-SPAN (Pin 21):** Manual Span Control Input. M-SPAN can be pin-strapped to configure the LTC2757 for operation in a single, fixed output range.

To configure the part for single-span use, tie M-SPAN directly to  $V_{DD}$ . The output range is then set via hardware pin strapping; and the Span I/O port ignores Write, Update and Read commands.

If M-SPAN is instead connected to ground (SoftSpan configuration), the output ranges are set and verified by using Write, Update and Read operations. See *Manual Span Configuration* in the Operation section. M-SPAN must be connected either directly to GND (for SoftSpan operation) or  $V_{DD}$  (for single-span operation).

**DNC (Pins 22, 32):** Do Not Connect.

**D8-D0 (Pins 23-31):** DAC Input/Output Data Bits. These I/O pins set and read back the DAC code. D0 is the LSB.

$\overline{D}/S$  (Pin 33): Data/Span Select Input. This pin is used to select activation of the Data ( $\overline{D}/S = 0$ ) or Span ( $\overline{D}/S = 1$ ) Input I/O pins (D0 to D17 or S0 to S2, respectively), along with their respective dedicated registers, for Write or Read operations. Update operations are unaffected by  $\overline{D}/S$ , since all updates affect both Data and Span registers. For single-span operation, tie  $\overline{D}/S$  to GND.

**READ (Pin 34):** Read Input. When READ is asserted high, the Data I/O pins (D0-D17) or Span I/O pins (S0-S2) output the contents of a selected Input or DAC register (see Table 1). Data/Span ports are selected for readback with the  $\overline{D}/S$  pin; the Input/DAC registers within those ports are selected for readback with the UPD pin. The readback function of the Span I/O pins is disabled when M-SPAN is tied to  $V_{DD}$ .

**UPD (Pin 35):** Update/Register Select Input.

READ = low: Update function. When UPD is asserted high, the contents of the Input registers are copied into their respective DAC registers. The output of the DAC is updated, reflecting the new DAC register values.

READ = high: Register selector function. The Update function is disabled and the UPD pin functions as a register selector. UPD = low selects Input registers for readback, high selects DAC registers. See *Readback* in the Operation section.

WR (Pin 36): Active-Low Write Input. A Write operation copies the data present on the Data or Span I/O pins (D0-D17 or S0-S2, respectively) into the Input register. The Write function is disabled when READ is high.

**S0 (Pin 37):** Span I/O Bit 0. Pins S0, S1 and S2 are used to program and to read back the output range of the DAC. See Table 2.

**S1 (Pin 38):** Span I/O Bit 1. Pins S0, S1 and S2 are used to program and to read back the output range of the DAC. See Table 2.

LINEAR TECHNOLOGY

#### PIN FUNCTIONS

**V**<sub>OSADJ</sub> (**Pin 39**): DAC Offset Adjust Pin. This voltage-control pin can be used to null unipolar offset or bipolar zero error. The offset change expressed in LSB is the same for any output range. See *System Offset and Gain Adjustments* in the Operation section. Tie to ground if not used.

**I<sub>OUT1</sub> (Pin 40):** DAC current output; normally tied to the negative input (summing junction) of the I/V converter amplifier.

$R_{FB}$  (Pins 41, 42): DAC Feedback Resistor. Normally tied to the output of the I/V converter amplifier. The DAC output current from  $I_{OUT1}$  flows through the feedback resistor to the  $R_{FB}$  pins. These pins are internally shorted together.

$R_{OFS}$  (Pins 43, 44): Bipolar Offset Network. These pins provide the translation of the output voltage range for bipolar spans. Accepts up to  $\pm 15$ V; normally tied to the positive reference voltage. These pins are internally shorted together.

**REF (Pins 45, 46):** Feedback Resistor for the Reference Inverting Amplifier, and Reference Input for the DAC. Normally tied to the output of the reference inverting amplifier. Typically –5V; accepts up to ±15V. These pins are internally shorted together.

**R<sub>COM</sub>** (**Pin 47**): Center Tap Point of R<sub>IN</sub> and REF. Normally tied to the negative input of the external reference inverting amplifier.

**GE**<sub>ADJ</sub> (**Pin 48**): Gain Adjust Pin. This voltage-control pin can be used to null gain error or to compensate for reference errors. The gain error change expressed in LSB is the same for any output range. See *System Offset and Gain Adjustments* in the Operation section. Tie to ground if not used.

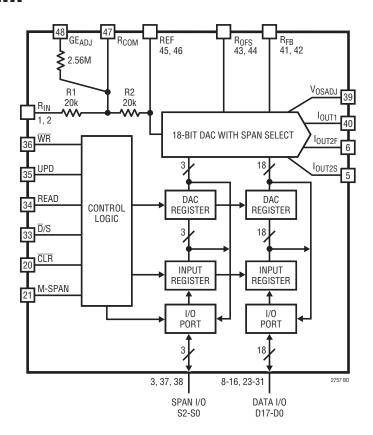

#### **BLOCK DIAGRAM**

## **TIMING DIAGRAMS**

#### Write, Update and Clear Timing

#### **Readback Timing**

#### **OPERATION**

#### **Output Ranges**

The LTC2757 is a current-output, parallel-input precision multiplying DAC offering  $\pm 1$ LSB INL and DNL over six software-selectable output ranges. Ranges can either be programmed in software for maximum flexibility or hardwired through pin-strapping. Two unipolar ranges are available (0V to 5V and 0V to 10V), and four bipolar ranges ( $\pm 2.5$ V,  $\pm 5$ V,  $\pm 10$ V and -2.5V to 7.5V). These ranges are obtained when an external precision 5V reference is used. The output ranges for other reference voltages are easy to calculate by observing that each range is a multiple of the external reference voltage. The ranges can then be expressed: 0 to 1×, 0 to 2×,  $\pm 0.5$ ×,  $\pm 1$ ×,  $\pm 2$ ×, and -0.5× to 1.5×.

#### **Digital Section**

The LTC2757 has four internal interface registers (see Block Diagram). Two of these—one Input and one DAC register—are dedicated to the Data I/O port, and two to the Span I/O port. Each port is thus double buffered. Double buffering provides the capability to simultaneously update the Span and Code registers, which allows smooth voltage transitions when changing output ranges. It also permits the simultaneous updating of multiple DACs or other parts on the data bus.

#### Write and Update Operations

Load the data input register directly from an 18-bit bus by holding the  $\overline{D}/S$  pin low and then pulsing the  $\overline{WR}$  pin low (Write operation).

Load the Span Input register by holding the  $\overline{D}/S$  pin high and then pulsing the  $\overline{WR}$  pin low (Write operation). The Span and Data register structures are the same except for the number of parallel bits—the Span registers have three bits, while the Data registers have 18 bits.

The DAC registers are loaded by pulsing the UPD pin high (Update operation), which copies the data held in the Input registers of both ports into the DAC registers. Note that Update operations always include both Data and Span registers; but the DAC register values will not change unless the Input register values have previously been changed by a Write operation.

To make both registers transparent for flowthrough mode, tie  $\overline{WR}$  low and UPD high. However, this defeats the deglitcher operation and output glitch impulse may increase. The deglitcher is activated on the rising edge of the UPD pin.

The interface also allows the use of the Input and DAC registers in a master-slave, or edge-triggered, configuration. This mode of operation occurs when  $\overline{WR}$  and UPD are tied together and driven by a single clock signal. The data bits are loaded into the Input register on the falling edge of the clock and then loaded into the DAC register on the rising edge.

It is possible to control both ports on one 18-bit wide data bus by allowing Span pins S2 to S0 to share bus lines with the Data LSBs (D2 to D0). No Write or Read operation acts on both span and data, so there cannot be a signal conflict.

The asynchronous clear pin ( $\overline{\text{CLR}}$ ) resets the LTC2757 to OV (zero-, half- or quarter-scale code) in any output range.  $\overline{\text{CLR}}$  resets both the Input and DAC data registers, but leaves the Span registers unchanged.

The device also has a power-on reset that initializes the DAC to  $V_{OUT} = 0V$  in any output range. The DAC powers up in the 0V to 5V range at zero-scale if the part is in SoftSpan configuration. For manual span (M-SPAN tied to  $V_{DD}$ ; see *Manual Span Configuration*), the DACs power-up in the manually-chosen range at the appropriate code.

#### Manual Span Configuration

Multiple output ranges are not needed in some applications. To configure the LTC2757 for single-span operation, tie the M-SPAN pin to  $V_{DD}$  and the  $\overline{D}/S$  pin to GND. The desired output range is programmed by tying S0, S1 and S2 to GND or  $V_{DD}$  (see Figure 1 and Table 2). In this configuration, no range-setting software routine is needed; the part will initialize to the chosen output range at power-up, with  $V_{OUT} = 0V$ .

When configured for manual span operation, Span port readback is disabled.

#### **OPERATION**

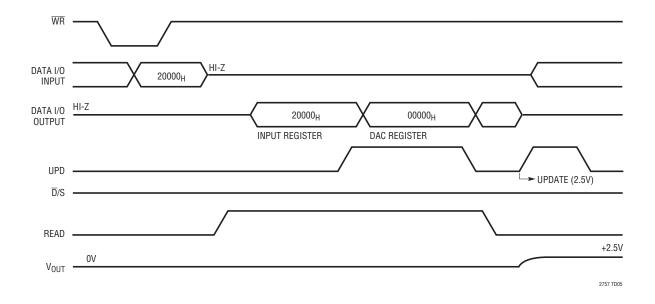

#### Readback

The contents of any one of the four interface registers can be read back from the I/O ports by using the READ pin in conjunction with the  $\overline{D}/S$  and UPD pins.

The I/O pins and registers are grouped into two ports—Data and Span. The Data I/O port consists of pins D0-D17, and the Span I/O port consists of pins S0, S1 and S2.

Each I/O port has one dedicated Input register and one dedicated DAC register. The register structure is shown in the Block Diagram.

A Readback operation is initiated by asserting READ to logic high after selecting the desired I/O port.

Select the I/O port (Data or Span) to be read back with the  $\overline{D}/S$  pin. The selected I/O port's pins become logic outputs during readback, while the unselected I/O port's pins remain high-impedance digital inputs.

With the I/O port selected, assert READ high and select the desired Input or DAC register using the UPD pin. Note that UPD is a two function pin—the Update function is only available when READ is low. If READ is high, the Update function is disabled and the UPD pin instead functions as a register selector, selecting an Input or DAC register for readback. Table 1 shows the readback functions for the LTC2757.

Table 1. Write, Update and Read Functions

| READ | D/S | WR | UPD | SPAN I/O                      | DATA I/O                      |

|------|-----|----|-----|-------------------------------|-------------------------------|

| 0    | 0   | 0  | 0   | -                             | Write to Input Register       |

| 0    | 0   | 0  | 1   | -                             | Write/Update<br>(Transparent) |

| 0    | 0   | 1  | 0   | -                             | -                             |

| 0    | 0   | 1  | 1   | Update DAC Register           | Update DAC Register           |

| 0    | 1   | 0  | 0   | Write to Input Register       | -                             |

| 0    | 1   | 0  | 1   | Write/Update<br>(Transparent) | -                             |

| 0    | 1   | 1  | 0   | -                             | -                             |

| 0    | 1   | 1  | 1   | Update DAC register           | Update DAC Register           |

| 1    | 0   | Χ  | 0   | -                             | Read Input Register           |

| 1    | 0   | Χ  | 1   | -                             | Read DAC Register             |

| 1    | 1   | Χ  | 0   | Read Input Register           | -                             |

| 1    | 1   | Χ  | 1   | Read DAC Register             | -                             |

X = Don't Care

The most common readback task is to check the contents of an Input register after writing to it, and before updating the new data to the DAC register. To do this, hold UPD low and assert READ high. The contents of the selected port's Input register are output to its I/O pins.

To read back the contents of a DAC register, hold UPD low and assert READ high, then bring UPD high to select the DAC register. The contents of the selected DAC register are output by the selected port's I/O pins. Note: if no update is desired after the readback operation, UPD must be returned low before bringing READ low, otherwise the UPD pin will revert to its primary function and update the DAC.

Table 2. Span Codes

| <b>S2</b> | <b>S1</b> | SO | SPAN                  |  |  |  |  |

|-----------|-----------|----|-----------------------|--|--|--|--|

| 0         | 0         | 0  | Unipolar 0V to 5V     |  |  |  |  |

| 0         | 0         | 1  | Unipolar 0V to 10V    |  |  |  |  |

| 0         | 1         | 0  | Bipolar –5V to 5V     |  |  |  |  |

| 0         | 1         | 1  | Bipolar –10V to 10V   |  |  |  |  |

| 1         | 0         | 0  | Bipolar –2.5V to 2.5V |  |  |  |  |

| 1         | 0         | 1  | Bipolar –2.5V to 7.5V |  |  |  |  |

Codes not shown are reserved and should not be used.

Figure 1. Configuring the LTC2757 for Single-Span Operation (±10V Range)

#### System Offset and Gain Adjustments

Many systems require compensation for overall system offset. This may be an order of magnitude or more greater than the offset of the LTC2757, which is so low as to be dominated by external output amplifier errors even when using the most precise op amps.

#### **OPERATION**

The offset adjust pin  $V_{OSADJ}$  can be used to null unipolar offset or bipolar zero error. The offset change expressed in LSB is the same for any output range:

$$\Delta V_{OS}[LSB] = \frac{-V(V_{OSADJ})}{V(R_{IN})} \cdot 2048$$

A 5V control voltage applied to  $V_{OSADJ}$  produces  $\Delta V_{OS}$  = -2048 LSB in any output range, assuming a 5V reference voltage at  $R_{IN}$ .

In voltage terms, the offset delta is attenuated by a factor of 32, 64 or 128, depending on the output range. (These functions hold regardless of reference voltage.)

$$\Delta V_{OS} = -(^{1}/_{128})V_{OSADJ}$$

[0V to 5V, ±2.5V spans]

$\Delta V_{OS} = -(^{1}/_{64})V_{OSADJ}$  [0V to 10V, ±5V, -2.5V to 7.5V spans]

$\Delta V_{OS} = -(^{1}/_{32})V_{OSADJ}$  [±10V span]

The gain error adjust pin GE<sub>ADJ</sub> can be used to null gain error or to compensate for reference errors. The gain error change expressed in LSB is the same for any output range:

$$\Delta GE = \frac{V(GE_{ADJ})}{V(R_{IN})} \bullet 2048$$

The gain-error delta is non-inverting for positive reference voltages.

Note that this pin compensates the gain by altering the inverted reference voltage V(REF). In voltage terms, the V(REF) delta is inverted and attenuated by a factor of 128.

$$\Delta V(REF) = -(^{1}/_{128})GE_{ADJ}$$

The nominal input range of these pins is ±5V; other voltages of up to ±15V may be used if needed. However, do not use voltages divided down from power supplies; reference-quality, low-noise inputs are required to maintain the best DAC performance.

The  $V_{OSADJ}$  pin has an input impedance of 1.28M $\Omega$ . This pin should be driven with a Thevenin-equivalent impedance of 10k or less to preserve the settling performance of the LTC2757. It should be shorted to GND if not used.

The  $GE_{ADJ}$  pin has an input impedance of 2.56M $\Omega$ , and is intended for use with fixed reference voltages only. It should be shorted to GND if not used.

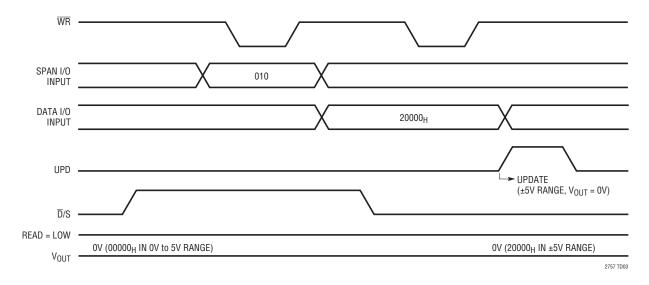

### **OPERATION—EXAMPLES**

1. Load ±5V range with the output at 0V. Note that since span and code are updated together, the output, if started at 0V, will stay there. The 18-bit DAC code is shown in hex for compactness.

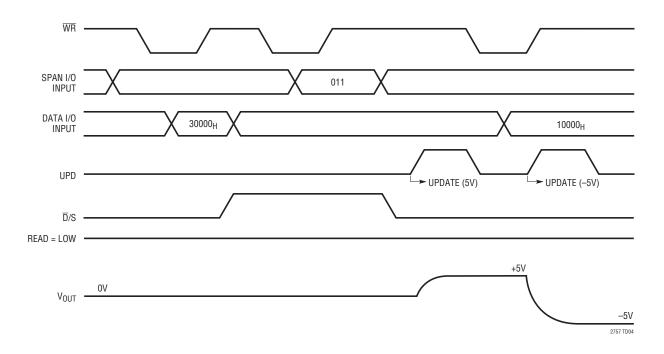

### **OPERATION—EXAMPLES**

2. Load ±10V range with the output at 5V, changing to -5V.

3. Write and update mid-scale code in 0V to 5V range ( $V_{OUT} = 2.5V$ ) using readback to check the contents of the input and DAC registers before updating.

#### APPLICATIONS INFORMATION

#### **Op Amp Selection**

Because of the extremely high accuracy of the 18-bit LTC2757, careful thought should be given to op amp selection in order to achieve the exceptional performance of which the part is capable. Fortunately, the sensitivity of INL and DNL to op amp offset has been greatly reduced compared to previous generations of multiplying DACs.

Tables 3 and 4 contain equations for evaluating the effects of op amp parameters on the LTC2757's accuracy. These are the changes the op amp can cause to the INL, DNL, unipolar offset, unipolar gain error, bipolar zero and bipolar gain error.

Table 3. Coefficients for the Equations of Table 4

| OUTPUT RANGE  | A1  | A2 | А3   | A4  | A5  |

|---------------|-----|----|------|-----|-----|

| 5V            | 1.1 | 2  | 1    |     | 1   |

| 10V           | 2.2 | 3  | 0.5  |     | 1.5 |

| ±5V           | 2   | 2  | 1    | 1   | 1.5 |

| ±10V          | 4   | 4  | 0.83 | 1   | 2.5 |

| ±2.5V         | 1   | 1  | 1.4  | 1   | 1   |

| -2.5V to 7.5V | 1.9 | 3  | 0.7  | 0.5 | 1.5 |

Table 4. Easy-to-Use Equations Determine Op Amp Effects on DAC Accuracy in All Output Ranges (Circuit of Page 1). Subscript 1 Refers to Output Amp, Subscript 2 Refers to Reference Inverting Amp.

| OP<br>AMP                   | INL (LSB)                                                   | DNL (LSB)                                                        | UNIPOLAR<br>Offset (LSB)                                                  | BIPOLAR ZERO ERROR<br>(LSB)                                               | UNIPOLAR GAIN<br>Error (LSB)                                    | BIPOLAR GAIN<br>Error (LSB)                                     |

|-----------------------------|-------------------------------------------------------------|------------------------------------------------------------------|---------------------------------------------------------------------------|---------------------------------------------------------------------------|-----------------------------------------------------------------|-----------------------------------------------------------------|

| V <sub>OS1</sub> (mV)       | $V_{0S1} \cdot 12.1 \cdot \left(\frac{5V}{V_{REF}}\right)$  | $V_{0S1} \bullet 3.1 \bullet \left(\frac{5V}{V_{REF}}\right)$    | $A3 \bullet V_{0S1} \bullet 52.4 \bullet \left(\frac{5V}{V_{REF}}\right)$ | $A3 \bullet V_{0S1} \bullet 78.6 \bullet \left(\frac{5V}{V_{REF}}\right)$ | V <sub>0S1</sub> •52.4• $\left(\frac{5V}{V_{REF}}\right)$       | $V_{0S1} \bullet 52.4 \bullet \left(\frac{5V}{V_{REF}}\right)$  |

| I <sub>B1</sub><br>(nA)     | $I_{B1} \cdot 0.0012 \cdot \left(\frac{5V}{V_{REF}}\right)$ | $I_{B1} \bullet 0.00032 \bullet \left(\frac{5V}{V_{REF}}\right)$ | $I_{B1} \bullet 0.524 \bullet \left(\frac{5V}{V_{REF}}\right)$            | $I_{B1} \bullet 0.524 \bullet \left(\frac{5V}{V_{REF}}\right)$            | $I_{B1} \bullet 0.0072 \bullet \left(\frac{5V}{V_{REF}}\right)$ | $I_{B1} \bullet 0.0072 \bullet \left(\frac{5V}{V_{REF}}\right)$ |

| A <sub>VOL1</sub><br>(V/mV) | $A1 \cdot \left(\frac{66}{A_{VOL1}}\right)$                 | $A2^{\bullet}\left(\frac{6}{A_{VOL1}}\right)$                    | 0                                                                         | 0                                                                         | $A5 \bullet \left(\frac{524}{A_{VOL1}}\right)$                  | $A5^{\bullet} \left( \frac{524}{A_{VOL1}} \right)$              |

| V <sub>OS2</sub> (mV)       | 0                                                           | 0                                                                | 0                                                                         | $A4 \bullet V_{0S2} \bullet 52.4 \bullet \left(\frac{5V}{V_{REF}}\right)$ | $V_{0S2} \bullet 104.8 \bullet \left(\frac{5V}{V_{REF}}\right)$ | $V_{0S2} \bullet 104.8 \bullet \left(\frac{5V}{V_{REF}}\right)$ |

| I <sub>B2</sub> (nA)        | 0                                                           | 0                                                                | 0                                                                         | $A4 \bullet I_{B2} \bullet 0.524 \bullet \left(\frac{5V}{V_{REF}}\right)$ | $I_{B2} \bullet 1.048 \bullet \left(\frac{5V}{V_{REF}}\right)$  | $I_{B2} \cdot 1.048 \cdot \left(\frac{5V}{V_{REF}}\right)$      |

| A <sub>VOL2</sub><br>(V/mV) | 0                                                           | 0                                                                | 0                                                                         | $A4 \bullet \left(\frac{262}{A_{VOL2}}\right)$                            | $\left(\frac{524}{A_{VOL2}}\right)$                             | $\left(\frac{524}{A_{VOL2}}\right)$                             |

#### APPLICATIONS INFORMATION

Table 5. Partial List of LTC Precision Amplifiers Recommended for Use with the LTC2757 with Relevant Specifications

|           |                       | AMPLIFIER SPECIFICATIONS |                          |                            |                            |                      |                                  |                                 |                            |  |  |  |  |  |

|-----------|-----------------------|--------------------------|--------------------------|----------------------------|----------------------------|----------------------|----------------------------------|---------------------------------|----------------------------|--|--|--|--|--|

| AMPLIFIER | V <sub>OS</sub><br>µV | I <sub>B</sub>           | A <sub>VOL</sub><br>V/mV | VOLTAGE<br>NOISE<br>nV/√Hz | CURRENT<br>NOISE<br>pA/√Hz | SLEW<br>RATE<br>V/µs | GAIN BANDWIDTH<br>PRODUCT<br>MHz | tsettling<br>with LTC2757<br>µs | POWER<br>DISSIPATION<br>mW |  |  |  |  |  |

| LTC1150   | 10                    | 0.05                     | 5600                     | 90                         | 0.0018                     | 3                    | 2.5                              | 10ms                            | 24                         |  |  |  |  |  |

| LT1001    | 25                    | 2                        | 800                      | 10                         | 0.12                       | 0.25                 | 0.8                              | 120                             | 46                         |  |  |  |  |  |

| LT1012    | 25                    | 0.1                      | 2000                     | 14                         | 0.02                       | 0.2                  | 1                                | 120                             | 11.4                       |  |  |  |  |  |

| LT1097    | 50                    | 0.35                     | 2500                     | 14                         | 0.008                      | 0.2                  | 0.7                              | 120                             | 11                         |  |  |  |  |  |

| LT1468    | 75                    | 10                       | 5000                     | 5                          | 0.6                        | 22                   | 90                               | 2.1                             | 117                        |  |  |  |  |  |

Table 5 contains a partial list of LTC precision op amps recommended for use with the LTC2757. The easy-to-use design equations simplify the selection of op amps to meet the system's specified error budget. Select the amplifier from Table 5 and insert the specified op amp parameters in Table 4. Add up all the errors for each category to determine the effect the op amp has on the accuracy of the part. Arithmetic summation gives an (unlikely) worst-case effect. A root-sum-square (RMS) summation produces a more realistic estimate.

Op amp offset contributes mostly to DAC output offset and gain error, and has minimal effect on INL and DNL. For example, consider the LTC2757 in unipolar 5V output range. (Note that for this example, the LSB size is  $19\mu V$ .) An op amp offset of  $35\mu V$  will cause 1.8LSB of output offset, and 1.8LSB of gain error; but 0.4LSB of INL, and just 0.1LSB of DNL.

While not directly addressed by the simple equations in Tables 3 and 4, temperature effects can be handled just as easily for unipolar and bipolar applications. First, consult an op amp's data sheet to find the worst-case  $V_{OS}$  and  $I_{B}$  over temperature. Then, plug these numbers in the  $V_{OS}$  and  $I_{B}$  equations from Table 4 and calculate the temperature-induced effects.

For applications where fast settling time is important, Application Note 120, *1ppm Settling Time Measurement for a Monolithic 18-Bit DAC*, offers a thorough discussion of 18-bit DAC settling time and op amp selection.

#### Recommendations

To achieve the full specified static and dynamic performance of the LTC2757, the LT1468 amplifier is recommended; it offers a unique combination of fast settling and excellent DC precision. When using the LT1468 as an output amp, however, the offset voltage (75 $\mu$ V max) must be nulled to avoid degrading the linearity of the LTC2757. The LT1468 datasheet shows how to do this with a digital potentiometer.

For DC or low-frequency applications, the LTC1150 is the simplest 18-bit accurate output amplifier. An auto-zero amp, its exceptionally low offset ( $10\mu V$  max) and offset drift ( $0.01\mu V$ /°C) make nulling unnecessary. Note: for swings above 8V, use an LT1010 buffer to boost the load current capability of the LTC1150. The settling of auto-zero amps is a special case; see Application Note 120, 1ppm Settling Time Measurement for a Monolithic 18-Bit DAC, Appendix E, for details.

The LT1012 and LT1001 are good intermediate output-amp solutions that achieve moderate speed and good accuracy. They are also excellent choices for the reference inverting amplifier in fixed-reference applications.

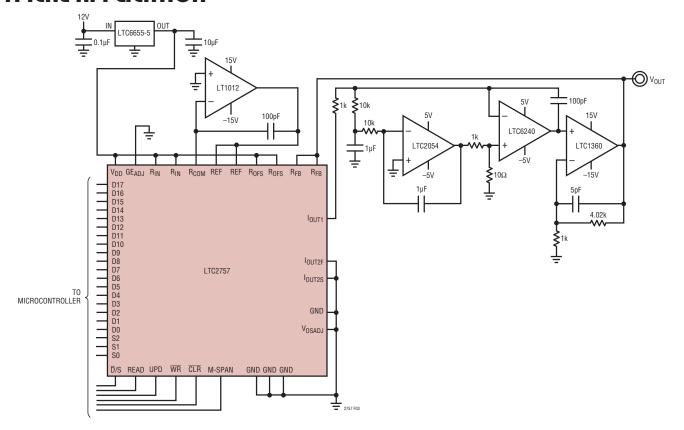

Figure 3 shows a composite output amplifier that achieves fast settling (8μs) and very low offset (3μV max) without offset nulling. This circuit offers high open-loop gain (1000V/mV min), low input bias current (0.15nA max), fast slew rate (25V/μs min), and a high gain-bandwidth product (30MHz typ). The high speed path consists of an LTC6240, which is an 18MHz ultra-low bias current amplifier, followed by an LT1360, a 50MHz fast-slewing amplifier which provides additional gain and the ability to

LINEAD

#### APPLICATIONS INFORMATION

swing to  $\pm 10V$  at the output. Compensation is taken from the output of the LTC6240, allowing the use of a much larger compensation capacitor than if taken after the gain-of-five stage. An LTC2054 auto-zero amplifier senses the voltage at  $I_{OUT1}$  and drives the non-inverting input of the LTC6240 to eliminate the offset of the high speed path. The 100:1 attenuator and input filter reduce the low frequency noise in this stage while maintaining low DC offset.

#### **Precision Voltage Reference Considerations**

Much in the same way selecting an operational amplifier for use with the LTC2757 is critical to the performance of the system, selecting a precision voltage reference also requires due diligence. The output voltage of the LTC2757 is directly affected by the voltage reference; thus, any voltage reference error will appear as a DAC output voltage error.

There are three primary error sources to consider when selecting a precision voltage reference for 18-bit applications: output voltage initial tolerance, output voltage temperature coefficient and output voltage noise.

Initial reference output voltage tolerance, if uncorrected, generates a full-scale error term. Choosing a reference with low output voltage initial tolerance, like the LT1236  $(\pm 0.05\%)$ , minimizes the gain error caused by the reference; however, a calibration sequence that corrects for system zero- and full-scale error is always recommended.

A reference's output voltage temperature coefficient affects not only the full-scale error, but can also affect the circuit's INL and DNL performance. If a reference is chosen with a loose output voltage temperature coefficient, then the DAC output voltage along its transfer characteristic will be very dependent on ambient conditions. Minimizing the error due to reference temperature coefficient can be achieved by choosing a precision reference with a low output voltage temperature coefficient and/or tightly controlling the ambient temperature of the circuit to minimize temperature gradients.

As precision DAC applications move to 18-bit performance, reference output voltage noise may contribute a dominant share of the system's noise floor. This in turn can degrade system dynamic range and signal-to-noise ratio. Care

should be exercised in selecting a voltage reference with as low an output noise voltage as practical for the system resolution desired. Precision voltage references like the LT1236 produce low output noise in the 0.1Hz to 10Hz region, well below the 18-bit LSB level in 5V or 10V full-scale systems. However, as the circuit bandwidths increase, filtering the output of the reference may be required to minimize output noise.

Table 6. Partial List of LTC Precision References Recommended for Use with the LTC2757 with Relevant Specifications

| REFERENCE   | INITIAL       | TEMPERATURE     | 0.1Hz to 10Hz         |

|-------------|---------------|-----------------|-----------------------|

|             | Tolerance     | DRIFT           | NOISE                 |

| LT1019A-5,  | ±0.05%        | 5ppm/°C         | 12μV <sub>P-P</sub>   |

| LT1019A-10  | Max           | Max             |                       |

| LT1236A-5,  | ±0.05%        | 5ppm/°C         | 3µV <sub>P-P</sub>    |

| LT1236A-10  | Max           | Max             |                       |

| LT1460A-5,  | ±0.075%       | 10ppm/°C        | 20μV <sub>P-P</sub>   |

| LT1460A-10  | Max           | Max             |                       |

| LT1790A-2.5 | ±0.05%<br>Max | 10ppm/°C<br>Max | 12μV <sub>P-P</sub>   |

| LTC6655-2.5 | ±0.025%       | 2ppm/°C         | 0.62µV <sub>P-P</sub> |

| LTC6655-5   | Max           | Max             |                       |

#### Grounding

As with any high-resolution converter, clean grounding is important. A low-impedance analog ground plane is necessary, as are star grounding techniques. Keep the board layer used for star ground continuous to minimize ground resistances; that is, use the star-ground concept without using separate star traces. The I<sub>OUT2</sub> pins are of particular concern; INL will be degraded by the code-dependent currents carried by the I<sub>OUT2F</sub> and I<sub>OUT2S</sub> pins if voltage drops to ground are allowed to develop. The best strategy here is to tie the pins to the star ground plane by multiple vias located directly underneath the part. Alternatively, the pins may be routed to the star ground point if necessary; join them together at the part and route a single trace of no more than 30 squares of 1oz copper.

In the rare case in which neither of these alternatives is practicable, a force/sense amplifier should be used as a ground buffer (see the Typical Applications section). Note, however, that the voltage offset of the ground buffer amp directly contributes to the effects on accuracy specified in Table 4 under ' $V_{OS1}$ '. The combined effects of the offsets can be calculated by substituting the total offset from  $I_{OUT1}$  to  $I_{OUT2S}$  for  $V_{OS1}$  in the equations.

## TYPICAL APPLICATIONS

Figure 2. Basic Connections for SoftSpan  $V_{OUT}$  DAC with Two Optional Circuits for Driving  $I_{OUT2}$  from GND with a Force/Sense Amplifier

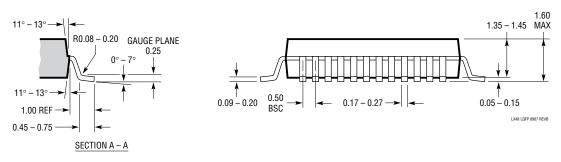

### PACKAGE DESCRIPTION

####

(Reference LTC DWG # 05-08-1760 Rev Ø)

RECOMMENDED SOLDER PAD LAYOUT APPLY SOLDER MASK TO AREAS THAT ARE NOT SOLDERED

#### NOTE:

- 1. PACKAGE DIMENSIONS CONFORM TO JEDEC #MS-026 PACKAGE OUTLINE

- 2. DIMENSIONS ARE IN MILLIMETERS

- 3. DIMENSIONS OF PACKAGE DO NOT INCLUDE MOLD FLASH. MOLD FLASH SHALL NOT EXCEED 0.25mm ON ANY SIDE, IF PRESENT

- 4. PIN-1 INDENTIFIER IS A MOLDED INDENTATION, 0.50mm DIAMETER 5. DRAWING IS NOT TO SCALE

### TYPICAL APPLICATION

Figure 3. Composite Amplifier Provides 18-Bit Precision and Fast Settling

## **RELATED PARTS**

| PART NUMBER         | DESCRIPTION                                                   | COMMENTS                                                                                      |  |

|---------------------|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------|--|

| LTC1591/<br>LTC1597 | Parallel 14-/16-Bit I <sub>OUT</sub> Single DAC               | Integrated 4-Quadrant Resistors                                                               |  |

| LTC1592             | Serial 16-Bit I <sub>OUT</sub> Single DAC                     | Software-Selectable (SoftSpan) Ranges, ±1LSB INL, DNL, 16-Lead SSOP Package                   |  |

| LTC1821             | Parallel 16-Bit V <sub>OUT</sub> Single DAC                   | ±1LSB INL, DNL, 0V to 10V, 0V to -10V, ±10V Output Ranges                                     |  |

| LTC2641/<br>LTC2642 | Serial 12-/14-/16-Bit Unbuffered V <sub>OUT</sub> Single DACs | ±1LSB INL, ±1LSB DNL, 1µs Settling, Tiny MSOP-10,<br>3mm × 3mm DFN-10 Packages                |  |

| LTC2704             | Serial 12-/14-/16-Bit V <sub>OUT</sub> SoftSpan Quad DACs     | Software-Selectable Ranges, Integrated Amplifiers                                             |  |

| LTC2751             | Parallel 12-/14-/16-Bit I <sub>OUT</sub> SoftSpan Single DAC  | ±1LSB INL, DNL, Software-Selectable Ranges, 5mm × 7mm QFN-38 Package                          |  |

| LTC2753             | Parallel 12-/14-/16-Bit I <sub>OUT</sub> SoftSpan Dual DACs   | ±1LSB INL, DNL, Software-Selectable Ranges, 7mm × 7mm QFN-48 Package                          |  |

| LTC2754             | Serial 12-/16-Bit I <sub>OUT</sub> SoftSpan Quad DACs         | ±1LSB INL, DNL, Software-Selectable Ranges, 7mm × 8mm QFN-52 Package                          |  |

| LTC2755             | Parallel 12-/14-/16-Bit I <sub>OUT</sub> SoftSpan Quad DACs   | ±1LSB INL, DNL, Software-Selectable Ranges, 9mm × 9mm QFN-64 Package                          |  |

| LT1027              | Precision Reference                                           | 1ppm/°C Maximum Drift                                                                         |  |

| LT1236A-5           | Precision Reference                                           | 0.05% Maximum Tolerance, 1ppm 0.1Hz to 10Hz Noise                                             |  |

| LTC1150             | ±15V Zero-Drift Op Amp                                        | 10μV Maximum Offset Voltage, 1.8μV <sub>P-P</sub> (0.1Hz to 10Hz) Noise, 0.8mA Supply Current |  |

| LT1468              | 16-Bit Accurate Op Amp                                        | 90MHz GBW, 22V/µs Slew Rate                                                                   |  |