# 6-Bit Programmable 2-/3-/4-Phase Synchronous Buck Controller

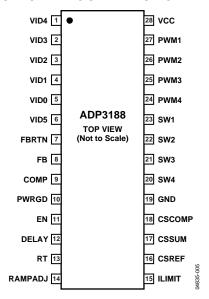

**ADP3188**

#### **FEATURES**

Selectable 2-, 3- or 4-phase operation at up to 1 MHz per phase

±9.5 mV worst-case differential sensing error over temperature

Logic-level PWM outputs for interface to external high power drivers

Active current balancing between all output phases

Built-in power good/crowbar blanking supports on-the-fly

VID code changes

6-bit digitally programmable 0.8375 V to 1.6 V output Programmable short-circuit protection with programmable latch-off delay

#### **APPLICATIONS**

Desktop PC power supplies for Next-generation Intel® processors VRM modules

#### **GENERAL DESCRIPTION**

The ADP3188 is a highly efficient, multiphase, synchronous buck switching regulator controller optimized for converting a 12 V main supply into the core supply voltage required by high performance Intel processors. The part uses an internal 6-bit DAC to read a voltage identification (VID) code directly from the processor, which is used to set the output voltage between 0.8375 V and 1.6 V. It uses a multimode PWM architecture to drive the logic-level outputs at a programmable switching frequency that can be optimized for VR size and efficiency. The phase relationship of the output signals can be programmed to provide 2-, 3-, or 4-phase operation, allowing the construction of up to four complementary buck switching stages.

The ADP3188 also includes programmable no-load offset and slope functions to adjust the output voltage as a function of the load current, so it is always optimally positioned for a system transient. The ADP3188 also provides accurate and reliable short-circuit protection, adjustable current limiting, and a delayed power good output that accommodates on-the-fly output voltage changes requested by the CPU.

The ADP3188 is specified over the commercial temperature range of 0°C to 85°C and is available in 28-lead, TSSOP and QSOP packages.

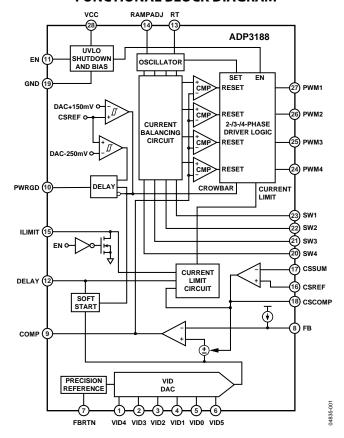

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

#### Rev. A

## **TABLE OF CONTENTS**

| Specifications                                            | Inductor Selection                                            | 15 |

|-----------------------------------------------------------|---------------------------------------------------------------|----|

| Test Circuits                                             | Designing an Inductor                                         | 16 |

| Absolute Maximum Ratings6                                 | Selecting a Standard Inductor                                 | 16 |

| ESD Caution                                               | Output Droop Resistance                                       | 16 |

| Pin Configuration and Function DescriptionS7              | Inductor DCR Temperature Correction                           | 17 |

| Typical Performance Characteristics                       | Output Offset                                                 | 17 |

| Theory of Operation9                                      | C <sub>OUT</sub> Selection                                    | 18 |

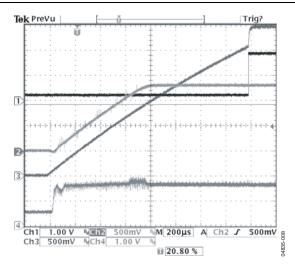

| Start-Up Sequence9                                        | Power MOSFETs                                                 | 18 |

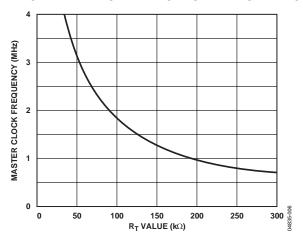

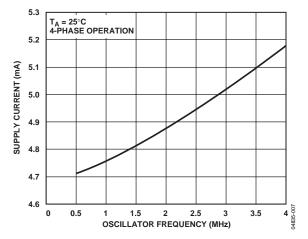

| Master Clock Frequency9                                   | Ramp Resistor Selection                                       | 20 |

| Output Voltage Differential Sensing9                      | COMP Pin Ramp                                                 | 20 |

| Output Current Sensing9                                   | Current-Limit Setpoint                                        | 20 |

| Active Impedance Control Mode10                           | Feedback Loop Compensation Design                             | 20 |

| Current-Control Mode and Thermal Balance10                | $C_{\mathrm{IN}}$ Selection and Input Current di/dt Reduction | 22 |

| Voltage Control Mode10                                    | Tuning the ADP3188                                            | 23 |

| Soft Start                                                | DC Loadline Setting                                           | 23 |

| Current-Limit, Short-Circuit, and Latch-Off Protection 11 | AC Loadline Setting                                           | 24 |

| Dynamic VID11                                             | Layout and Component Placement                                | 26 |

| Power Good Monitoring                                     | General Recommendations                                       | 26 |

| Output Crowbar                                            | Power Circuitry Recommendations                               | 26 |

| Output Enable and UVLO                                    | Signal Circuitry Recommendations                              | 26 |

| Application Information                                   | Outline Dimensions                                            | 27 |

| Setting the Clock Frequency15                             | Ordering Guide                                                | 27 |

| Soft Start and Current-Limit Latch-Off Delay Times 15     |                                                               |    |

|                                                           |                                                               |    |

|                                                           |                                                               |    |

#### **REVISION HISTORY**

4/05—Rev. 0 to Rev. A

| Changes to Figure 10      | 14 |

|---------------------------|----|

| Changes to Ordering Guide | 27 |

4/04—Revision 0: Initial Version

# **SPECIFICATIONS**

VCC = 12 V, FBRTN = GND,  $T_A = 0$ °C to 85°C, unless otherwise noted.<sup>1</sup>

Table 1.

| Parameter                                            | Symbol                                                     | Conditions                                                                          | Min                                        | Тур  | Max  | Unit    |

|------------------------------------------------------|------------------------------------------------------------|-------------------------------------------------------------------------------------|--------------------------------------------|------|------|---------|

| ERROR AMPLIFIER                                      |                                                            |                                                                                     |                                            |      |      |         |

| Output Voltage Range <sup>2</sup>                    | V <sub>COMP</sub>                                          |                                                                                     | 0.7                                        |      | 3.1  | V       |

| Accuracy                                             | V <sub>FB</sub>                                            | Relative to nominal DAC output,<br>referenced to FBRTN,<br>CSSUM = CSCOMP, Figure 2 | -9.5                                       |      | +9.5 | mV      |

| Line Regulation                                      | $\Delta V_{FB}$                                            | VCC = 10 V to 14 V                                                                  |                                            | 0.05 |      | %       |

| Input Bias Current                                   | I <sub>FB</sub>                                            |                                                                                     | 14                                         | 15.5 | 17   | μA      |

| FBRTN Current                                        | I <sub>FBRTN</sub>                                         |                                                                                     |                                            | 100  | 140  | μA      |

| Output Current                                       | I <sub>O(ERR)</sub> FB forced to V <sub>OUT</sub> – 3% 500 |                                                                                     | μA                                         |      |      |         |

| Gain Bandwidth Product                               | GBW <sub>(ERR)</sub>                                       | COMP = FB                                                                           |                                            | 20   |      | MHz     |

| Slew Rate                                            | , ,                                                        | $C_{COMP} = 10 \text{ pF}$                                                          |                                            | 25   |      | V/µs    |

| VID INPUTS                                           |                                                            |                                                                                     |                                            |      |      | ., ,,,, |

| Input Low Voltage                                    | V <sub>IL(VID)</sub>                                       |                                                                                     |                                            |      | 0.4  | V       |

| Input High Voltage                                   | V <sub>IH(VID)</sub>                                       |                                                                                     | 0.8                                        |      |      | V       |

| Input Current, Input Voltage Low                     | I <sub>IL(VID)</sub>                                       | VID(X) = 0 V                                                                        |                                            | -25  | -35  | μA      |

| Input Current, Input Voltage High                    | I <sub>IH(VID)</sub>                                       | VID(X) = 1.25 V                                                                     |                                            | 5    | 15   | μΑ      |

| Pull-Up Resistance                                   | R <sub>VID</sub>                                           | . ,                                                                                 | 35                                         | 60   | 85   | kΩ      |

| Internal Pull-Up Voltage                             | 1.5                                                        |                                                                                     | 0.9                                        | 1.1  |      | V       |

| VID Transition Delay Time                            |                                                            | VID code change to FB change                                                        | 400                                        | •••  |      | ns      |

| No CPU Detection Turn-Off Delay<br>Time <sup>2</sup> |                                                            | VID code change to 11111 to PWM going low                                           | 400                                        |      |      | ns      |

| OSCILLATOR                                           |                                                            |                                                                                     |                                            |      |      |         |

| Frequency Range                                      | f <sub>OSC</sub>                                           |                                                                                     | 0.25                                       |      | 4    | MHz     |

| Frequency Variation                                  | <b>f</b> PHASE                                             | $T_A = 25$ °C, $R_T = 250 \text{ k}\Omega$ , 4-phase                                | 155                                        | 200  | 245  | kHz     |

|                                                      |                                                            | $T_A = 25$ °C, $R_T = 115 \text{ k}\Omega$ , 4-phase                                |                                            | 400  |      | kHz     |

|                                                      |                                                            | $T_A = 25^{\circ}\text{C}, R_T = 75 \text{ k}\Omega, 4\text{-phase}$                |                                            | 600  |      | kHz     |

| Output Voltage                                       | $V_{RT}$                                                   | $R_T = 100 \text{ k}\Omega \text{ to GND}$                                          | 1.9                                        | 2.0  | 2.1  | V       |

| RAMPADJ Output Voltage                               | V <sub>RAMPADJ</sub>                                       | RAMPADJ – FB                                                                        | -50                                        |      | +50  | mV      |

| RAMPADJ Input Current Range                          | IRAMPADJ                                                   |                                                                                     | 0                                          |      | 100  | μΑ      |

| CURRENT-SENSE AMPLIFIER                              |                                                            |                                                                                     |                                            |      |      | 1       |

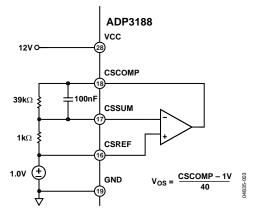

| Offset Voltage                                       | V <sub>OS(CSA)</sub>                                       | CSSUM – CSREF, Figure 3                                                             | 0.25 4 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 |      | mV   |         |

|                                                      |                                                            | T <sub>A</sub> = 25°C to 85°C, CSSUM – CSREF,<br>Figure 3                           | -1.5                                       |      | +1.5 | mV      |

| Input Bias Current                                   | I <sub>BIAS(CSSUM)</sub>                                   |                                                                                     | -50                                        |      | +50  | nA      |

| Gain Bandwidth Product                               | GBW <sub>(CSA)</sub>                                       |                                                                                     |                                            | 10   |      | MHz     |

| Slew Rate                                            |                                                            | $C_{CSCOMP} = 10 pF$                                                                |                                            | 10   |      | V/µs    |

| Input Common-Mode Range                              |                                                            | CSSUM and CSREF                                                                     | 0                                          |      | 2.7  | v       |

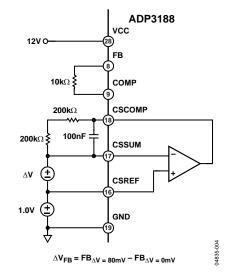

| Positioning Accuracy                                 | $\Delta V_{FB}$                                            | Figure 4                                                                            | -77                                        | -80  | -83  | mV      |

| Output Voltage Range                                 |                                                            |                                                                                     | 0.05                                       |      | 2.7  | V       |

| Output Current                                       | I <sub>CSCOMP</sub>                                        |                                                                                     |                                            | 500  |      | μΑ      |

| CURRENT-BALANCE CIRCUIT                              |                                                            |                                                                                     |                                            |      |      |         |

| Common-Mode Range                                    | $V_{SW(X)CM}$                                              |                                                                                     | -600                                       |      | +200 | mV      |

| Input Resistance                                     | R <sub>SW(X)</sub>                                         | SW(X) = 0 V                                                                         | 20                                         | 30   | 40   | kΩ      |

| Input Current                                        | I <sub>SW(X)</sub>                                         | SW(X) = 0 V                                                                         | 4                                          | 7    | 10   | μА      |

| Input Current Matching                               | $\Delta I_{SW(X)}$                                         | SW(X) = 0 V                                                                         | -5                                         |      | +5   | %       |

| Parameter                         | Symbol                     | Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Min Typ |      |      |       |

|-----------------------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|------|-------|

| CURRENT-LIMIT COMPARATOR          |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |      |      |       |

| Output Voltage                    |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |      |      |       |

| Normal Mode                       | V <sub>ILIMIT(NM)</sub>    | EN $> 0.8$ V, $R_{ILIMIT} = 250 \text{ k}\Omega$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2.9     | 3    | 3.1  | V     |

| Shutdown Mode                     | $V_{ILIMIT(SD)}$           | $EN < 0.4 \text{ V, } I_{ILIMIT} = -100  \mu\text{A}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |      | 400  | mV    |

| Output Current, Normal Mode       | I <sub>ILIMIT(NM)</sub>    | $EN > 0.8 \text{ V, R}_{\text{ILIMIT}} = 250 \text{ k}Ω$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         | 12   |      | μА    |

| Maximum Output Current            |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 60      |      |      | μA    |

| Current-Limit Threshold Voltage   | <b>V</b> CL                | $V_{CSREF} - V_{CSCOMP}$ , $R_{ILIMIT} = 250 \text{ k}\Omega$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 105     | 125  | 145  | mV    |

| Current-Limit Setting Ratio       |                            | V <sub>CL</sub> /I <sub>ILIMIT</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         | 10.4 |      | mV/μA |

| DELAY Normal Mode Voltage         | V <sub>DELAY(NM)</sub>     | $R_{DELAY} = 250 \text{ k}\Omega$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2.9     | 3    | 3.1  | ν .   |

| DELAY Overcurrent Threshold       | V <sub>DELAY(OC)</sub>     | $R_{DELAY} = 250 \text{ k}\Omega$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1.7     | 1.8  | 1.9  | V     |

| Latch-Off Delay Time              | t <sub>DELAY</sub>         | $R_{DELAY} = 250 \text{ k}\Omega$ , $C_{DELAY} = 12 \text{ nF}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         | 1.5  |      | ms    |

| SOFT START                        |                            | TOLEN TO THE OFFICE OF THE OFF |         |      |      |       |

| Output Current, Soft-Start Mode   | I <sub>DELAY(SS)</sub>     | During startup, DELAY < 2.4 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15      | 20   | 25   | μΑ    |

| Soft-Start Delay Time             | t <sub>DELAY(SS)</sub>     | $R_{DELAY} = 250 \text{ k}\Omega$ , $C_{DELAY} = 12 \text{ nF}$ ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         | 1    |      | ms    |

| •                                 | , ,                        | VID code= 011111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |      |      |       |

| ENABLE INPUT                      |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |      |      |       |

| Input Low Voltage                 | $V_{\text{IL}(EN)}$        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |      | 0.4  | V     |

| Input High Voltage                | $V_{\text{IH}(\text{EN})}$ |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0.8     |      |      | V     |

| Input Current, Input Voltage Low  | I <sub>IL(EN)</sub>        | EN = 0 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -1      |      | +1   | μΑ    |

| Input Current, Input Voltage High | I <sub>IH(EN)</sub>        | EN = 1.25 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         | 10   | 25   | μΑ    |

| POWER GOOD COMPARATOR             |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |      |      |       |

| Undervoltage Threshold            | $V_{PWRGD(UV)}$            | Relative to nominal DAC output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -180    | -250 | -300 | mV    |

| Overvoltage Threshold             | $V_{PWRGD(OV)}$            | Relative to nominal DAC output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 90      | 150  | 200  | mV    |

| Output Low Voltage                | $V_{OL(PWRGD)}$            | $I_{PWRGD(SINK)} = 4 \text{ mA}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         | 225  | 400  | mV    |

| Power Good Delay Time             |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |      |      |       |

| During Soft Start <sup>2</sup>    |                            | $R_{DELAY}$ = 250 kΩ, $C_{DELAY}$ = 12 nF, VID code = 011111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1       |      |      | ms    |

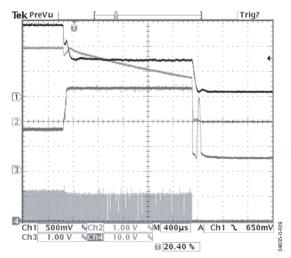

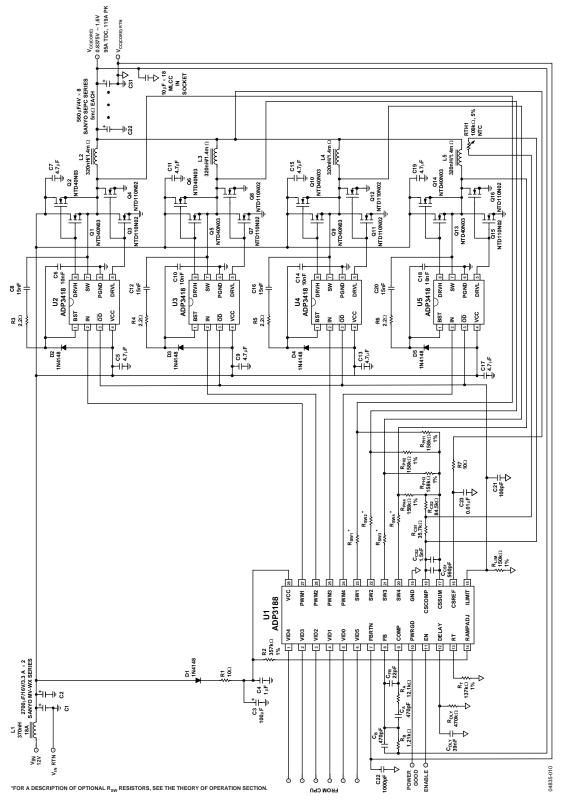

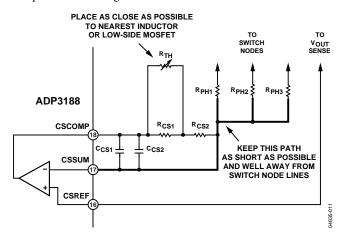

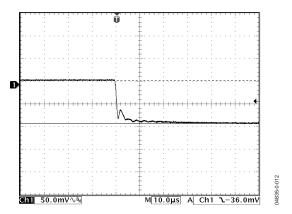

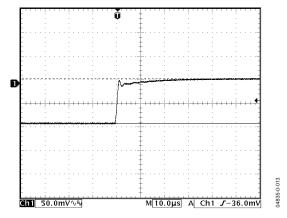

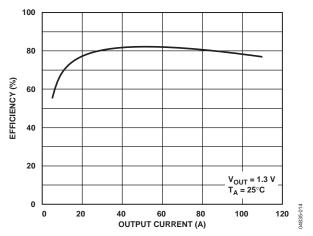

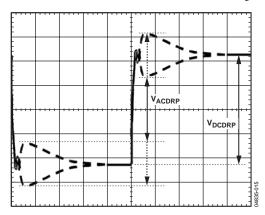

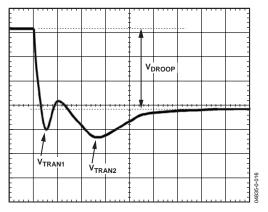

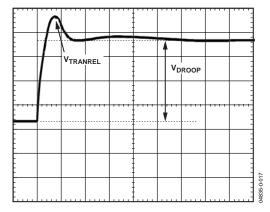

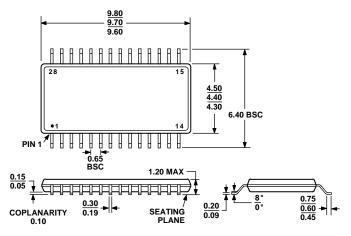

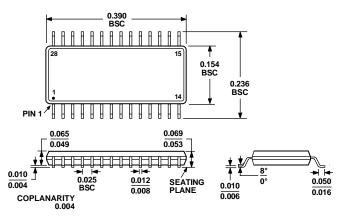

| VID Code Changing                 |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 100     | 250  |      | μs    |