# Stand-alone USB Type-C<sup>TM</sup> Power Delivery 3.0 Controller

### **Highlights**

- Single-chip USB Type-C<sup>™</sup> (1) Power Delivery Solution for Stand-alone Source-only

- · Preprogrammed Power Delivery Firmware

- Supports Standard Power Delivery Power Profiles (15/27/45/60W)

- USB Power Delivery 3.0 Compliant MAC

- USB Type-C<sup>™</sup> Connector Support with Connection Detection and Control

- Integrated Analog Discrete Components Reduce Bill of Materials and Design Footprint

- Easily Supports 2<sup>nd</sup> Port via UPD350 Add-on

- Commercial, Industrial, and Automotive Temperature Support

### **Target Applications**

- · Point-of-Sale Terminals

- · Charging Lockers

- · IoT Products and Sensors

- · Smart Speakers and Monitors

- · Conference Systems

- · Power Tools

- · Multi-port Charging Docks

- · Automotive Rear Seat Charging Ports

### **Key Benefits**

- Preprogrammed Power Delivery Firmware

- Supports Standard Power Delivery Power Profiles (15/27/45/60W)

- No Custom Firmware Development Required

- · Multiple Stand-alone Configurations via Pin Straps

- Power Delivery Power Profile Selection

- Optional Two Port Solution via External UPD350

- SPI for External UPD350 Communication

- Power Delivery Firmware Controls Both Ports

- · Integrated Analog Discrete Components

- VCONN FETs with Rp/Rd Switching

- Programmable Current Sense for Overcurrent Conditions

- Voltage Sense for Overvoltage Conditions

- · USB Power Delivery MAC

- Compliant with USB Power Delivery Specification Revision 3.0

- Power Delivery Packet Framing

- CRC Checking/Generation

- 4B/5B Encoding/Decoding

- BMC Encoding/Decoding

- EOP/SOP Generation for PD Frames

- SOP Detection and SOP Header Processing

- Separate RX/TX FIFOs

- Automatic GoodCRC Message Generation

- Automatic Retry Generation

- Error Handling

- Low Standby Power Support

- USB Type-C Cable Detect Logic

- Auto Cable Attach & Orientation Detection

- Routes Baseband Communication to Respective CC Pin per Detected Orientation

- VCONN Supply Control for Active Cable

- Strappable Downstream Facing Port (DFP) Modes

- Charging Current Capability Detection

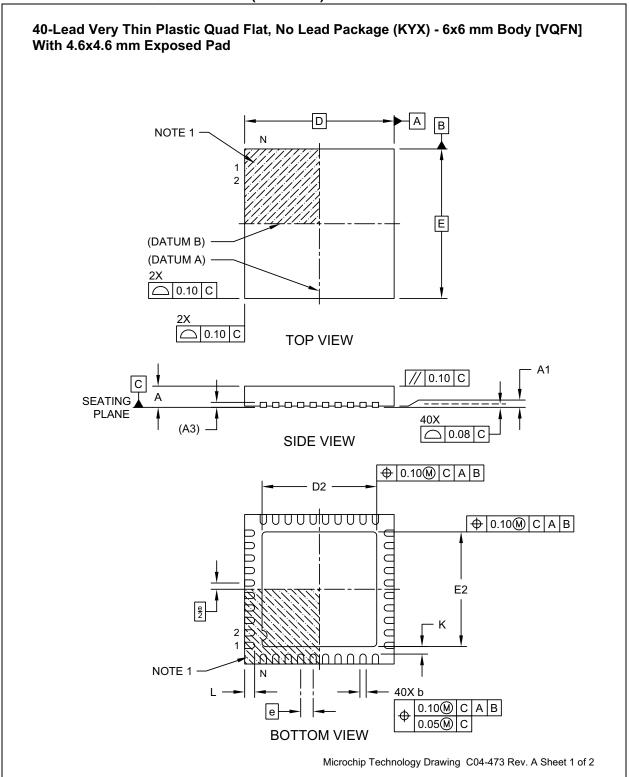

- Package

- 40-VQFN (6.0mm x 6.0mm)

- Environmental

- Commercial Temperature Range (0°C to +70°C)

- Industrial / AEC-Q100 Automotive Grade 3 Temperature Range (-40°C to +85°C)

USB Type-C<sup>™</sup> and USB-C<sup>™</sup> are trademarks of USB Implementers Forum.

#### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at docerrors@microchip.com. We welcome your feedback.

#### **Most Current Documentation**

To obtain the most up-to-date version of this documentation, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- · Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include -literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

# **Table of Contents**

| 1.0 Preface                             | 4  |

|-----------------------------------------|----|

| 2.0 Introduction                        | 7  |

| 3.0 Pin Descriptions and Configuration  | 9  |

| 4.0 Functional Descriptions             |    |

| 5.0 Operational Characteristics         |    |

| 6.0 Package Information                 | 32 |

| Appendix A: Data Sheet Revision History | 36 |

| The Microchip Web Site                  | 37 |

| Customer Change Notification Service    | 37 |

| Customer Support                        | 37 |

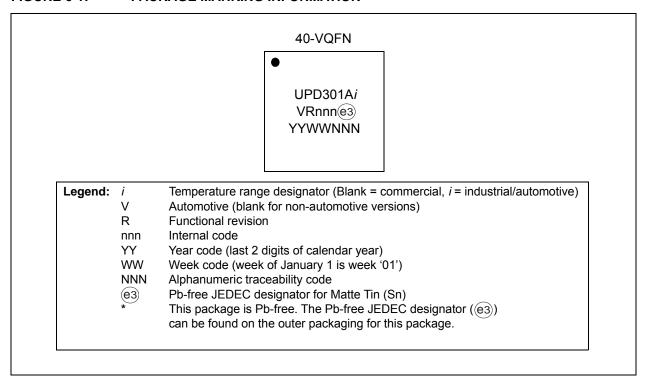

| Product Identification System           |    |

# 1.0 PREFACE

# 1.1 Glossary of Terms

# TABLE 1-1: GLOSSARY OF TERMS

| Term      | Definition                                                                                                                                                                                                                                         |  |  |  |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| ADC       | Analog to Digital Converter                                                                                                                                                                                                                        |  |  |  |

| AFE       | Analog Front End                                                                                                                                                                                                                                   |  |  |  |

| BCI       | Baseband CC Interface                                                                                                                                                                                                                              |  |  |  |

| Billboard | USB Billboard Device. A required USB device class for UFPs which support Alternate Modes in order to provide product information to the USB Host.                                                                                                  |  |  |  |

| BIST      | Built-In Self Test                                                                                                                                                                                                                                 |  |  |  |

| вмс       | Bi-phase Mark Coding                                                                                                                                                                                                                               |  |  |  |

| Byte      | 8-bits                                                                                                                                                                                                                                             |  |  |  |

| CC        | Generic reference to USB Type-C <sup>™</sup> Cable / Connector CC1/CC2 pins                                                                                                                                                                        |  |  |  |

| CSR       | Control and Status Register                                                                                                                                                                                                                        |  |  |  |

| DFP       | Downstream Facing Port (USB Type-C™ Specification definition)                                                                                                                                                                                      |  |  |  |

| DP        | DisplayPort (a VESA standard interface)                                                                                                                                                                                                            |  |  |  |

| DPM       | Device Policy Manager (PD Specification definition)                                                                                                                                                                                                |  |  |  |

| DWORD     | 32-bits                                                                                                                                                                                                                                            |  |  |  |

| EC        | Embedded Controller                                                                                                                                                                                                                                |  |  |  |

| EP        | USB Endpoint                                                                                                                                                                                                                                       |  |  |  |

| ESD       | Electro-Static Discharge                                                                                                                                                                                                                           |  |  |  |

| FIFO      | First In First Out buffer                                                                                                                                                                                                                          |  |  |  |

| FW        | Firmware                                                                                                                                                                                                                                           |  |  |  |

| FS        | Full-Speed                                                                                                                                                                                                                                         |  |  |  |

| GPIO      | General Purpose Input/Output                                                                                                                                                                                                                       |  |  |  |

| Host      | External system (Includes processor, application software, etc.)                                                                                                                                                                                   |  |  |  |

| НВМ       | Human Body Model (Simulates ESD from humans)                                                                                                                                                                                                       |  |  |  |

| HPD       | Hot-Plug Detect functionality as defined by DisplayPort and DisplayPort Alternate Mode specifications                                                                                                                                              |  |  |  |

| HS        | High-Speed                                                                                                                                                                                                                                         |  |  |  |

| HW        | Hardware (Refers to function implemented by the device)                                                                                                                                                                                            |  |  |  |

| IC        | Integrated Circuit                                                                                                                                                                                                                                 |  |  |  |

| IFC       | InterFrame Gap                                                                                                                                                                                                                                     |  |  |  |

| LDO       | Linear Drop-Out regulator                                                                                                                                                                                                                          |  |  |  |

| MAC       | Media Access Controller                                                                                                                                                                                                                            |  |  |  |

| Microchip | Microchip Technology Incorporated                                                                                                                                                                                                                  |  |  |  |

| N/A       | Not Applicable                                                                                                                                                                                                                                     |  |  |  |

| NC        | No Connect (pin)                                                                                                                                                                                                                                   |  |  |  |

| ocs       | Over-Current Sense                                                                                                                                                                                                                                 |  |  |  |

| PCS       | Physical Coding Sublayer                                                                                                                                                                                                                           |  |  |  |

| PD / UPD  | USB Power Delivery                                                                                                                                                                                                                                 |  |  |  |

| PDO       | Power Delivery Object (USB PD Specification definition) PDOs enable the port to indicate its Port Partner supported combinations of Voltage/Current or Power as well as the type of supply (Fixed, Variable, Battery) in Source Role or Sink Role. |  |  |  |

| PDP       | Power Delivery Power (USB PD Specification definition) A wattage value which corresponds to a set of voltages with corresponding current values.                                                                                                   |  |  |  |

TABLE 1-1: GLOSSARY OF TERMS (CONTINUED)

| Term                            | Definition                                                                                                                                                                                                                                                         |  |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| PIO                             | General Purpose I/O                                                                                                                                                                                                                                                |  |

| PMIC                            | Power Management Integrated Circuit                                                                                                                                                                                                                                |  |

| POR                             | Power-On Reset                                                                                                                                                                                                                                                     |  |

| Port Partner                    | Remote port which is connected to the UPD301A's local port                                                                                                                                                                                                         |  |

| PRBS                            | Pseudo Random Binary Sequence                                                                                                                                                                                                                                      |  |

| QWORD                           | 64-bits                                                                                                                                                                                                                                                            |  |

| SA                              | Source Address                                                                                                                                                                                                                                                     |  |

| SBU                             | SideBand Use                                                                                                                                                                                                                                                       |  |

| SCSR                            | System Control and Status Register                                                                                                                                                                                                                                 |  |

| Source Role                     | USB Type-C port is sinking power from its Port Partner                                                                                                                                                                                                             |  |

| Source-only<br>Operation        | Operation exclusively in USB Type-C / Power Delivery Source Role as defined in the USB Type-C and Power-Delivery specifications. In this mode of operation, USB Type-C Dual-Role Power Operation is not supported and there is no support for USB Power Role Swap. |  |

| SPI                             | Serial Peripheral Interface                                                                                                                                                                                                                                        |  |

| SPM                             | System Policy Manager (USB PD Specification definition)                                                                                                                                                                                                            |  |

| SS                              | SuperSpeed                                                                                                                                                                                                                                                         |  |

| Stand-alone Mode                | Chip operation without the control or configuration by an external MCU. Policy is defined locally by the UPD301A firmware. Configuration is achieved by use of configuration straps.                                                                               |  |

| SVDM                            | Standard/Vendor Defined Message (USB PD Specification definition)                                                                                                                                                                                                  |  |

| SVID                            | Standard/Vendor IDentity (USB PD Specification definition)                                                                                                                                                                                                         |  |

| TCPC                            | USB Type-C™ Port Controller                                                                                                                                                                                                                                        |  |

| UFP                             | Upstream Facing Port (USB Type-C™ Specification definition)                                                                                                                                                                                                        |  |

| USB                             | Universal Serial Bus                                                                                                                                                                                                                                               |  |

| USB Power<br>Delivery Operation | Port is operating using USB Power Delivery protocols in conformance to the USB PD Specification.                                                                                                                                                                   |  |

| USB Power<br>Role Swap          | Message sequence as defined in the USB PD Specification, enabling a transition between Source Role and Sink Role during USB Power Delivery Operation                                                                                                               |  |

| USB Type-C™                     | USB Type-C™ Cable / Connector                                                                                                                                                                                                                                      |  |

| VDO                             | Vendor-Defined Object (USB PD Specification definition)                                                                                                                                                                                                            |  |

| VSM                             | Vendor Specific Messaging                                                                                                                                                                                                                                          |  |

| WORD                            | 16-bits                                                                                                                                                                                                                                                            |  |

| ZLP                             | Zero Length USB Packet                                                                                                                                                                                                                                             |  |

# 1.2 Buffer Types

TABLE 1-2: BUFFER TYPES

| Buffer Type | Description                                                                                                                                                                                                                                   |  |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1           | Input                                                                                                                                                                                                                                         |  |

| IS          | Schmitt-triggered input                                                                                                                                                                                                                       |  |

| O2          | Output with 2 mA sink and 2 mA source                                                                                                                                                                                                         |  |

| OD2         | Open-drain output with 2 mA sink and 2 mA source                                                                                                                                                                                              |  |

| O8          | Output with 8 mA sink and 8 mA source                                                                                                                                                                                                         |  |

| PD          | 200kΩ (typical) internal pull-down.                                                                                                                                                                                                           |  |

|             | Note: Internal pull-down resistors prevent unconnected inputs from floating. Do not rely on internal resistors to drive signals external to the device. When connected to a load that must be pulled low, an external resistor must be added. |  |

| Al          | Analog input                                                                                                                                                                                                                                  |  |

| AO          | Analog output                                                                                                                                                                                                                                 |  |

| AIO         | Analog bidirectional                                                                                                                                                                                                                          |  |

| Р           | Power pin                                                                                                                                                                                                                                     |  |

**Note:** Refer to Section 5.5, "DC Characteristics," on page 28 for the electrical characteristics of the various buffers.

#### 1.3 References

- USB Power Delivery: https://www.usb.org/document-library/usb-power-delivery.

- USB Type-C™ Specification: i<a href="https://www.usb.org/document-library/usb-type-cr-cable-and-connector-specification-revision-14-march-29-2019">https://www.usb.org/document-library/usb-type-cr-cable-and-connector-specification-revision-14-march-29-2019</a>

### 2.0 INTRODUCTION

## 2.1 General Description

The UPD301A is a stand-alone, small form factor USB Type-C™ Power Delivery (PD) Port Controller designed to adhere to the *USB Type-C™ Cable and Connector Specification* and *USB Power Delivery 3.0 Specification*. The UPD301A provides stand-alone operation for source PD applications, enabling cable plug orientation and detection for a USB Type-C receptacle, and implementing baseband communication with a partner USB Type-C device via the integrated USB Power Delivery 3.0 MAC.

The embedded 32-bit ARM Cortex-M0+ implements a full Power Delivery firmware stack, providing a turn-key solution for USB-C™ power-only applications, and requiring minimal customer development. Configuration is supported via pin straps to select source functionality and PD power profiles. Optionally, a second PD port is supported via SPI connection of an external Microchip UPD350.

Additionally, the UPD301A integrates many of the analog discrete components required for USB Type-C PD applications, including two VCONN FETs with Rp/Rd switching and current/voltage sense circuitry for over-voltage/current detection. By integrating the PD firmware and many of the analog discrete components required for USB Type-C PD applications, the UPD301A provides a low cost, stand-alone, fast time-to-market solution for consumer, industrial, and automotive applications.

The UPD301A is available in commercial (0°C to +70°C) and industrial/automotive grade 3 (-40°C to +85°C) temperature ranges. For ordering information, refer to the Product Identification System on page 38.

# 2.2 Example Applications

The UPD301A has been designed for multiple applications, including:

- · Source-Only Applications (E.G., Charging Ports)

- · Two-Port Applications (E.G., Automotive Rear Seat Charging)

Note: Single-Port Source and Dual-Port Source modes are the only supported modes of operation.

#### 2.2.1 SOURCE-ONLY APPLICATIONS (E.G., CHARGING PORTS)

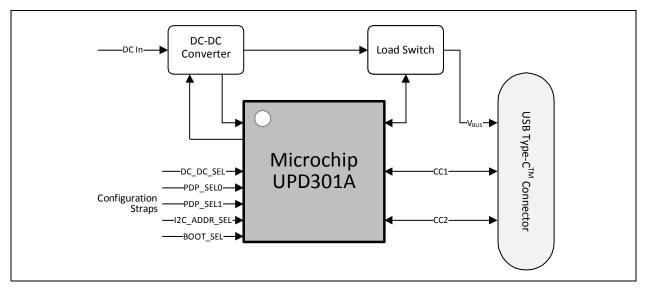

The simplest UPD301A application is a power source (Source-Only), as shown in Figure 2-1. Using the device configuration straps, various PD parameters/options can be configured. The integrated DAC configures the DC-DC converter, selecting the output voltage, and controls the load switch to regulate and protect the output voltage. The load switch can also be replaced by discrete FETs and over-current / over-voltage protection circuits.

FIGURE 2-1: SYSTEM BLOCK DIAGRAM - SOURCE-ONLY APPLICATION

### 2.2.2 TWO-PORT APPLICATIONS (E.G., AUTOMOTIVE REAR SEAT CHARGING)

Some applications, such as a automotive rear seat charging port, may need up to two USB Type-C™ power delivery ports. These ports can be implemented by connecting a UPD301A and a UPD350 via the SPI interface, as shown in Figure 2-2. The UPD301A will execute the stack for the UPD350. The two-port implementation supports dynamic power allocation (e.g., go-to power min based on an external input). The integrated DAC from the UPD301A and additional GPIOs from the UPD350 control the DC-DC converter, selecting the voltages, and control the load switch to regulate and protect the output voltage. The load switch can also be replaced by discrete FETs and over-current / over-voltage protection circuits.

DC-DC Load Switch Converter USB Type-C<sup>™</sup> Connector Microchip DC\_DC\_SEL-UPD301A -PDP SELO-Configuration Straps -I2C ADDR SEL-BOOT\_SEL -DC In SPI USB Type-C<sup>™</sup> Microchip **UPD350** Connector DC-DC DC In Load Switch Converter

FIGURE 2-2: SYSTEM BLOCK DIAGRAM - TWO-PORT APPLICATION

# 3.0 PIN DESCRIPTIONS AND CONFIGURATION

# 3.1 Pin Assignments

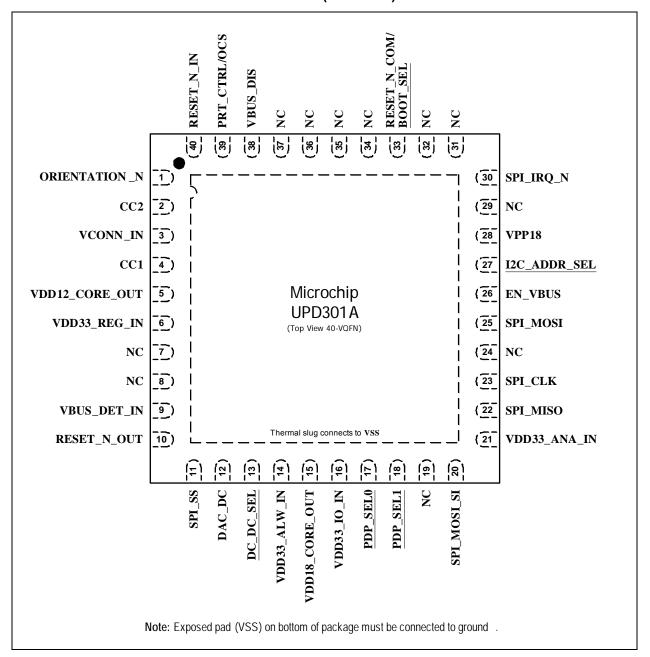

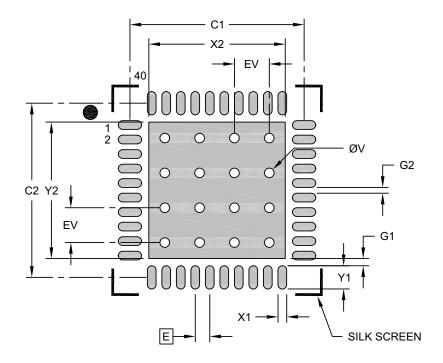

The device pin diagram for the UPD301A can be seen in Figure 3-1. Table 3-1 provides a UPD301A pin assignment table. Pin descriptions are provided in Section 3.2, "Pin Descriptions".

FIGURE 3-1: UPD301A PIN ASSIGNMENTS (TOP VIEW)

TABLE 3-1: UPD301A PIN ASSIGNMENTS

| Pin | Pin Name                                       | Pin | Pin Name              |  |  |

|-----|------------------------------------------------|-----|-----------------------|--|--|

| 1   | ORIENTATION_N                                  | 21  | VDD33_ANA_IN          |  |  |

| 2   | CC2                                            | 22  | SPI_MISO              |  |  |

| 3   | VCONN_IN                                       | 23  | SPI_CLK               |  |  |

| 4   | CC1                                            | 24  | NC                    |  |  |

| 5   | VDD12_CORE_OUT                                 | 25  | SPI_MOSI              |  |  |

| 6   | VDD33_REG_IN                                   | 26  | EN_VBUS               |  |  |

| 7   | NC                                             | 27  | I2C ADDR SEL          |  |  |

| 8   | NC                                             | 28  | VPP18                 |  |  |

| 9   | VBUS_DET_IN                                    | 29  | NC                    |  |  |

| 10  | RESET_N_OUT                                    | 30  | SPI_IRQ_N             |  |  |

| 11  | SPI_SS                                         | 31  | NC                    |  |  |

| 12  | DAC_DC                                         | 32  | NC                    |  |  |

| 13  | DC DC SEL                                      | 33  | RESET_N_CO M/BOOT_SEL |  |  |

| 14  | VDD33_ALW_IN                                   | 34  | NC                    |  |  |

| 15  | VDD18_CORE_OUT                                 | 35  | NC                    |  |  |

| 16  | VDD33_IO_IN                                    | 36  | NC                    |  |  |

| 17  | PDP SEL0                                       | 37  | NC                    |  |  |

| 18  | PDP SEL1                                       | 38  | VBUS_DIS              |  |  |

| 19  | NC                                             | 39  | PRT_CTRL/OCS          |  |  |

| 20  | SPI_MOSI_SI                                    | 40  | RESET_N_IN            |  |  |

|     | Exposed Pad (VSS) must be connected to ground. |     |                       |  |  |

# 3.2 Pin Descriptions

This sections details the functions of the various device signals.

TABLE 3-2: PIN DESCRIPTIONS

| Name                                 | Symbol      | Buffer<br>Type | Description                                                                                                              |  |  |

|--------------------------------------|-------------|----------------|--------------------------------------------------------------------------------------------------------------------------|--|--|

| USB Type-C™                          |             |                |                                                                                                                          |  |  |

| Configuration<br>Channel 1           | CC1         | AIO            | Configuration Channel (CC) used in the discovery, configuration and management of connections across a USB Type-C cable. |  |  |

| Configuration<br>Channel 2           | CC2         | AIO            | Configuration Channel (CC) used in the discovery, configuration and management of connections across a USB Type-C cable. |  |  |

| VBUS<br>Detection                    | VBUS_DET_IN | AIO            | Scaled down version of VBUS input used for VBUS detection. Tie this signal to VBUS via a resistor divider.               |  |  |

|                                      |             | SPI            | Interface                                                                                                                |  |  |

| SPI Clock                            | SPI_CLK     | IS             | SPI clock. The maximum supported SPI clock frequency is 8 MHz.                                                           |  |  |

| SPI Data<br>Master In /<br>Slave Out | SPI_MISO    | I/O8           | SPI data master in, slave out.                                                                                           |  |  |

| SPI Data<br>Master Out /<br>Slave In | SPI_MOSI    | O2             | SPI data master out / slave in. This pin must be connected to SPI_MOSI_SI for proper operation.                          |  |  |

| SPI Data<br>Slave In                 | SPI_MOSI_SI | IS             | SPI data slave in. This pin must be connected to <b>SPI_MOSI</b> for proper operation.                                   |  |  |

| SPI Chip<br>Enable                   | SPI_SS      | O2             | Active low SPI chip enable input for optional external UPD350.                                                           |  |  |

| SPI Interrupt                        | SPI_IRQ_N   | I              | SPI interrupt indicating request for service from optional external UPD350.                                              |  |  |

| DC/DC Control                        |             |                |                                                                                                                          |  |  |

| DAC Output<br>(Source)               | DAC_DC      | AO             | In the Source Role, this DAC output is used to control the DC/DC converter output voltage.                               |  |  |

| Miscellaneous                        |             |                |                                                                                                                          |  |  |

| VBUS Load<br>Switch Enable           | EN_VBUS     | O8             | When asserted, closes the VBUS load switch. Only valid in the Attach.SRC state.                                          |  |  |

| VBUS<br>Discharge                    | VBUS_DIS    | O8             | When asserted, enables external current sink in order to discharge VBUS.                                                 |  |  |

TABLE 3-2: PIN DESCRIPTIONS (CONTINUED)

| Butter        |                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|---------------|-----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Symbol        | Buffer<br>Type                                                                                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| PRT_CTRL/OCS  | I/O2/OD2                                                                                      | When the UPD301A is in the Source Role, any external VBUS/VCONN/temperature faults may be wire-ORed on OCS to indicate a default has occurred, prompting the device's firmware to make VBUS safe (open load switches, discharge VBUS, and enter error recovery).                                                                                                                                                                                                                                                                                                              |  |  |

|               |                                                                                               | When the UPD301A is in the Source Role, this pin is a bidirectional signal indicating various faults to a load switch, DC/DC converter, DFP or hub. This pin is nominally configured as an output, sending faults to a load switch or DC/DC converter. However, if a different fault condition (e.g. overvoltage) is detected internally by the UPD301A, this pin is reconfigured as an open-drain output with an internal pull-down enabled and asserted low for a duration to allow detection by the hub's PRT_ENx/OCSx_N input, and is then reconfigured back to an input. |  |  |

|               |                                                                                               | <b>Note:</b> For proper operation, a 100kOhm pull-up to +3.3V should be applied to this pin externally.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| ORIENTATION_N | O2                                                                                            | This signal is used to indicate which CC pin is terminated by the attached device. When asserted CC = CC1, otherwise CC=CC2.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|               |                                                                                               | <b>Note:</b> For proper operation, a 200kOhm pull-up to +3.3V should be applied to this pin externally.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| RESET_N_IN    | I                                                                                             | Active low system reset input. This reset is used for reset of the UPD301A by a companion MCU.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| RESET_N_OUT   | O2                                                                                            | Active low system reset output. This pin must be connected to <b>RESET_N_COM</b> for proper operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| RESET_N_COM   | IS                                                                                            | This pin must be connected to <b>RESET_N_OUT</b> for proper operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| NC            | -                                                                                             | For proper operation, this pin must be left unconnected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|               | Configu                                                                                       | ration Straps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| PDP SEL0      | 1/02                                                                                          | This multi-level configuration strap is sampled after system reset to specify a Power Delivery Power (PDP) which defines the voltages and currents to be used by the UPD301A Power Delivery Objects (PDOs).                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|               |                                                                                               | Refer to Section 3.3, "Configuration Straps" for additional information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| PDP SEL1      | I/O2                                                                                          | For a two port system, this multi-level configuration strap is sampled after a system reset to specify a Power Delivery Power (PDP) which defines the voltages and currents to be used by the optional external UPD350 Power Delivery Objects (PDOs).                                                                                                                                                                                                                                                                                                                         |  |  |

|               |                                                                                               | Refer to Section 3.3, "Configuration Straps" for additional information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| I2C ADDR SEL  | AIO                                                                                           | This multi-level configuration signal is sampled after a system reset to select the device's default I <sup>2</sup> C slave address.  Refer to Section 3.3, "Configuration Straps" for additional information.                                                                                                                                                                                                                                                                                                                                                                |  |  |

|               | Symbol PRT_CTRL/OCS  ORIENTATION_N  RESET_N_IN RESET_N_OUT RESET_N_COM NC  PDP_SEL0  PDP_SEL1 | Symbol   Buffer Type                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

TABLE 3-2: PIN DESCRIPTIONS (CONTINUED)

| tem reset to<br>boot using a                  |

|-----------------------------------------------|

| tem reset to<br>is configured<br>r additional |

|                                               |

|                                               |

|                                               |

|                                               |

|                                               |

| uF capacitor                                  |

|                                               |

|                                               |

| gnal must be<br>per opera-                    |

| ust be con-<br>operation.                     |

|                                               |

| ti r                                          |

#### 3.3 Configuration Straps

Configuration straps are used during Power-On Reset (POR) or external chip reset (RESET\_N) to determine the default configuration of a particular feature. The state of the signal is latched following deassertion of the reset. Configuration straps are identified by an underlined symbol name. This section details the various device configuration straps and associated functions.

#### 3.3.1 PDP\_SEL0/PDP\_SEL1 CONFIGURATION STRAPS

The <u>PDP\_SEL0</u> and <u>PDP\_SEL1</u> configuration straps are used to define the normative Power Delivery Object (PDO) support in the Source Role, as defined in Chapter 10 of the USB Power Delivery Specification.

In the Source Role, the Power Delivery Power (PDP) defines all of the normative PDOs returned in the USB PD Source\_Capabilities Message. These correspond to the fixed voltages and currents the Source supports.

The PDP SEL0 input configuration strap is used to define the PDP value used to configure the UPD301A.

The <u>PDP\_SEL1</u> input configuration strap is used to define the PDP value used to configure the external UPD350 for the optional UPD301A two port solution.

The <u>PDP SEL0</u> and <u>PDP SEL1</u> configuration straps are each encoded to one of five possible values determined by external resistors. Table 3-3 indicates the PDP that each configuration corresponds to and the PDO values that should be returned in the USB Power Delivery Source capabilities.

TABLE 3-3: PDP SEL RESISTOR ENCODING

| PDP SELx Resistor Value | PDP   | PDO 1     | PDO 2   | PDO 3    | PDO 4    |

|-------------------------|-------|-----------|---------|----------|----------|

| 200 kΩ Pull-Down        | 7.5 W | 5 V@1.5 A | -       | -        | -        |

| 200 kΩ Pull-Up          | 15 W  | 5 V@3 A   | -       | -        | -        |

| 4.7 kΩ Pull-Down        | 27 W  | 5 V@3 A   | 9 V@3 A | -        | -        |

| 4.7 kΩ Pull-Up          | 45 W  | 5 V@3 A   | 9 V@3 A | 15 V@3 A | -        |

| 10 Ω Pull-Down          | 60 W  | 5 V@3 A   | 9 V@3 A | 15 V@3 A | 20 V@3 A |

#### 3.3.2 I2C ADDR SEL CONFIGURATION STRAP

The <u>I2C ADDR SEL</u> configuration strap is used to define the default I<sup>2</sup>C address that the UPD301A will respond to when operating as a companion MCU. The <u>I2C ADDR SEL</u> configuration strap is encoded to one of six possible values determined by external resistors, as detailed in <u>Table 3-4</u>.

TABLE 3-4: <u>I2C ADDR SEL</u> RESISTOR ENCODING

| <u>I2C ADDR SEL</u> Resistor Value | I <sup>2</sup> C Slave Address |

|------------------------------------|--------------------------------|

| 200 kΩ Pull-Down                   | 1111_000                       |

| 200 kΩ Pull-Up                     | 1101_000                       |

| 20 kΩ Pull-Down                    | 1101_001                       |

| 20 kΩ Pull-Up                      | 1101_010                       |

| 10 Ω Pull-Down                     | 1101_011                       |

| 10 Ω Pull-Up                       | 1101_100                       |

# 3.3.3 BOOT\_SEL CONFIGURATION STRAP

The <u>BOOT SEL</u> configuration strap is used to select the UPD301A boot mode between a normal boot or a boot ROM boot, and is implemented using a weak pull-up/pull-down of 200 k $\Omega$ , as shown in Table 3-5.

TABLE 3-5: BOOT SEL RESISTOR ENCODING

| BOOT SEL Resistor Value | Setting            |

|-------------------------|--------------------|

| 200 kΩ Pull-Down        | Boot from boot ROM |

| 200 kΩ Pull-Up          | Normal operation   |

# 3.3.4 DC\_DC\_SEL CONFIGURATION STRAP

The DC DC SEL configuration strap is used to specify which DC/DC converter the DAC output is configured for.

The <u>DC DC SEL</u> configuration strap is encoded to one of three possible values determined by external resistors, as detailed in Table 3-6.

TABLE 3-6: DC DC SEL RESISTOR ENCODING

| DC DC SEL Resistor Value | DAC Output                                                        |

|--------------------------|-------------------------------------------------------------------|

| 200 kΩ Pull-Down         | General linear DAC operation. The DAC output range is defined as: |

|                          | • 0V - 0V on VBUS                                                 |

|                          | • 2.5V = 20V on VBUS                                              |

|                          | This output is linear for the range in between.                   |

| 200 kΩ Pull-Up           | Reserved for future use.                                          |

| 4.7 kΩ Pull-Down         | Reserved for future use.                                          |

### 4.0 FUNCTIONAL DESCRIPTIONS

This section provides functional descriptions of the following:

- · Serial Peripheral Interface (SPI)

- · Power States

- · Cable Plug Orientation and Detection

- · Baseband CC Interface (BCI)

- Power Delivery MAC

- · Supported Power Delivery (PD) Functionality

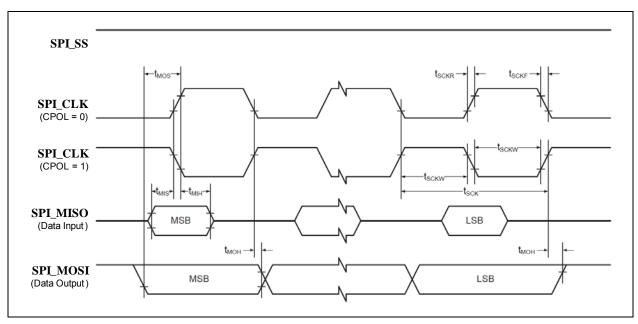

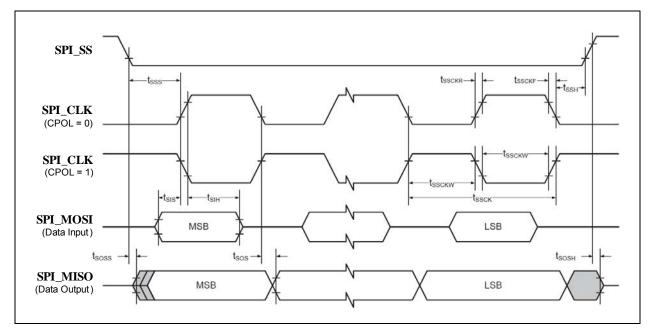

# 4.1 Serial Peripheral Interface (SPI)

The UPD301A integrates a SPI master/slave controller which includes the following features:

- • Full-duplex, four-wire interface (SPI\_MISO, SPI\_MOSI, SPI\_SCK, SPI\_SS)

- · · Single-buffered transmitter, double-buffered receiver

- · · Master operation:

- - Serial clock speed, f<sub>SCK</sub>=1/t<sub>SCK</sub>(Note 4-1)

- - 8-bit clock generator

- · · Slave operation:

- Serial clock speed, f<sub>SCK</sub>=1/t<sub>SSCK</sub>(Note 4-1)

- - Optional 8-bit address match operation

Note 4-1 For t<sub>SCK</sub> and t<sub>SSCK</sub> values, refer to Section 5.6.2, "SPI Timing"

The SPI is a high-speed synchronous data transfer interface which allows high-speed communication between the device and peripheral devices. The SPI can operate as a master or slave. As a master, the SPI initiates and controls all data transactions. The SPI is single buffered for transmitting and double buffered for receiving.

When transmitting data, a Data register is loaded with the next character to be transmitted during the current transmission. When receiving, the data is transferred to the two-level receive buffer, and the receiver is ready for a new character.

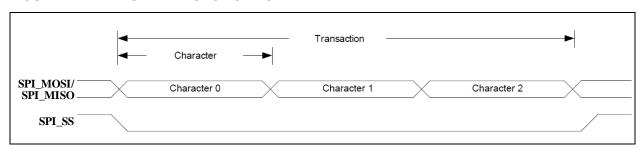

The SPI transaction format is shown in Figure 4-1. Each transaction can contain one or more characters. The character size is configurable, and can be either 8 or 9 bits.

#### FIGURE 4-1: SPI TRANSACTION FORMAT

The SPI master pulls the slave select line (SPI\_SS) of the desired slave low to initiate a transaction. The master and slave prepare data to send via their respective shift registers, and the master generates the serial clock on the SPI\_SCK line.

Data is always shifted from master to slave on the Master Output Slave Input line (SPI\_MOSI); data is shifted from slave to master on the Master Input Slave Output line (SPI\_MISO).

Each time character is shifted out from the master, a character will be shifted out from the slave simultaneously. To signal the end of a transaction, the master will pull the SPI\_SS line high.

#### 4.2 Power States

The device supports the following power states, as defined in their respective sub-sections:

- STANDBY

- ATTACHED IDLE

- ACTIVE

#### 4.2.1 STANDBY

STANDBY is the lowest power functional state of the device. The majority of the device is powered off in this state. The internal CC comparator and 20 KHz oscillator are enabled in this state as well as requisite analog components (1.8V LDO, PORs, Biases, etc).

The CC lines are constantly monitored for an attach condition which shall result in an interrupt assertion to the host. If an attachment has been made, this state can detect a change in the partner's advertisement as well as a detach.

STANDBY is the power state that the UPD301A device will be in when in USB Type-C<sup>™</sup> Unattached.SRC.

#### 4.2.2 ATTACHED IDLE

In this state, a USB Type-C™ device is connected and the USB PD bus is idle (no USB packets in transit). The CC signals are constantly being monitored for packet transmission.

#### 4.2.3 ACTIVE

This state defines the condition of the device after an attachment occurred. In this state, Power Delivery communication is supported. This state is also used for any condition in which the 48 MHz Relaxation Oscillator must be enabled, such as when it is desired to debounce a GPIO within the micro-second range.

When transmitting a Power Delivery packet, an additional 5 mA may be consumed. Additional power consumption results from enabling the OCS comparator, VBUS comparator and other modules. When VCONN FETs are enabled, there is an additional 70 mW of power consumption.

This section details the functions that control and monitor the CC pins, monitor the VBUS\_DET pin, control the VCONN FETs, and sample the CFG\_SEL pin.

# 4.3 Cable Plug Orientation and Detection

#### 4.3.1 CC COMPARATOR

The device integrates a comparator and DAC circuit to implement Type-C attach and detach functions. It supports up to eight programmable thresholds for attach detection between UFP and DFP. When operating as a UFP, the device supports detecting changes in the DFP's advertised thresholds to determine current sourcing capability. The default nominal values for the thresholds detected by the CC comparators are:

- 0.20 V

- 0.40 V

- 0.66 V

- 0.80 V

- 1.23 V

- 1.60 V

- 2.60 V

- 3.0 V Proprietary Mode

TABLE 4-1: CABLE DETECT SUMMARY

| Parameter   | Threshold CSR | Description                                                                             | Min | Тур    | Max |

|-------------|---------------|-----------------------------------------------------------------------------------------|-----|--------|-----|

| DFP_ACT_DEF | CC_THR0       | Detecting an active cable when configured as DFP and advertising default USB current.   |     | 0.20 V |     |

| UFP_DFP_DEF | CC_THR0       | Detecting DFP attach when configured as UFP and DFP is advertising default USB current. |     | 0.20 V |     |

| DFP_ACT_1A5 | CC_THR1       | Detecting an active cable when configured as DFP and advertising 1.5A.                  |     | 0.40 V |     |

| UFP_DFP_1A5 | CC_THR2       | Detecting DFP attach when configured as UFP and DFP is advertising 1.5A.                |     | 0.66 V |     |

| DFP_ACT_3A0 | CC_THR3       | Detecting an active cable when configured as DFP and advertising 3.0A.                  |     | 0.80 V |     |

| UFP_DFP_3A0 | CC_THR4       | Detecting DFP attach when configured as UFP and DFP is advertising 3.0A.                |     | 1.23 V |     |

| DFP_UFP_DEF | CC_THR5       | Detecting UFP attach when configured as DFP advertising default USB current.            |     | 1.60 V |     |

| DFP_UFP_1A5 | CC_THR5       | Detecting UFP attach when configured as DFP advertising 1.5A.                           |     | 1.60 V |     |

| DFP_UFP_3A0 | CC_THR6       | Detecting UFP attach when configured as DFP advertising 3.0A.                           |     | 2.60 V |     |

The following table summarizes the expected thresholds to be matched for various configurations.

TABLE 4-2: DFP CC MATCH SUMMARY

| CC State                                                     | CC<br>THR0 | CC<br>THR1 | CC<br>THR2 | CC<br>THR3 | CC<br>THR4 | CC<br>THR5 | CC<br>THR6 | CC<br>THR7 |

|--------------------------------------------------------------|------------|------------|------------|------------|------------|------------|------------|------------|

| Advertise Default USB Current and connected to powered cable | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 0          |

| Advertise 1.5 A and connected to powered cable               | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 0          |

| Advertise 3.0 A and connected to powered cable               | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 0          |

| Advertise Default USB Current and connected to UFP           | 1          | 0          | 0          | 0          | 0          | 0          | 0          | 0          |

| Advertise 1.5 A and connected to UFP                         | 0          | 1          | 0          | 0          | 0          | 0          | 0          | 0          |

| Advertise 3.0 A and connected to UFP                         | 0          | 0          | 0          | 1          | 0          | 0          | 0          | 0          |

| Advertise Default USB Current and no connect (vOpen)         | 1          | 0          | 0          | 0          | 0          | 1          | 0          | 0          |

| Advertise 1.5 A and no connect (vOpen)                       | 0          | 1          | 0          | 0          | 0          | 1          | 0          | 0          |

| Advertise 3.0 A and no connect (vOpen)                       | 0          | 0          | 0          | 1          | 0          | 0          | 1          | 0          |

| Proprietary Mode and no connect (vOpen)                      | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 1          |

#### 4.3.2 DFP OPERATION

The device implements current sources to advertise current charging capabilities on both CC pins when operating as a DFP.

When a UFP connection is established, the current driven across the CC pins creates a voltage across the UFP's Rd pull-down that can be detected by the integrated CC comparator. The voltages monitored are summarized in Table 4-3. When connected to an active cable, an alternative pull-down (Ra) appears on the CC pin.

The DFP also integrates two 5V FETs for implementing the VCONN function. This is further discussed in Section 4.3.5, "VCONN Operation".

TABLE 4-3: SOURCE DETECTION

| CC1  | CC2  | Connection State               | CC Comparator State                                          | VBUS | VCONN |

|------|------|--------------------------------|--------------------------------------------------------------|------|-------|

| Open | Open | Nothing Attached               | Monitor both CC pins for attach                              | Off  | Off   |

| Rd   | Open | UFP Attached                   | Monitor CC1 for detach                                       | On   | Off   |

| Open | Rd   | UFP Attached                   | Monitor CC2 for detach                                       | On   | Off   |

| Ra   | Open | Powered Cable, No UFP attached | Monitor CC2 for UFP attach.  Monitor CC1 for cable detach.   | Off  | Off   |

| Open | Ra   | Powered Cable, No UFP attached | Monitor CC1 for UFP attach.  Monitor CC2 for cable detach.   | Off  | Off   |

| Ra   | Rd   | Powered Cable, UFP attached    | Monitor CC2 for UFP detach. CC1 is not monitored for detach. | On   | On    |

| Rd   | Ra   | Powered Cable, UFP attached    | Monitor CC1 for UFP detach. CC2 is not monitored for detach. | On   | On    |

| Rd   | Rd   | Debug accessory mode attached  | Monitor both CC pins for detach                              | Off  | Off   |

| Ra   | Ra   | Audio accessory mode attached. | Monitor both CC pins for detach                              | Off  | Off   |

#### 4.3.3 RP CURRENT SOURCES

In order to advertise the current charging capabilities of the device via the integrated port power controller or external power circuit, Rp current sources are used. The current source can be selected by software. Table 4-4 summarizes the values supported by the current sources in regards to the programmed value.

TABLE 4-4: RP CURRENT SOURCES

| DFP Advertisement | Current source<br>(1.7V to 5.5V) | RPx Value |

|-------------------|----------------------------------|-----------|

| Disabl            | ed                               | 00b       |

| Default USB Power | 80 uA +/-20%                     | 01b       |

| 1.5A @ 5V         | 180 uA +/-8%                     | 10b       |

| 3.0A @ 5V         | 330 uA +/-8%                     | 11b       |

#### 4.3.4 COLLISION AVOIDANCE

An alternative mode of operation is required to enable the CC detection circuit to facilitate software implementation of collision detection which was incorporated into version 3.0 of the USB PD Specification.

In order to avoid message collisions due to asynchronous Messaging (AMS) sent from the Sink, the Source sets Rp to SinkTxOk (3A@5V) to indicate to the Sink that it is OK to initiate an AMS. When the Source wishes to initiate an AMS it sets Rp to SinkTxNG (1.5A@5V). When the Sink detects that Rp is set to SinkTxOk it may initiate an AMS. When the Sink detects that Rp is set to SinkTxNG it shall not initiate an AMS and shall only send Messages that are part of an AMS the Source has initiated.

#### 4.3.5 VCONN OPERATION

VCONN is a 5V supply that is used to power circuitry in the USB Type-C™ plug, which is required to implement Electronically Marked Cables. By default, the DFP always sources VCONN when connected to an active cable. However, this may be changed by software.

**APPLICATION NOTE:** It is not envisioned to ever enable both FETs simultaneously.

VCONN is monitored for an over current condition via an internal monitoring circuit. A VCONN over current condition is recognized when the event persists for a time longer than specified. When an over-current VCONN event is detected, an interrupt asserts. The device may be configured to automatically disable the VCONN FET upon detection of a CC1/CC2 Back-Drive Error or VCONN Discharge Error. In the event of the detection of a debounced over-current VCONN event, the enabled VCONN FET will be disabled.

#### 4.3.6 VBUS DETECTION

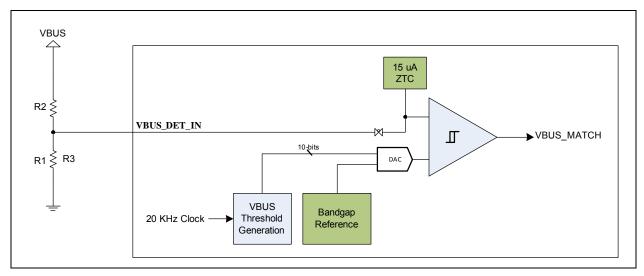

The device implements a comparator for determining when VBUS is within a programmed range, vSafe5V, or vSafe0v. VBUS is divided down externally via a 1:9 resistor divider to generate **VBUS\_DET\_IN**. **VBUS\_DET\_IN** is compared with an 8-bit threshold generated by an integrated DAC.

Figure 4-2 illustrates the VBUS\_DET\_IN circuit. In a typical use case, VBUS\_DET\_IN thresholds are programmed to track the following voltage ranges as defined in Table 4-5.

**Note:** Table 4-5 illustrates the values of VBUS\_DET\_IN utilizing +/-1% accurate resistors where R1 is 10K Ohms and R2 is 90 kOhms.

# FIGURE 4-2: VBUS\_DET\_IN COMPARATOR

For a DFP, the VBUS comparator is useful to detect when VBUS is within the desired range per PD negotiations. This is the case when VBUS is generated by a source external to the device.

For a UFP, the VBUS comparator is required to determine when a DFP is attached or detached. It may also use the comparator to determine when VBUS is within a new voltage range negotiated via PD.

TABLE 4-5: VBUS DETECTION THRESHOLDS

| VBUS | Range | VBUS_DET_IN | Comments |

|------|-------|-------------|----------|

| 20   | 21.5  | 2.11        |          |

| 20   | 18.5  | 1.82        |          |

| 10   | 13.1  | 1.29        |          |

| 12   | 10.9  | 1.07        |          |

| 0    | 8.9   | 0.88        |          |

| 8    | 7.1   | 0.69        |          |

| 5    | 5.5   | 0.51        |          |

| 5    | 3.67  | 0.33        | vSafe5V  |

| 0.68 | 0.68  | 0.068       | vSafe0V  |

If supported, the ranges 8V, 12V and 20V may be programmed in VBUS Threshold 2 and VBUS Threshold 3 registers. Likewise 5V range, vSafe5v, can be programmed in VBUS Threshold 0 and VBUS Threshold 1 registers.

The threshold for vSafe0V is programmable.

**VBUS\_DET\_IN** monitoring logic operates off of the 20 KHz oscillator which cycles through each threshold. Including vSafe0v, a total of five values are compared.

# 4.4 Baseband CC Interface (BCI)

The device integrates a Baseband CC Interface (BCI) to facilitate USB Power Delivery communication. This module bridges between the PD MAC/BMC and the analog front end. Baseband communication is initiated by the PD MAC, which interfaces to the BCI. The BCI implements the digital functions required to control TX baseband components.

#### 4.4.1 BASEBAND TX DATA-FLOW

The key responsibility of the BCI is to generate the wave form required for baseband communication. To this end, the BMC has a group of eight registers that define the Lo-Hi and Hi-Lo transitions for the generated BMC signal.

When instructed to transition from Lo-Hi, the BCI steps through all BB TX Rise Registers. Likewise when instructed to transition from Hi-Lo, the BCI steps through all BB TX Fall Registers

**APPLICATION NOTE:** The user may replicate values if it is desired to use less than twelve unique values for this purpose.

#### 4.4.2 BASEBAND RX DATA-FLOW

Baseband RX data is received by the BCI from the RX analog front end where it is compared to a threshold programmed by software. The CC RX DAC Value defines the trip point used for reception of baseband data. The field shall be programmed to be 175 mV below the RX Eye center, as defined in the PD Specification for the mode in which the device is operating (Sourcing Power, Sinking Power, Power Neutral).

#### 4.5 Power Delivery MAC

The PD MAC implements certain features of the protocol layer and physical layer of the Universal Serial Bus Power Delivery Specification. On one end the PD MAC interfaces to the software implementing the bulk of protocol and higher level layers and on the other end it interfaces to a BMC encoder / decoder module.

In addition to the normal TX and RX functions, the PD MAC implements the test mode logic defined in the USB PD specification (BIST).

The PD MAC supports the following features:

- · Automatic TX Mode for packet framing and CRC32 insertion.

- Raw TX Mode for bit level packet control.

- Automatic GoodCRC response to received messages.

- Automatic BIST Error Count Message in BIST RX Mode.

- · GoodCRCTimer implementation.

- · Automatic retries with programmable retry count.

- · Redundant receive packets automatically dropped in auto response mode.

- · 74 byte TX queue.

- · 128 byte RX queue.

- Programmable TX Bit-time. Allows for changing operating frequency.

- · Programmable preamble length.

- · BIST TX and RX logic.

- Programmable TX and RX queue modes buffer mode and FIFO mode.

- · CRC32 generator for TX.

- · CRC32 calculator and comparator for RX.

#### 4.5.1 PD MAC TRANSMITTER

The PD MAC transmitter is comprised of three major blocks:

#### • TX Queue:

The TX Queue is where software loads the message to be transmitted.

#### • TX Control:

The TX Control implements the necessary control logic. It is responsible for reading the data from the TX queue and based on the data processing mode (automatic or raw), processing the data to make it suitable (nibbles with control information) for use by the TX Comm. It is also responsible for generating packet framing and terminating the packet in automatic mode, and generating messages for automatic response (GoodCRC and BIST Error Count). TX Control also handles the selection of the SOP type that is to be transmitted.

#### TX Comm:

The TX Comm is comprised of a TX CRC generator, a 4b5b encoder, serializer, preamble generator, and TX bit timer. It takes the nibble data, computes and inserts the CRC, 5b encodes, and generates the baseband serial data. Preamble insertion is also performed by this logic.

### 4.5.2 PD MAC RECEIVER

The PD MAC receiver is comprised of three major blocks:

#### RX Queue:

The RX Queue is where software reads the received messages.

#### RX Control:

The RX Control implements the necessary control logic. It is responsible for validating the received packet, updating the RX Queue status, and triggering automatic responses, if required.

#### RX Comm:

The RX Comm is comprised of the Clock and Data Recovery (CDR), RX DES (de-serializer) (serial-to-parallel converter, 4b5b decoder, and framing detector), RX CRC32 (CRC calculator, receive timer), and other logic to detect valid packet reception.

#### 4.5.3 PD MAC BIST

The PD MAC incorporates BIST functions as defined in the USB PD Specification. It is comprised of a TX and RX block.

The BIST TX block contains a PRBS (Pseudo Random Binary Sequence) generator, BIST pattern generation logic, and its own bit-timing logic. The SOP type used by TX BIST Test Frames is a 20-bit static vector which is created by multiplexing between the five SOP ordered sets based on a register setting. The resultant 20-bit vector is simply bit selected when the packet is transmitted.

The BIST RX block contains a PRBS generator and bit error detection logic. BIST RX is used only during the BIST Receiver Test.

# 4.6 Supported Power Delivery (PD) Functionality

This section details the UPD301A PD support in firmware. The UPD301A PD functionality operates according to the USB Power Delivery Specification. Table 4-6 details the PD parameter values used.

TABLE 4-6: USB PD VALUES

| Parameter   | Value                                                                                                                                                                                                                 |  |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| VendorID    | 0x0424                                                                                                                                                                                                                |  |

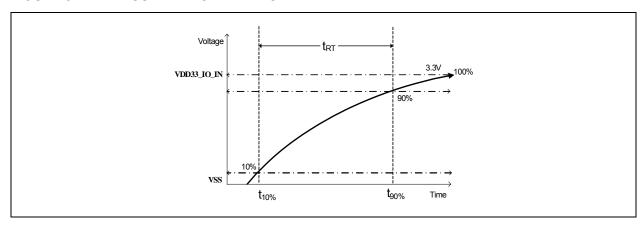

| ProductID   | 0x301A                                                                                                                                                                                                                |  |