# HMOS PARALLEL INTERFACE/TIMER

- TS68000 BUS COMPATIBLE

- PORT MODES INCLUDE:

BIT I/O

UNIDIRECTIONAL 8 BIT AND 16 BIT

BIDIRECTIONAL 8 BIT AND 16 BIT

- PROGRAMMABLE HANDSHAKING OPTIONS

- 24-BIT PROGRAMMABLE TIMER MODES

- FIVE SEPARATE INTERRUPT VECTORS

- SEPARATE PORT AND TIMER INTERRUPT SERVICE REQUESTS

- REGISTERS ARE READ/WRITE AND DIRECT-LY ADDRESSABLE

- REGISTERS ARE ADDRESSED FOR MOVEP (Move Peripheral) AND DMAC COMPATIBILITY

#### **DESCRIPTION**

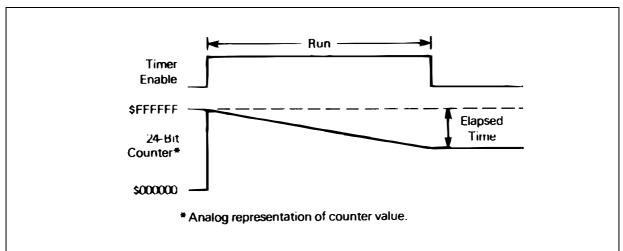

The TS68230 parallel interface/timer (PI/T) provides versatile double buffered parallel interfaces and a system oriented timer for TS68000 systems. The parallel interfaces operate in unidirectional or bidirectional modes, either 8 or 16 bits wide. In the unidirectional modes, an associated data direction register determines whether each port pin is an input or output. In the bidirectional modes the data direction registers are ignored and the direction is determined dynamically by the state of four handshake pins. These programmable handshake pins provide an interface flexible enough for connection to a wide variety of low, medium, or high speed peripherals or other computer systems. The PI/T ports allow use of vectored or auto-vectored interrupts, and also provide a DMA request pin for connection to the 68440 direct memory access controller (DMAC) or a similar circuit. The PI/T timer contains a 24-bit wide counter and a 5-bit prescaler. The timer may be clocked by the system clock (PI/T CLK pin) or by an external clock (TIN pin), and a 5-bit prescaler can be used. It can generate periodic interrupts, a square wave, or a single interrupt after a programmed time period. It can also be used for elapsed time measurement or as a device watchdog.

January 1989 1/61

#### **SECTION 1**

#### INTRODUCTION

The TS68230 parallel interface/timer (PI/T) provides versatile double buffered parallel interfaces and a system oriented timer for TS68000 systems. The parallel interfaces operate in unidirectional or bidirectional modes, either 8 or 16 bits wide. In the unidirectional modes, an associated data direction register determines whether each port pin is an input or output. In the bidirectional modes the data direction registers are ignored and the direction is determined dynamically by the state of four handshake pins. These programmable handshake pins provide an interface flexible enough for connection to a wide variety of low, medium, or high speed peripherals or other computer systems. The PI/T ports allow use of vectored or autovectored interrupts, and also provide a DMA request pin for connection to the 68440 direct memory access controller (DMAC) or a similar circuit. The PI/T timer contains a 24-bit wide counter and a 5-bit prescaler. The timer may be clocked by the system clock (PI/T CLK pin) or by an external clock (TIN pin), and a 5-bit prescaler can be used. It can generate periodic interrupts, a square wave, or a single interrupt after a programmed time period. It can also be used for elapsed time measurement or as a device watchdog.

Features of the PI/T include:

- TS68000 Bus Compatible

- Port Modes Include :

Bit I/O

Unidirectional 8 Bit and 16 Bit

Bidirectional 8 Bit and 16 Bit

- Programmable Handshaking Options

- 24-Bit Programmable Timer Modes

- Five Separate Interrupt Vectors

- Separate Port and Timer Interrupt Service Requests

- Registers are Read/Write and Directly Addressable

- Registers are Addressed for MOVEP (Move Peripheral) and DMAC Compatibility

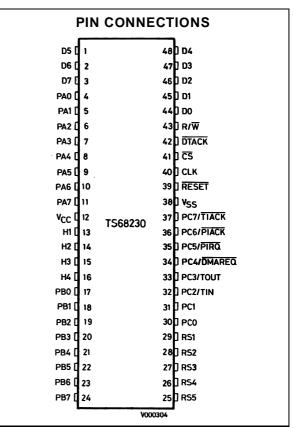

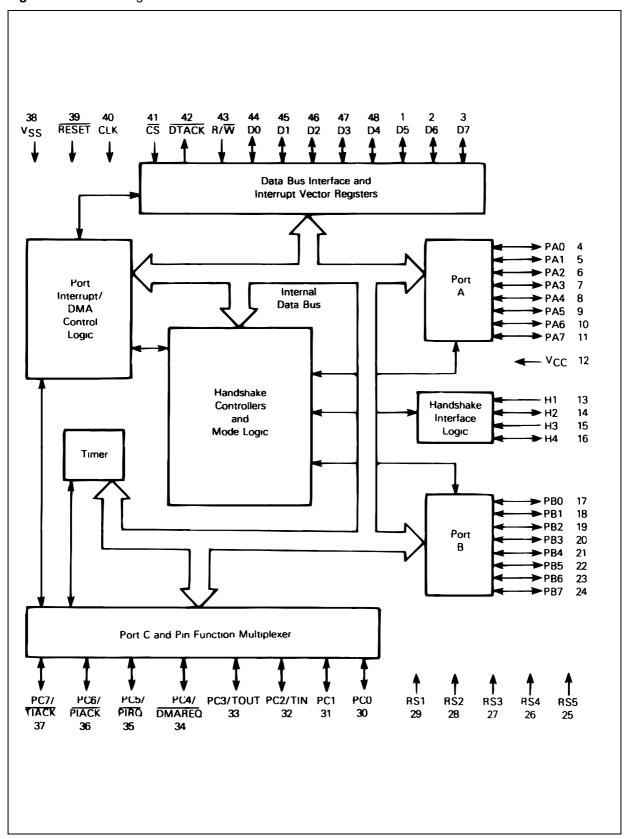

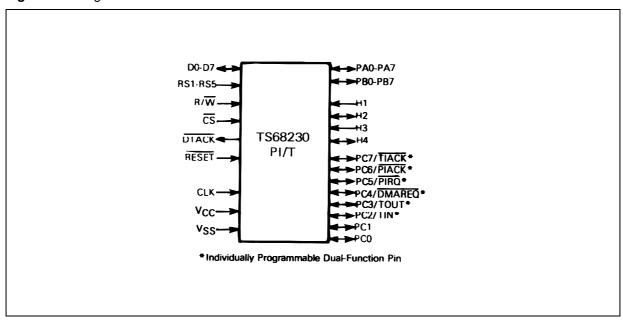

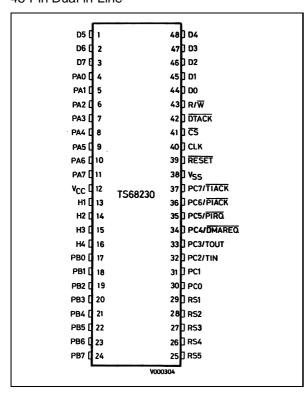

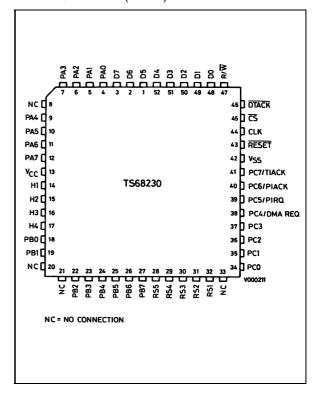

The PI/T consists of two logically independent sections: the ports and the timer. The port section consists of port A (PA0-PA7), port B (PB0-PB7), four handshake pins (H1, H2, H3, and H4), two general input/output (I/O) pins, and six dual-function pins. The dual-function pins can individually operate as a third port (port C) or an alternate function related to either port A, port B, or the timer. The four programmable handshake pins, depending on the mode, can control data transfer to and from the ports, or can be used as interrupt generating inputs or I/O pins. Refer to figure 1.1.

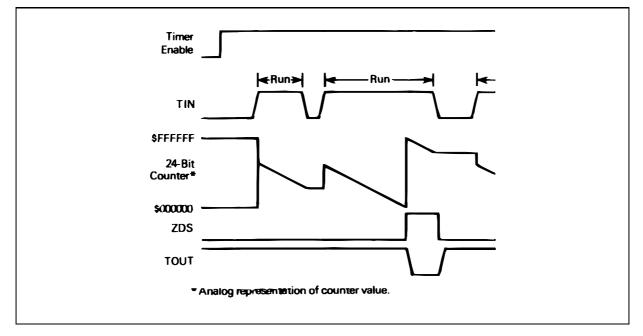

The timer consists of a 24-bit counter, optionally clocked by a 5-bit prescaler. Three pins provide complete timer I/O: PC2/TIN, PC3/TOUT, and PC7/TIACK. Only the ones needed for the given configuration perform the timer function, while the others remain port C I/O.

The system bus interface provides for asynchronous transfer of data from the PI/T to a bus master over the data bus (D0-D7). Data transfer acknowledge (DTACK), register selects (RS1-RS5), timer interrupt acknowledge (TIACK), read/write line (R/W), chip select (CS), or port interrupt acknowledge (PIACK) control data transfer between the PI/T and an TS68000.

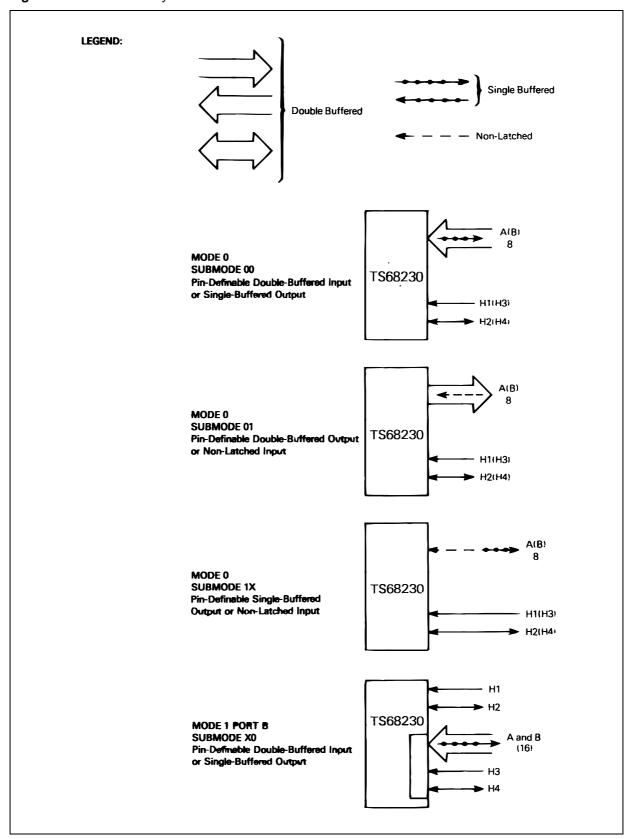

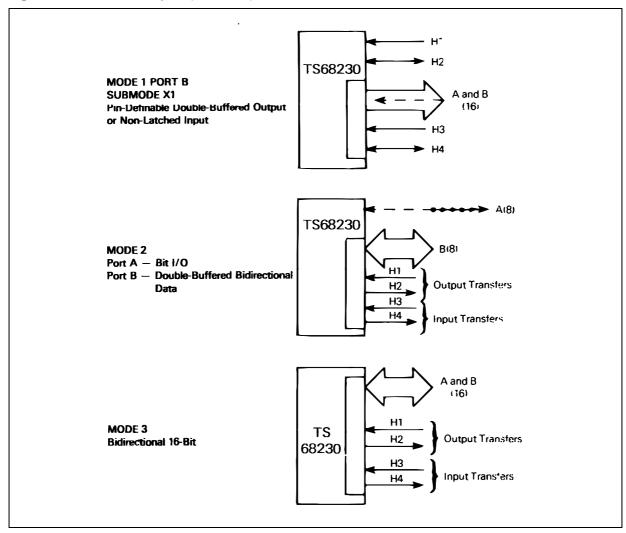

## 1.1. PORT MODE DESCRIPTION

The primary focus of most applications will be on port A, port B, the handshake pins, the port interrupt pins, and the DMA request pin. They are controlled in the following way: the port general control register contains a 2-bit field that specifies one of four operation modes. These govern the overall operation of the ports and determine their interrelation-ships. Some modes require additional information from each port's control register to further define its operation. In each port control register, there is a 2-bit submode field that serves this purpose. Each port mode/submode combination specifies a set of programmable characteristics that fully define the behavior of that port and two of the handshake pins. This structure is summarized in table 1.1 and figure 1.2.

Figure 1.1 : Block Diagram.

#### Table 1.1: Port Mode Control Summary.

#### Mode 0 (unidirectional 8-bit mode)

Port A

Submode 00 - Pin-definable Double-buffered Input or Single-buffered Output

H1 - Latches Input Data

H2 - Status/interrupt Generating Input, General-purpose Output, or Operation with H1 in the Interlocked or Pulsed Handshake Protocols

Submode 01 - Pin-definable Double-buffered Output or Non-latched Input

H1 - Indicates Data Received by Peripheral

H2 - Status/interrupt Generating Input, General-purpose Output, or Operation with H1 in the Interlocked or Pulsed Handshake Protocols

Submode 1X - Pin-definable Single-buffered Output or non-latched Input

H1 - Status/interrupt Generating Input

H2 - Status/interrupt Generating Input or General-purpose Output

Port B

H3 and H4 - Identical to Port A, H1 and H2

#### **Mode 1** (unidirectional 16-bit mode)

Port A - Most-significant Data Byte or non-latched Input or Single-buffered Output

Submode XX - (not used)

H1 - Status/interrupt Generating Input

H2 - Status/interrupt Generating Input or General-purpose Output

Port B - Least-significant Data Byte

Submode X0 - Pin-definable Double-buffered Input or Single-buffered Output

H3 - Latches Input Data

H4 - Status/interrupt Generating Input, General-purpose Output, or Operation with H3 in the Interlocked or pulsed handshake Protocols

Submode X1 - Pin-definable Double-buffered Output or Non-latched Input

H3 - Indicates Data Received by Peripheral

H4 - Status/interrupt Generating Input, General-purpose Output, or Operation with H3 in the Interlocked or Pulsed Hanshake Protocols

## Mode 2 (bidirectional 8-bit mode)

Port A - Bit I/O

Submode XX - (not used)

Port B - Double-buffered Bidirectional Data

Submode XX - (not used)

H1 - Indicates Output Data Received by the Peripheral and Controls Output Drivers

H2 - Operation with H1 in the Interlocked or Pulsed Output Handshake Protocols

H3 - Latches Input Data

H4 - Operation with H3 in the Interlocked or Pulsed Input Handshake Protocols

#### Mode 3 (bidirectional 16-bit mode)

Port A - Double-buffered Bidirectional Data (most-signifiant data byte)

Submode XX - (not used)

Port B - Double-buffered Bidirectional Data (least-signifiant data byte)

Submode XX - (not used)

H1 - Indicates Output Data Received by the Peripheral and Controls Output Drivers

H2 - Operation with H1 in the Interlocked or Pulsed Output Handshake Protocols

H3 - Latches Input Data

H4 - Operation with H3 in the Interlocked or Pulsed Input Handshake Protocols

Figure 1.2 : Port Mode Layout.

Figure 1.2: Port Mode Layout (continued).

#### 1.2. SIGNAL DESCRIPTION

Throughout this data sheet, signals are presented using the terms active and inactive or asserted and negated independent of whether the signal is active in the high-voltage state or low-voltage state. (The active state of each logic pin is given below). Active low signals are denoted by a superscript bar. R/W indicates a write is active low and a read active high. Table 1.2 further describes each pin and the logical pin assignments are given in figure 1.3.

- 1.2.1. BIDIRECTIONAL DATA BUS (D0-D7). The data bus pins D0-D7 form an 8-bit bidirectional data bus to/from an TS68000 bus master. These pins are active high.

- 1.2.2. REGISTER SELECTS (RS1-RS5). The register select pins, RS1-RS5, are active high high-impedance inputs that determine which of the 23 internal registers is being selected. They are provided by the TS68000 bus master or other bus master.

Table 1.2: Signal Summary.

| Signal Name                      | Input/Output                     | Active State         | Edge/Level<br>Sensitive    | OutputStates               |

|----------------------------------|----------------------------------|----------------------|----------------------------|----------------------------|

| CLK                              | Input                            |                      | Falling and Rising<br>Edge |                            |

| CS                               | Input                            | Low                  | Level                      |                            |

| D0-D7                            | Input/output                     | High = 1, Low = 0    | Level                      | High, Low, High Impedance  |

| DMAREQ                           | Output                           | Low                  |                            | High, Low                  |

| DTACK                            | Output                           | Low                  |                            | High, Low, High Impedance* |

| H1(H3)***                        | Input                            | Low or High          | Asserted Edge              |                            |

| H2(H4)**                         | Input or Output                  | Low or High          | Asserted Edge              | High, Low, High Impedance  |

| PA0-PA7**, PB0-PB7**,<br>PC0-PC7 | Input/output,<br>Input or Output | High = 1, Low = 0    | Level                      | High, Low, High Impedance  |

| PIACK                            | Input                            | Low                  | Level                      |                            |

| PIRQ                             | Output                           | Low                  |                            | Low, High Impedance*       |

| RS1-RS5                          | Input                            | High = 1, Low = 0    | Level                      |                            |

| R/W                              | Input                            | High Read, Low Write | Level                      |                            |

| RESET                            | Input                            | Low                  | Level                      |                            |

| TIACK                            | Input                            | Low                  | Level                      |                            |

| TIN (external clock)             | Input                            |                      | Rising Edge                |                            |

| TIN (run/halt)                   | Input                            | High                 | Level                      |                            |

| TOUT (square wave)               | Output                           | Low                  |                            | High, Low                  |

| TOUT (TIRQ)                      | Output                           | Low                  |                            | Low, High Impedance*       |

<sup>\*</sup> Pullup resistors required.

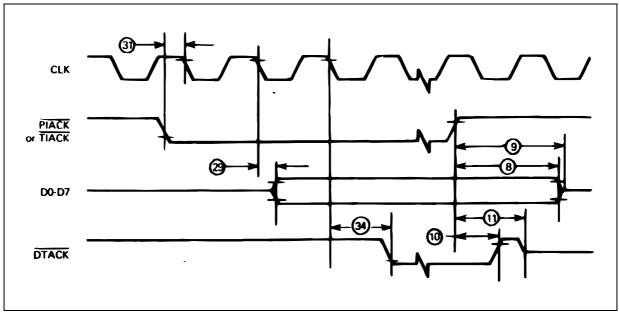

Figure 1.3: Logical Pin Connection.

<sup>\*\*</sup> Note these pins have internal pullup resistors.

- 1.2.3. READ/WRITE (R/ $\overline{W}$ ). R/ $\overline{W}$  is a high impedance read/write input signal from the TS68000 bus master, indicating whether the current bus cycle is a read (high) or write (low) cycle.

- 1.2.4. CHIP SELECT (CS). CS is a high-impedance input that selects the PI/T registers for the current bus cycle. Address strobe and the data strobe (upper or lower) of the bus master, along with the appropriate address bits, must be included in the chip-select equation. A low level corresponds to an asserted chip select.

- 1.2.5. DATA TRANSFER ACKNOWLEDGE (DTACK). DTACK is an active low output that signals the completion of the bus cycle. During read or interrupt acknowledge cycles, DTACK is asserted after data has been provided on the data bus; during write cycles it is asserted after data has been accepted at the data bus. Data transfer acknowledge is compatible with the TS68000 and with other TS68000 bus masters such as the 68440 direct memory access controller (DMAC). A pullup resistor is required to maintain DTACK high between bus cycles.

- 1.2.6. RESET (RESET). RESET is a high-impedance input used to initialize all PI/T functions. All control and data direction registers are cleared and most internal operations are disabled by the assertion of RESET (low).

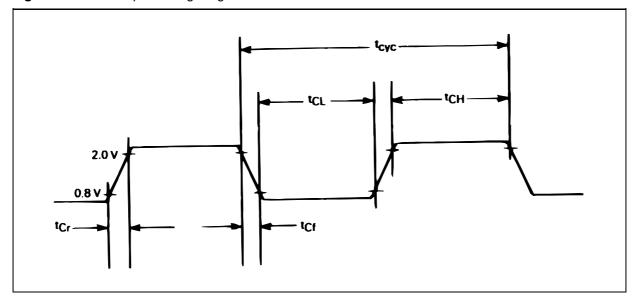

- 1.2.7. CLOCK (CLK). The clock pin is a high-impedance TTL-compatible signal with the same specifications as the TS68000. The PI/T contains dynamic logic throughout, and hence this clock must not be gated off at any time. It is not necessary that this clock maintain any particular phase relationship with the TS68000 system clock. It may be connected to an independent frequency source (faster or slower) as long as all bus specifications are met.

- 1.2.8. PORT A AND PORT B (PA0-PA7 AND PB0-PB7). Ports A and B are 8-bit ports that may be concatenated to form a 16-bit port in certain modes. The ports may be controlled in conjunction with the

- handshake pins H1-H4. For stabilization during system power up, ports A and B have internal pullup resistors to  $V_{CC}$ . All ports pins are active high.

- 1.2.9. HANDSHAKE PINS (H1-H4). Handshake pins H1-H4 are multi-purpose pins that (depending on the operational mode) may provide an interlocked handshake, a pulsed handshake, an interrupt input (independent of data transfers), or simple I/O pins. For stabilization during system power up, H2 and H4 have internal pullup resistors to  $V_{\rm CC}$ . The sense of H1-H4 (active high or low) may be programmed in the port general control register bits 3-0. Independent of the mode, the instantaneous level of the handshake pins can be read from the port status register.

- 1.2.10. PORT C (PC0-PC7/ALTERNATE FUNCTION). This port can be used as eight general purpose I/O pins (PC0-PC7) or any combination of six special function pins and two general purpose I/O pins (PC0-PC1). Each dual-function pin can be a standard I/O or a special function independent of the other port C pins. When used as a port C pin, these pins are active high. They may be individually programmed as inputs or outputs by the port C data direction register. The dual-function pins are defined in the following paragraphs.

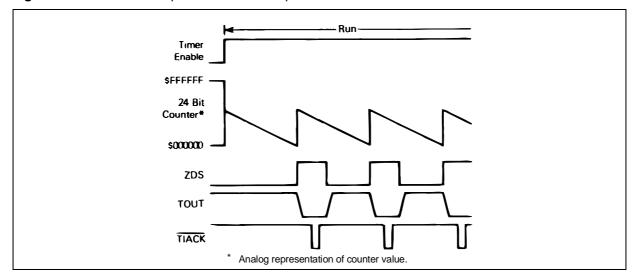

The alternate functions TIN, TOUT, and TIACK are timer I/O pins. TIN may be used as a rising-edge triggered external clock input or an external run/halt control pin (the timer is in the run state if run/halt is high and in the halt state if run/halt is low). TOUT may provide an active low timer interrupt request output or a general-purpose square-wave output, initially high. TIACK is an active low high-impedance input used for timer interrupt acknowledge.

Port A and B functions have <u>an independent pair of active low interrupt request (PIRQ)</u> and interrupt acknowledge (PIACK) pins.

The DMAREQ (direct memory access request) pin provides an active low direct memory access controller request pulse for three clock cycles, completely compatible with the 68440 DMAC.

# 1.3. REGISTER MODEL

A register model that includes the corresponding register selects is shown in table 1.3.

Table 1.3: Register Model.

| ; |   | _ | ster<br>Bit |   |             |                           |               |               |             |                     |                          |                    | Register<br>Value<br>after<br>RESET<br>(hex |                                   |

|---|---|---|-------------|---|-------------|---------------------------|---------------|---------------|-------------|---------------------|--------------------------|--------------------|---------------------------------------------|-----------------------------------|

| 5 | 4 | 3 | 2           | 1 | 7           | 6                         | 5             | 4             | 3           | 2                   | 1                        | 0                  | value)                                      |                                   |

| 0 | 0 | 0 | 0           | 0 |             | Mode<br>ntrol             | H34<br>Enable | H12<br>Enable | H4<br>Sense | H3<br>Sense         | H2<br>Sense              | H1<br>Sense        | 0 0                                         | Port General<br>Control Register  |

| 0 | 0 | 0 | 0           | 1 | V           |                           | CRQ<br>ect    | IF<br>Sel     | PF<br>ect   | l                   | ort Interru<br>ority Con | •                  | 0 0                                         | Port Service<br>Request Register  |

| 0 | 0 | 0 | 1           | 0 | Bit<br>7    | Bit<br>6                  | Bit<br>5      | Bit<br>4      | Bit<br>3    | Bit<br>2            | Bit<br>1                 | Bit<br>0           | 0 0                                         | Port A Data<br>Direction Register |

| 0 | 0 | 0 | 1           | 1 | Bit<br>7    | Bit<br>6                  | Bit<br>5      | Bit<br>4      | Bit<br>3    | Bit<br>2            | Bit<br>1                 | Bit<br>0           | 0 0                                         | Port B Data<br>Direction Register |

| 0 | 0 | 1 | 0           | 0 | Bit<br>7    | Bit<br>6                  | Bit<br>5      | Bit<br>4      | Bit<br>3    | Bit<br>2            | Bit<br>1                 | Bit<br>0           | 0 0                                         | Port C Data<br>Direction Register |

| 0 | 0 | 1 | 0           | 1 |             | Interrupt Vector V Number |               |               |             |                     |                          |                    | 0 F                                         | Port Interrupt<br>Vector Register |

| 0 | 0 | 1 | 1           | 0 | _           | Port A H2 Control Submode |               |               |             | H2<br>Int<br>Enable | H1<br>SVCRQ<br>Enable    | H1<br>Stat<br>Ctrl | 0 0                                         | Port A Control<br>Register        |

| 0 | 0 | 1 | 1           | 1 |             | rt B<br>node              | F             | 14 Contro     | ol          | H4<br>Int<br>Enable | H3<br>SVCRQ<br>Enable    | H3<br>Stat<br>Ctrl | 0 0                                         | Port B Control<br>Register        |

| 0 | 1 | 0 | 0           | 0 | Bit<br>7    | Bit<br>6                  | Bit<br>5      | Bit<br>4      | Bit<br>3    | Bit<br>2            | Bit<br>1                 | Bit<br>0           | VV                                          | Port A Data<br>Register           |

| 0 | 1 | 0 | 0           | 1 | Bit<br>7    | Bit<br>6                  | Bit<br>5      | Bit<br>4      | Bit<br>3    | Bit<br>2            | Bit<br>1                 | Bit<br>0           | VV                                          | Port B Data<br>Register           |

| 0 | 1 | 0 | 1           | 0 | Bit<br>7    | Bit<br>6                  | Bit<br>5      | Bit<br>4      | Bit<br>3    | Bit<br>2            | Bit<br>1                 | Bit<br>0           | VVV                                         | Port A Alternate<br>Register      |

| 0 | 1 | 0 | 1           | 1 | Bit<br>7    | Bit<br>6                  | Bit<br>5      | Bit<br>4      | Bit<br>3    | Bit<br>2            | Bit<br>1                 | Bit<br>0           | VVV                                         | Port B Alternate<br>Register      |

| 0 | 1 | 1 | 0           | 0 | Bit<br>7    | Bit<br>6                  | Bit<br>5      | Bit<br>4      | Bit<br>3    | Bit<br>2            | Bit<br>1                 | Bit<br>0           | VVVV                                        | Port C Data<br>Register           |

| 0 | 1 | 1 | 0           | 1 | H4<br>Level | H3<br>Level               | H2<br>Level   | H1<br>Level   | H4S         | H3S                 | H2S                      | H1S                | VVVV                                        | Port Status<br>Register           |

| 0 | 1 | 1 | 1           | 0 | V           | V                         | V             | V             | V           | V                   | V                        | V                  | 0 0                                         | (null)                            |

| 0 | 1 | 1 | 1           | 1 | V           | V                         | V             | V             | V           | V                   | V                        | V                  | 0 0                                         | (null)                            |

<sup>\*</sup> Unused, read as zero.

<sup>\*\*</sup> Value before  $\overline{\text{RESET}}$ .

<sup>\*\*\*</sup> Current value on pins.

Table 1.3: Register Model (continued).

| ; | Register<br>Select Bits |   |   |   |                       |           |             |           |           |              |                 |           | Register<br>Value<br><u>after</u><br>RESET<br>(hex |                                    |

|---|-------------------------|---|---|---|-----------------------|-----------|-------------|-----------|-----------|--------------|-----------------|-----------|----------------------------------------------------|------------------------------------|

| 5 | 4                       | 3 | 2 | 1 | 7                     | 6         | 5           | 4         | 3         | 2            | 1               | 0         | value)                                             |                                    |

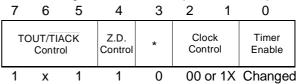

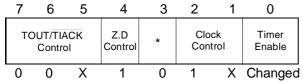

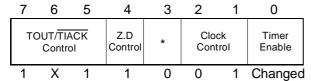

| 1 | 0                       | 0 | 0 | 0 | TOUT/TIACK<br>Control |           | Z D<br>Ctrl | <b>V</b>  |           | ock<br>ntrol | Timer<br>Enable | 0 0       | Timer Control<br>Register                          |                                    |

| 1 | 0                       | 0 | 0 | 1 | Bit<br>7              | Bit<br>6  | Bit<br>5    | Bit<br>4  | Bit<br>3  | Bit<br>2     | Bit<br>1        | Bit<br>0  | 0 F                                                | Timer Interrupt<br>Vector Register |

| 1 | 0                       | 0 | 1 | 0 | V                     | V         | V           | V         | V         | V            | V               | V         | 0 0                                                | (null)                             |

| 1 | 0                       | 0 | 1 | 1 | Bit<br>23             | Bit<br>22 | Bit<br>21   | Bit<br>20 | Bit<br>19 | Bit<br>18    | Bit<br>17       | Bit<br>16 | VV                                                 | Counter Preload<br>Register (high) |

| 1 | 0                       | 1 | 0 | 0 | Bit<br>15             | Bit<br>14 | Bit<br>13   | Bit<br>12 | Bit<br>11 | Bit<br>10    | Bit<br>9        | Bit<br>8  | VV                                                 | Counter Preload<br>Register (mid)  |

| 1 | 0                       | 1 | 0 | 1 | Bit<br>7              | Bit<br>6  | Bit<br>5    | Bit<br>4  | Bit<br>3  | Bit<br>2     | Bit<br>1        | Bit<br>0  | VV                                                 | Counter Preload<br>Register (low)  |

| 1 | 0                       | 1 | 1 | 0 | V                     | V         | V           | V         | V         | V            | V               | \<br>\    | 0 0                                                | (null)                             |

| 1 | 0                       | 1 | 1 | 1 | Bit<br>23             | Bit<br>22 | Bit<br>21   | Bit<br>20 | Bit<br>19 | Bit<br>18    | Bit<br>17       | Bit<br>16 | VV                                                 | Count Register (high)              |

| 1 | 1                       | 0 | 0 | 0 | Bit<br>15             | Bit<br>14 | Bit<br>13   | Bit<br>12 | Bit<br>11 | Bit<br>10    | Bit<br>9        | Bit<br>8  | VV                                                 | Count Register (mid)               |

| 1 | 1                       | 0 | 0 | 1 | Bit<br>7              | Bit<br>6  | Bit<br>5    | Bit<br>4  | Bit<br>3  | Bit<br>2     | Bit<br>1        | Bit<br>0  | VV                                                 | Count Register (low)               |

| 1 | 1                       | 0 | 1 | 0 | V                     | V         | V           | V         | V         | V            | V               | ZDS       | 0 0                                                | Timer Status<br>Register           |

| 1 | 1                       | 0 | 1 | 1 | V                     | V         | V           | V         | V         | V            | V               | V         | 0 0                                                | (null)                             |

| 1 | 1                       | 1 | 0 | 0 | V                     | V         | V           | V         | V         | V            | V               | V         | 0 0                                                | (null)                             |

| 1 | 1                       | 1 | 0 | 1 | V                     | V         | V           | V         | V         | V            | V               | V         | 0 0                                                | (null)                             |

| 1 | 1                       | 1 | 1 | 0 | V                     | V         | V           | V         | V         | V            | V               | V         | 0 0                                                | (null)                             |

| 1 | 1                       | 1 | 1 | 1 | V                     | V         | V           | V         | V         | V            | V               | V         | 0 0                                                | (null)                             |

<sup>\*</sup> Unused, read as zero.

#### 1.4. BUS INTERFACE OPERATION

The PI/T has an asynchronous bus interface primarily designed for use with an TS68000 microprocessor. With care, however, it can be connected to synchronous microprocessor buses. This section completely describes the PI/T's bus interface, and is intended for the asynchronous bus designer unless otherwise mentioned.

In an asynchronous system the PI/T clock may operate at a significantly different frequency, either higher or lower, than the bus master and other system components, as long as all bus specifications are met. The TS68230 CLK pin has the same specifications as the TS68000 CLK pin, and must not be gated off at any time.

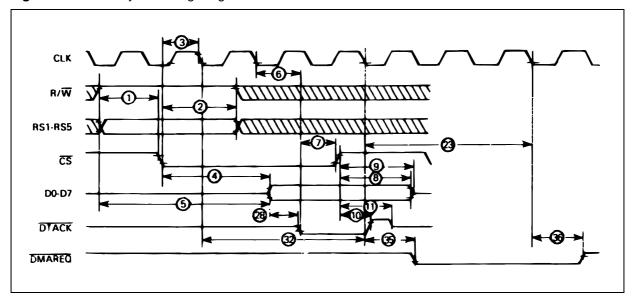

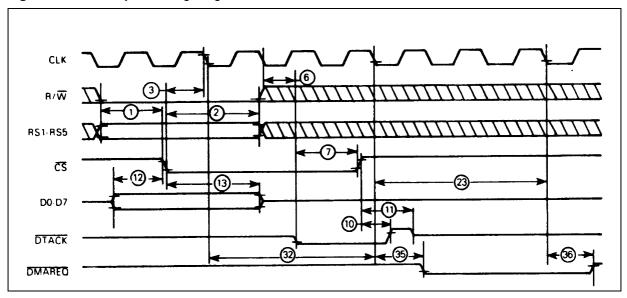

The following signals generate normal read and write cycles to the PI/T: CS (chip select), R/W (read/write), RS1-RS5(five register select bits), D0-D7 (the 8-bit bidirectional data bus), and DTACK (data transfer acknowledge). To generate interrupt acknowledge cycles, PC6/PIACK or PC7/TIACK is used instead of CS, and the register select pins are ignored. No combination of the following pin functions may be asserted simultaneously: CS, PIACK, or TIACK.

1.4.1. READ CYCLES. This category includes all register reads, except <u>port</u> or timer interrupt acknowledge cycles. When CS is asserted, the register select and R/W inputs are latched internally. They must meet small setup and hold time <u>requirements</u> with respect to the asserted edge of CS. (Refer to **6.6 AC Electrical Specifications** for further information). The PI/T is **not** protected against aborted (shortened) bus cycles generated by an address error or bus error exception in which it is addressed.

Certain operations triggered by normal read (or write) bus cycles are not complete within the time allotted to the bus cycle. One example is transfers to/from the double-buffered latches that occur as a result of the bus cycle. If the bus master's clock is significan-tly faster than the PI/T's the possibility exists that, following the bus cycle, CS can be negated then re-asserted before completion of these internal operations. In this situation the PI/T does not recognize the re-assertion of CS until these operations are complete. Only at that time does it begin the internal sequencing necessary to react to the asserted CS. Since CS also controls the DTACK response, this "bus cycle recovery time" can be related to the clock edge on which DTACK is asserted for that cycle. The PI/T will recognize the subsequent assertion of CS three clock periods after the clock edge on which DTACK was previously asserted.

The register select and R/W inputs pass through an internal latch that is transparent when the PI/T can recognize a new CS pulse (see above paragraph). Since the internal data bus of the PI/T is continuously engaged for read transfers, the read access time (to the data bus buffers) begins when the register selects are stabilized internally. Also, when the PI/T is ready to begin a new bus cycle, the assertion of CS enables the data bus buffers within a short propagation delay. This does not contribute to the overall read access time unless CS is asserted significantly after the register select and R/W inputs are stabilized (as may occur with synchronous bus microprocessors).

In addition to the chip select's previously mentioned duties, it controls the assertion of DTACK and latching of read data at the data bus interface. Except for controlling input latches and enabling the data bus buffers, all of these functions occur only after CS has been recognized internally and synchronized with the internal clock. Chip select is recognized on the falling edge of the clock if the setup time is met; DTACK is asserted (low) on the next falling edge of the clock. Read data is latched at the PI/T's data bus interface at the same time DTACK is asserted. It is stable as long as chip select remains asserted independent of other external conditions.

From the above discussion it is clear that if the chip select setup time prior to the falling edge of the clock is met, the PI/T can consistently respond to a new read or write bus cycle every four clock cycles. This fact is especially useful in designing the <u>PI/T's clock</u> in synchronous bus systems not using DTACK. (An extra clock period is required in interrupt acknowledge cycles, see **1.4.2 Interrupt Acknowledge Cycles**).

In asynchronous bus systems in which the PI/T's clock differs from that of the bus master, generally there is no way to guarantee that the chip select setup time with respect to the PI/T clock is met. Thus, the only way to determine that the PI/T recognized the assertion of CS is to wait for the assertion of DTACK. In this situation, all latched bus inputs to the PI/T must be held stable until DTACK is asserted. These include register select, R/W, and write data inputs (see below).

System specifications impose a maximum delay from the trailing (negated) edge of CS to the negated edge of DTACK. As system speeds increase this becomes more difficult to meet with a simple pullup resistor tied to the DTACK line. Therefore, the PI/T provides an internal active pullup device to reduce the rise time, and a level-sensitive circuit that later turns this device off. DTACK is negated asynchronously as fast as possible following the rising edge

of chip select, then three-stated to avoid interference with the next bus cycle.

The system designer must take care that DTACK is negated and three-stated quickly enough after each bus cycle to avoid interference with the next one. With an TS68000 this necessitates a relatively fast external path from the data strobe negation to CS bus master negation.

1.4.2. INTERRUPT ACKNOWLEDGE CYCLES. Special internal operations take place on PI/T interrupt acknowledge cycles. The port interrupt vector register or the timer vector register are implicitly addressed by the assertion of PC6/PIACK or PC7/TIACK, respectively. The signals are first synchronized with the falling edge of the clock. One clock period after they are recognized, the data bus

buffe<u>rs are enabled</u> and the vector is driven onto the bus. DTACK is asserted after another cloc<u>k period to allow</u> the vector some setup time prior to DTACK. DTACK is negated, then three-<u>stated</u>, as <u>with normal read</u> or write cycles, when PIACK or TIACK is negated.

1.4.3. WRITE CYCLES. In many ways, write cycles are similar to normal read cycles. On write cycles, data at the D0-D7 pins must meet the same setup specifications as the register select and R/W lines. Like these signals, write data is latched on the asserted edge of CS, and must meet small setup and hold time requirements with respect to that edge. The same bus cycle recovery conditions exist as for normal read cycles. No other differences exist.

#### **SECTION 2**

# PORT GENERAL INFORMATION AND CONVENTIONS

This section introduces concepts that are generally applicable to the PI/T ports independent of the chosen mode and submode. For this reason, no particular port or handshake pins are mentioned; the notation H1(H3) indicates that, depending on the chosen mode and submode, the statement given may be true for either the H1 or H3 handshake pin.

#### 2.1. UNIDIRECTIONAL VS BIDIRECTIONAL

Figure 1.2 shows the configuration of ports A and B and each of the handshake pins in each port mode and submode. In modes 0 and 1, a data direction register is associated with each of the ports. These registers contain one bit for each port pin to determine whether that pin is an input or an output. Modes 0 and 1 are, thus, called unidirectional modes because each pin assumes a constant direction, changeable only by a reset condition or a programming change. These modes allow double-buffered data transfers in one direction. This direction, determined by the mode and submode definition, is known as the primary direction. Data transfers in the primary direction are controlled by the handshake pins. Data transfers not in the primary direction are generally unrelated, and single or unbuffered data paths exist.

In modes 2 and 3 there is no concept of primary direction as in modes 0 and 1. Except for port A in mode 2 (bit I/O), the data direction registers have no effect. These modes are bidirectional, in that the direction of each transfer (always 8 or 16 bits, double buffered) is determined dynamically by the state of the handshake pins. Thus, for example, data may be transferred out of the ports, followed very shortly by a transfer into the same port pins. Transfers to and from the ports are independent and may occur in any sequence. Since the instantaneous direction is always determined by the external system, a small amount of arbitration logic may be required.

2.1.1. CONTROL OF DOUBLE-BUFFERED DATA PORTS. Generally speaking, the PI/T is a double-buffered device. In the primary direction, double buffering allows orderly transfers by using the handshake pins in any of several programmable protocols. (When bit I/O is used, double buffering is not available and the handshake pins are used as outputs or status/interrupt inputs).

Use of double buffering is most beneficial in situations where a peripheral device and the computer system are capable of transferring data at roughly the same speed. Double buffering allows the fetch operation of the data transmitter to be overlapped with the store operation of the data receiver. Thus, throughput measured in bytes or words-per-second may be greatly enhanced. If there is a large mismatch in transfer capability between the computer and the peripheral, little or no benefit is obtained. In these cases there is no penalty in using double buffering.

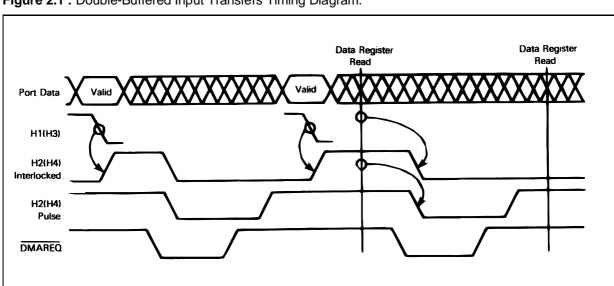

2.1.2. DOUBLE-BUFFERED INPUT TRANSFERS. In all modes, the PI/T supports double-buffered input transfers. Data that meets the port setup and hold times is latched on the asserted edge of H1(H3). H1(H3) is edge sensitive, and may assume any duty cycle as long as both high and low minimum times are observed. The PI/T contains a port status register whose H1S(H3S) status bit is set anytime any input data that has not been read by the bus master is present in the double-buffered latches. The action of H2(H4) is programmable; it may indicate whether there is room for more data in the PI/T latches or it may serve other purposes. The following options are available, depending on the mode.

- 1. H2(H4) may be an edge-sensitive input that is independent of H1(H3) and the transfer of port data. On the asserted edge of H2(H4), the H2S(H4S) status bit is set. It is cleared by the direct method (refer to 2.3 Direct Method of Resetting Status), the RESET pin being asserted, or when the H12 enable (H34 enable) bit of the port general control register is zero.

- 2. H2(H4) may be a general purpose output pin that is always negated. The H2S(H4S) status bit is always zero.

- 3. H2(H4) may be a general purpose output pin that is always asserted. The H2S(H4S) status bit is always zero.

- 4. H2(H4) may be an output pin in the interlocked input handshake protocol. It is asserted when the port input latches are ready to accept new data. It is negated asynchronously following the asserted edge of the H1(H3) input. As soon as the input latches become ready, H2(H4) is again asserted. When both double-buffered latches are full, H2(H4) remains negated until data is removed by a read of port A (port B) data register. Thus, anytime the H2(H4) output is asserted, new input data may be entered by asserting H1(H3). At other times transitions of H1(H3) are ignored. The H2S(H4S) status bit is always zero. When H12 enable (H34 enable) is zero, H2(H4) is held negated.

- 5. H2(H4) may be an output pin in the pulsed input handshake protocol. It is asserted exactly as in the interlocked input protocol, but never remains asserted longer than four clock cycles. Typically, a four clock cycle pulse is generated. But in the case that a subsequent H1(H3) asserted edge occurs before termination of the pulse, H2(H4) is negated asynchronously. Thus, anytime after the leading edge of the H2(H4) pulse, new data may be entered in the PI/T double-buffered input latches. The H2S(H4S) status bit is always zero. When H12 enable (H34 enable) is zero, H2(H4) is held negated.

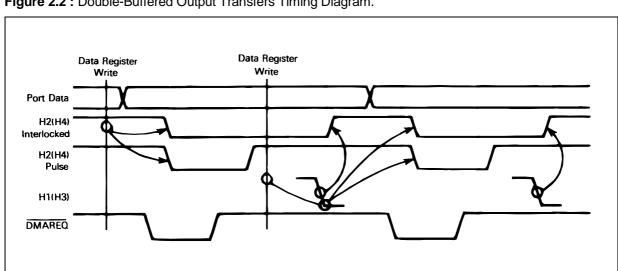

- 2.1.3. DOUBLE-BUFFERED OUTPUT TRANS-FERS. The PI/T supports double-buffered output transfers in all modes. Data, written by the bus master to the PI/T, is stored in the port's output latch. The peripheral accepts the data by asserting H1(H3), which causes the next data to be moved to the port's output latch as soon as it is available. The function of H2(H4) is programmable; it may indicate whether data has been moved to the output latch or it may serve other purposes. The H1S(H3S) status bit may be programmed for two interpretations. First, the status bit is a one when there is at least one latch in the double-buffered data path that can accept new data. After writing one byte/word of data to the ports, an interrupt service routine could check this bit to determine if it could store another byte/word, thus filling both latches. Second, when the bus master is finished, it is often useful to be able to check whether all of the data has been transferred to the peripheral. The H1S(H3S) status bit is set when both output

latches are empty. The programmable options of the H2(H4) pin are given below, depending on the mode.

- H2(H4) may be an edge-sensitive input pin independent of H1(H3) and the transfer of port data. On the asserted edge of H2(H4), the H2S(H4S) status bit is set. It is cleared by the direct method (refer to 2.3 Direct Method of Resetting Status), the RESET pin being asserted, or when the H12 enable (H34 enable) bit of the port general control register is zero.

- 2. H2(H4) may be a general-purpose output pin that is always zero.

- 3. H2(H4) may be a general-purpose output pin that is always asserted. The H2S(H4s) status bit is always zero.

- 4. H2(H4) may be an output pin in the interlocked output handshake protocol. H2(H4) is asserted two clock cycles after data is transferred to the double-buffered output latches. The data remains stable and H2(H4) remains asserted until the next asserted edge of the H1(H3) input. At that time, H2(H4) is asynchronously negated. As soon as the next data is available, it is transferred to the output latches and H2(H4) is asserted. When H2(H4) is negated, asserted transitions on H1(H3) have no effect on the data paths. As is explained later, however, in modes 2 and 3 H1 does control the three-state output buffers of the bidirectional port(s). The H2S(H4S) status bit is always zero. When H12 enable (H34 enable) is zero, H2(H4) is held negated.

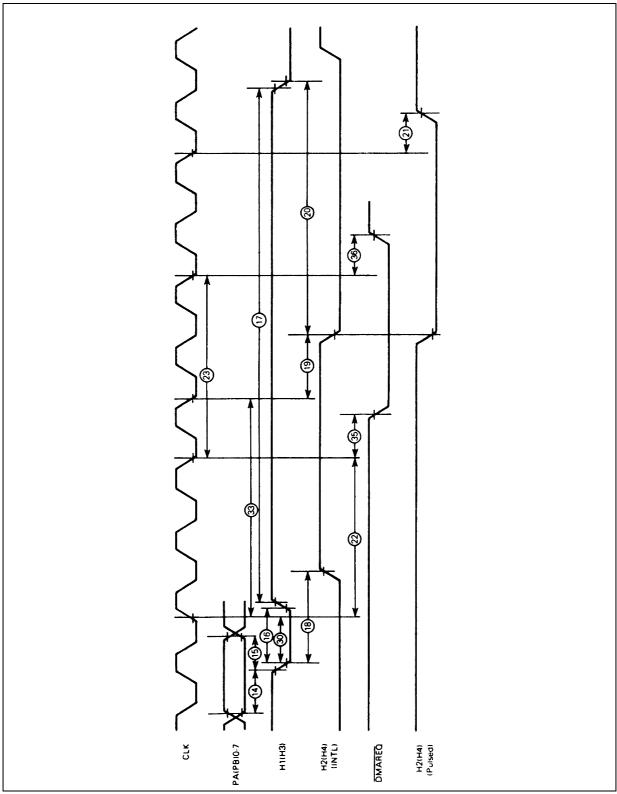

Figure 2.1: Double-Buffered Input Transfers Timing Diagram.

5. H2(H4) may be an output pin in the pulsed output handshake protocol. It is asserted exactly as in the interlocked output protocol above, but never remains asserted longer than four clock cycles. Typically, a four clock pulse is generated. But in the case that a subsequent H1(H3) asserted edge occurs before termination of the pulse, H2(H4) is negated asynchronously, thus shortening the pulse. The H2S(H4S) status bit is always zero. When H12 enable (H34 enable) is zero, H2(H4) is held negated.

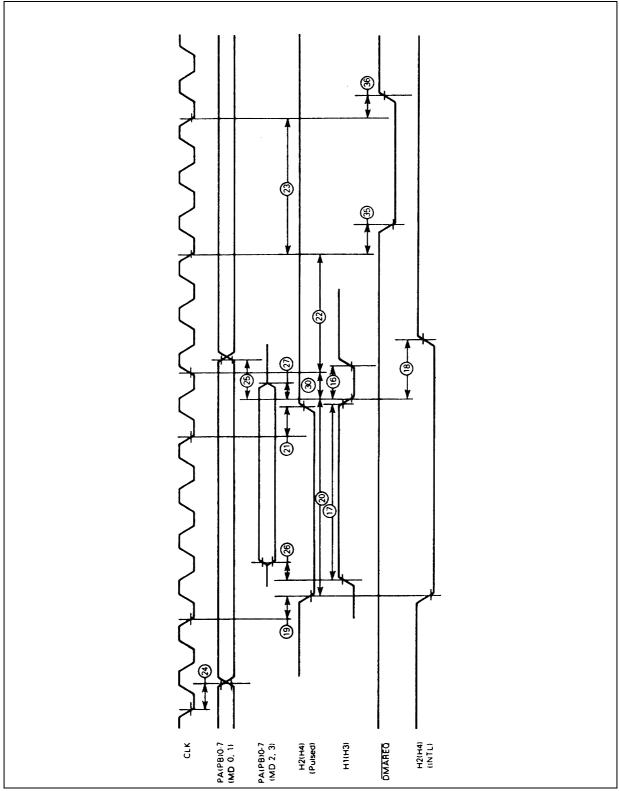

A sample timing diagram is shown in figure 2.2. The H2(H4) interlocked and pulsed output handshake protocols are shown. The DMAREQ pin is also shown assuming it is enabled. All handshake pin sense bits are assumed to be zero; thus, the pins are in the low state when asserted. Due to the great similarity between modes, this timing diagram is applicable to all double-buffered output transfers.

#### 2.2. REQUESTING BUS MASTER SERVICE

The PI/T has several means of indicating a need for service by a bus master. First, the processor may poll the port status register. It contains a status bit for each handshake pin, plus a level bit that always reflects the instantaneous state of that handshake pin. A status bit is one when the PI/T needs servicing (i.e., generally when the bus master needs to read or write data to the ports) or when a handshake pin used as a simple status input has been asserted. The interpretation of these bits is dependent on the chosen mode and submode.

Second, the PI/T may be placed in the processor's interrupt structure. As mentioned previously, the PI/T contains port A and B control registers that configure the handshake pins. Other bits in these registers enable an interrupt associated with each handshake pin. This interrupt is made available through the PC5/PIRQ pin, if the PIRQ function is selected. Three additional conditions are required for PIRQ to be asserted: 1) the handshake pin status bit is set, 2) the corresponding interrupt (service request) enable bit is set, and 3) DMA requests are not associated with that data transfer (H1 and H3 only). The conditions from each of the four handshake status bits and corresponding status bits are ORed to determine PIRQ. To clear the interrupt, the proper status bit must be cleared (see 2.3. Direct Method of Resetting Status).

The third method of requesting service is via the PC4/DMAREQ pin. This pin can be associated with double-buffered transfers in each mode. If it is used as a DMA controller request, it can initiate requests to keep the PI/T's input/output double-buffering empty/full as much as possible. It will not overrun the DMA controller. The pin is compatible with the 68440 direct memory access controller (DMAC).

2.2.1. VECTORED, PRIORITIZED PORT INTER-RUPTS. Use of TS68000 compatible vectored interrupts with the PI/T requires the PIRQ and PIACK pins. When PIACK is asserted while PIRQ is asserted, the PI/T places an 8-bit vector on the data pins D0-D7. Under normal conditions, this vector corresponds to the highest priority enabled active port interrupt source with which the DMAREQ pin is not currently associated. The most-significant six bits are provided by the port interrupt vector register (PIVR), with the lower two bits supplied by prioritization logic according to conditions present when PIACK is asserted. It is important to note that the on-

Figure 2.2: Double-Buffered Output Transfers Timing Diagram.

ly effect on the PI/T caused by interrupt acknowledge cycles is that the vector is placed on the data bus. Specifically, no registers, data, status, or other internal states of the PI/T are affected by the cycle.

Several conditions may be present when the PIACK input is asserted to the PI/T. These conditions affect the PI/T's response and the termination of the bus cycle. If the PI/T has no interrupt function selected, or is not asserting PIRQ, the PI/T will make no response to PIACK (DTACK will not be asserted). If the PI/T is asserting PIRQ when PIACK is received, the PI/T will output the contents of the port interrupt vector register and the prioritization bits. If the PIVR has not been initialized, \$0F will be read from this register. These conditions are summarized in table 2.1.

The vector table entries for the PI/T appear as a contiguous block of four vector numbers whose common upper six bits are programmed in the PIVR. The following table pairs each interrupt source with the 2-bit value provided by the prioritization logic when interrupt acknowledge is asserted (see **4.2. Port Service Request Register** (PSRR)).

2.2.2. AUTOVECTORED PORT INTERRUPTS. Autovectored interrupts use only the PIRQ pin. The operation of the PI/T with vectored and autovectored interrupts is identical except that no vectors are supplied and the PC6/PIACK pin can be used as a port C pin.

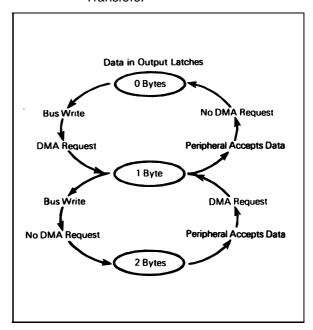

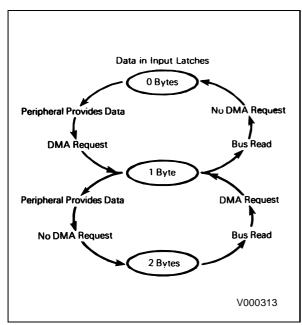

2.2.3. DMA REQUEST OPERATION. The direct memory access request (DMAREQ) pulse (when enabled) is associated with output or input transfers to keep the initial and final output latches full or initial and final input latches empty, respectively. Figures 2.3 and 2.4 show all the possible paths in generating DMA requests. See **4.2. Port Service Request Register** (PSRR) for programming the operation of the DMA request bit.

DMAREQ is generated on the bus side of the TS68230 by the synchronized\* chip select. If the conditions of figures 2.3 or 2.4 are met, an assertion of CS will cause DMAREQ to be asserted three PI/T clocks (plus the delay time from the clock edge) after CS is synchronized. DMAREQ remains asserted three clock cycles (plus the delay time from the clock edge) and is then negated.

DMAREQ pulses are associated with peripheral transfers or are generated by the synchronized\* H1(H3) input. If the conditions of figures 2.3 or 2.4 are met, an assertion of the H1(H3) input will cause DMAREQ to be asserted 2.5 PI/T clock cycles (plus the delay time from clock edge) after H1(H3) is synchronized. DMAREQ remains asserted three clock cycles (plus the delay time from the clock edge) and is then negated.

**Figure 2.3 :** DMAREQ Associated with Output Transfers.

Table 2.1: Response to Port Interrupt Acknowledge.

| Conditions                                 | PIRQ Negated OR Interrupt<br>Request Function not Selected | PIRQ Asserted                                         |  |

|--------------------------------------------|------------------------------------------------------------|-------------------------------------------------------|--|

| PIVR has not been initialized since RESET. | No Response from PI/T. No DTACK.                           | PI/T provides \$0F, the Uninitialized Vector*.        |  |

| PIVR has been initialized since RESET.     | No Response from PI/T. No DTACK.                           | PI/T provides PIVR contents with prioritization bits. |  |

<sup>\*</sup> The uninitialized vector is the value returned from an interrupt vector register before it has been initialized.

clock (rising edge for H1(H3) and falling edge for CS). Refer to 1.4 BUS INTERFACE OPERATION for the exception concer-

<sup>\*</sup> Synchronized means that the appropriate input signal (H1, H3, or CS) has been sampled by the PI/T on the appropriatre edge of the

**Figure 2.4 :** DMAREQ Associated with Input Transfers.

#### 2.3. DIRECT METHOD OF RESETTING STATUS

In certain modes one or more handshake pins can be used as edge-sensitive inputs for the sole purpose of setting bits in the port status register. These bits consist of simple flip-flops. They are set (to one) by the occurrence of the asserted edge of the handshake pin input. Resetting a handshake status bit can be done by writing an 8-bit mask to the port status register. This is called the direct method of resetting. To reset a status bit that is resettable by the direct method, the mask must contain a one in the bit position of the port status register corresponding to the desired status bit. For status bits that are not resettable by the direct method in the chosen mode, the data written to the port status register has no effect. For status bits that are resettable by the direct method in the chosen mode, a zero in the mask has no effect.

# 2.4. HANDSHAKE PIN SENSE CONTROL

The PI/T contains exclusive-OR gates to control the sense of each of the handshake pins, whether used

as inputs or outputs. Four bits in the port general control register may be programmed to determine whether the pins are asserted in the low- or high-voltage state. As with other control registers, these bits are reset to zero when the RESET pin is asserted, defaulting the asserted level to be low.

#### 2.5. ENABLING PORTS A AND B

Certain functions involved with double-buffered data transfers, the handshake pins, and the status bits may be disabled by the external system or by the programmer during initialization. The port general control register contains two bits, H12 enable and H34 enable, which control these functions. These bits are cleared to the zero state when the RESET pin is asserted, and the functions are disabled. The functions are the following:

- Independent of other actions by the bus master or peripheral (via the handshake pins), the PI/T's disabled handshake controller is held to the "empty" state; i.e., no data is present in the double-buffered data path.

- When any handshake pin is used to set a simple status flip-flop, unrelated to double-buffered transfers, these flip-flops are held reset to zero (see table 1.1).

- 3. When H2(H4) is used in an interlocked or pulsed handshake with H1(H3), H2(H4) is held negated, regardless of the chosen mode, submode, and primary direction. Thus, for double-buffered input transfers, the programmer may signal a peripheral when the PI/T is ready to begin transfers by setting the associated handshake enable bit to one.

### 2.6. PORT A AND B ALTERNATE REGISTERS

In addition to the port A and B data registers, the PI/T contains port A and B alternate registers. These registers are read only, and simply provide the ins-tantaneous (non-latched) level of each port pin. They have no effect on the operation of the hand-shake pins, double-buffered transfers, status bits, or any other aspect of the PI/T, and they are mode/submode independent. Refer to **4.7. Port Alternate Registers** for further information.

#### **SECTION 3**

# **PORT MODES**

This section contains information that distinguishes the various port modes and submodes. General characteristics common to all modes are defined in **Section 2 Port General Information and Conventions.** A description of the port A control register (PACR) and port B control register (PBCR) is given before each mode description. After each submode description, the programmable options are listed for that submode.

# 3.1. PORT A CONTROL REGISTER (PACR)

| 7           | 6 | 5  | 4 3     | 3 | 2                        | 1                     | 0                       |

|-------------|---|----|---------|---|--------------------------|-----------------------|-------------------------|

| Por<br>Subm |   | H2 | Control |   | H2<br>nterrupt<br>Enable | H1<br>SVCRQ<br>Enable | H1<br>Status<br>Control |

The port A control register, in conjunction with the programmed mode and the port B submode, controls the operation of port A and the handshake pins H1 and H2. The port A control register contains five fields: bits 7 and 6 specify the port A submode; bits 5, 4, and 3 control the operation of the H2 handshake pin and the H2S status bit; bit 2 determines whether an interrupt will be generated when the H2S status bit goes to one; and bit 1 determines whether a service request (interrupt request or DMA request) will occur; bit 0 controls the operation of the H1S status bit. The PACR is always readable and writable.

All bits are cleared to zero when the RESET pin is asserted. When the port A submode field is relevant in a mode/submode definition, it must not be altered unless the H12 enable bit in the port general control register is clear (see table 1.3 located at the end of this document). Altering these bits will give unpredictable results.

# 3.2. PORT B CONTROL REGISTER (PBCR)

| 7            | 6 | 5  | 4      | 3  | 2                         | 1                     | 0                       |

|--------------|---|----|--------|----|---------------------------|-----------------------|-------------------------|

| Port<br>Subm | _ | H4 | Contro | ol | H4<br>Interrupt<br>Enable | H3<br>SVCRQ<br>Enable | H3<br>Status<br>Control |

The port B control register specifies the operation of port B and the handshake pins H3 and H4. The port B control register contains five fields: bits 7 and 6 specify the port B submode; bits 5, 4, and 3 control the operation of the H4 handshake pin and H4S status bit; bit 2 determines whether an interrupt will be generated when the H4S status bit goes to a one; bit 1 determines whether a service request (interrupt request or DMA request) will occur; and bit 0 controls the operation of the H3S status bit. The PBCR is always readable and writable. There is never a consequence to reading the register.

All bits are cleared to zero when the RESET pin is asserted. When the port B submode field is relevant in a mode/submode definition, it must not be altered unless the H34 enable bit in the port general control register is clear (see table 1.3 located at the end of this document).

#### 3.3. MODE 0 - UNIDIRECTIONAL 8-BIT MODE

In mode 0, ports A and B operate independently. Each may be configured in any of its three possible submodes:

Submode 00 - Pin-Definable Double-Buffered Input or Single-Buffered Output

Submode 01 - Pin-Definable Double-Buffered Output or Non-Latched Input

Submode 1X - Bit I/O (Pin-Definable Single-Buffered Output or Non-Latched Input)

Handshake pins H1 and H2 are associated with port A and configured by programming the port A control register. (The H12 enable bit of the port general control register enables port A transfers). Handshake pins H3 and H4 are associated with port B and configured by programming the port B control register. (The H34 enable bit of the port general control register enables port B transfers). The port A and B data direction registers operate in all three submodes. Along with the submode, they affect the data read and write at the associated data register according to table 3.1. They also enable the output buffer associated with each port pin. The DMAREQ pin may be associated with either (not both) port A or port B, but does not function if the bit I/O submode (submode 1X) is programmed for the chosen port.

Table 3.1: Mode 0 Port Data Paths.

| Mode                         | Read Port A/B     | Data Register            | Write Port A/B Data Register |                  |  |

|------------------------------|-------------------|--------------------------|------------------------------|------------------|--|

| Wode                         | DDR = 0           |                          | DDR = X                      |                  |  |

| 0 Submode 00<br>0 Submode 01 | FIL, D. B.<br>Pin | FOL Note 3<br>FOL Note 3 | FOL, S. B.<br>IOL/FOL, D. B. | Note 1<br>Note 2 |  |

| 0 Submode 1X                 | Pin               | FOL Note 3               | FOL, S. B.                   | Note 1           |  |

Abbreviations:

IOL - Initial Output Latch

FOL - Final Output Latch

FIL - Final Input Latch

S. B. - Single Buffered

D. B. - Double Buffered

DDR - Data Direction Register

- Note 1 : Data is latched in the output data registers (final output latch) and will be single buffered at the pin if the DDR is 1. The output buffers will be turned off if the DDR is 0.

- Note 2: Data is latched in the double-buffered output data registers. The data in the final output latch will appear on the port pin if the DDR is a 1.

- Note 3: The output drivers that connect the final output latch to the pins are turned on

3.3.1. SUBMODE 00 - PIN-DEFINABLE DOUBLE-BUFFERED INPUT OR SINGLE-BUFFERED OUTPUT. In mode 0, double-buffered input transfers of up to eight bits are available by programming submode 00 in the desired port's control register. Data that meets the port setup and hold times is latched on the asserted edge of H1(H3) and is placed in the initial or final input latch. H1(H3) is edge sensitive and may assume any duty cycle as long as both high and low minimum times are observed. The PI/T contains a port status register whose H1S(H3S) status bit is set anytime any input data that has not been read by the bus master is present in the double-buffered latches. The action of H2(H4) is programmable. The following options are available:

- 1. H2(H4) may be an edge-sensitive status input that is independent of H1(H3) and the transfer of port data. On the asserted edge of H2(H4), the H2S(H4S) status bit is set. It is cleared by either the RESET pin being asserted, writing a one to the particular status bit in the port status register (PSR), or when the H12 enable (H34 enable) bit of the port general register is clear.

- H2(H4) may be a general-purpose output pin that is always negated. In this case the H2S(H4S) status bit is always clear.

- 3. H2(H4) may be a general-purpose output pin that is always asserted. In this case the H2S(H4S) status bit is always clear.

- 4. H2(H4) may be an output pin in the interlocked input handshake protocol. It is asserted when the port input latches are ready to accept new data. It is negated asynchronously following the asserted edge of the H1(H3) input. As soon

as the input latches become ready, H2(H4) is again asserted. When the input double-buffered latches are full, H2(H4) remains negated until data is removed. Thus, anytime the H2(H4) output is asserted, new input data may be entered by asserting H1(H3). At other times, transitions on H1(H3) are ignored. The H2S(H4S) status bit is always clear. When H12 enable (H34 enable) in the port general control register is clear, H2(H4) is held negated.

5. H2(H4) may be an output pin in the pulsed input handshake protocol. It is asserted exactly as in the interlocked input protocol above, but never remains asserted longer than four clock cycles. Typically, a four clock cycle pulse is generated. But in the case of a subsequent H1(H3) asserted edge occurring before termination of the pulse, H2(H4) is negated asynchronously. Thus, anytime after the leading edge of the H2(H4) pulse, new data may be entered in the double-buffered input latches. The H2S(H4S) status bit is always clear. When H12 enable (H34 enable) is clear, H2(H4) is held negated.

For pins used as outputs, the data path consists of a single latch driving the output buffer. Data written to the port's data register does not affect the operation of any handshake pin or status bit. Output pins may be used independently of the input transfers. However, read bus cycles to the data register do remove data from the port. Therefore, care should be taken to avoid processor instructions that perform unwanted read cycles.

# Programmable Options Mode 0 - Port A Submode 00 and Port B Submode 00

| PACR  |                                                                                            |

|-------|--------------------------------------------------------------------------------------------|

| 76    | Port A Submode                                                                             |

| 0 0   | Submode 00                                                                                 |

| PACR  |                                                                                            |

| 5 4 3 | H2 Control                                                                                 |

| 0 X X | Input pin - edge-sensitive status input, H2S is set on an asserted edge.                   |

| 100   | Output pin - negated, H2S is always clear.                                                 |

| 101   | Output pin - asserted, H2S is always clear.                                                |

| 110   | Output pin - interlocked input handshake protocol, H2S is always clear.                    |

| 111   | Output pin - pulsed input handshake protocol, H2S is always clear.                         |

| PACR  |                                                                                            |

| 2     | H2 Interrupt Enable                                                                        |

| 0     | The H2 interrupt is disabled.                                                              |

| 1     | The H2 interrupt is enabled.                                                               |

| PACR  |                                                                                            |

| 1     | H1 SVCR Enable                                                                             |

| 0     | The H1 interrupt and DMA request are disabled.                                             |

| 1     | The H1 interrupt and DMA request are enabled.                                              |

| PACR  |                                                                                            |

| 0     | H1 Status Control                                                                          |

| Χ     | The H1S status bit is set anytime input data is present in the double-buffered input path. |

| PBCR  |                                                                                            |

| 76    | Port B Submode                                                                             |

| 0 0   | Submode 00                                                                                 |

| PBCR  |                                                                                            |

| 5 4 3 | H4 Control                                                                                 |

| 0 X X | Input pin - edge-sensitive status input, H4S is set on an asserted edge.                   |

| 100   | Output pin - negated, H4S is always cleared.                                               |

| 101   | Output pin - asserted, H4S is always cleared.                                              |

| 110   | Output pin - interlocked input handshake protocol, H4S is always cleared.                  |

| 111   | Output pin - pulsed input handshake protocol, H4S is always cleared.                       |

# Programmable Options Mode 0 - Port A Submode 00 and Port B Submode 00 (continued)

#### **PBCR**

- 2 H4 Interrupt Enable

- 0 The H4 interrupt is disabled.

- 1 The H4 interrupt is enabled.

#### **PBCR**

- 1 H3 SVCRQ Enable

- 0 The H3 interrupt and DMA request are disabled.

- 1 The H3 interrupt and DMA request are enabled.

#### **PBCR**

- 0 H3 Status Control

- X The H3S status bit is set anytime input data is present in the double-buffered input path.

3.3.2. SUBMODE 01 - PIN-DEFINABLE DOUBLE-BUFFERED OUTPUT OR NON-LATCHED INPUT. In mode 0, double-buffered output transfers of up to eight bits are available by programming submode 01 in the desired port's control register. The operation of H2 and H4 may be selected by programming the port A and B control registers, respectively. Data, written by the bus master to the PI/T, is stored in the port's output latches. The peripheral accepts the data by asserting H1(H3), which causes the next data to be moved to the port's output latch as soon as it is available.

The H1S(H3S) status bit may be programmed for two interpretations :

- The H1S(H3S) status bit is set when either the port initial or final output latch can accept new data. It is cleared when both latches are full and cannot accept new data.

- The H1S(H3S) status bit is set when both of the port output latches are empty. It is cleared when at least one latch is full.

The programmable options of the H2(H4) pin are:

- H2(H4) may be an edge-sensitive input pin independent of H1(H3) and the transfer of port data. On the asserted edge of H2(H4), the H2S(H4S) status bit is set. It is cleared by either the RESET pin being asserted, writing a one to the particular status bit in the port status register (PSR), or when the H1(H2) enable (H3(H4) enable) bit of the port general control register is clear.

- H2(H4) may be a general-purpose output pin that is always negated. The H2S(H4S) status bit is always clear.

- 3. H2(H4) may be a general-purpose output pin that is always asserted. The H2S(H4S) status bit is always clear.

- 4. H2(H4) may be an output pin in the interlocked output handshake protocol. H2(H4) is asserted two clock cycles after data is transferred to the double-buffered output latches. The data remains stable at the port pins and H2(H4) remains asserted until the next asserted edge of the H1(H3) input. At that time, H2(H4) is asynchronously negated. As soon as the next data is available, it is transferred to the output latches. When H2(H4) is negated, asserted transitions of H1(H3) have no affect on data paths. The H2S(H4S) status bit is always clear. When H12 enable (H34 enable) is clear, H2(H4) is held negated.

- 5. H2(H4) may be an output pin in the pulsed output handshake protocol. It is asserted exactly as in the interlocked protocol above, but never remains asserted longer than four clock cycles. Typically, a four clock pulse is generated. But in the case that a subsequent H1(H3) asserted edge occurs before termination of the pulse, H2(H4) is negated asynchronously shortening the pulse. The H3S(H4S) status bit is always clear. When H12 enable (H34 enable) is clear H2(H4) is held negated.

For pins used as inputs, data written to the associated data register is double-buffered and passed to the initial or final output latch, but, the output buffer is disabled.

# Programmable Options Mode 0 - Port A Submode 01 and Port B Submode 01

| PACR  |                                                                                                                                                                       |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 76    | Port A Submode                                                                                                                                                        |

| 0 1   | Submode 01                                                                                                                                                            |

| PACR  |                                                                                                                                                                       |

| 5 4 3 | H2 Control                                                                                                                                                            |

| 0 X X | Input pin - edge-sensitive status inputs, H2S is set on an asserted edge.                                                                                             |

| 100   | Output pin - negated, H2S is always clear.                                                                                                                            |

| 101   | Output pin - asserted, H2S is always clear.                                                                                                                           |

| 110   | Output pin - interlocked input handshake protocol, H2S is always clear.                                                                                               |

| 111   | Output pin - pulsed input handshake protocol, H2S is always clear.                                                                                                    |

| PACR  |                                                                                                                                                                       |

| 2     | H2 Interrupt Enable                                                                                                                                                   |

| 0     | The H2 interrupt is disabled.                                                                                                                                         |

| 1     | The H2 interrupt is enabled.                                                                                                                                          |

| PACR  |                                                                                                                                                                       |

| 1     | H1 SVCRQ Enable                                                                                                                                                       |

| 0     | The H1 interrupt and DMA request are disabled.                                                                                                                        |

| 1     | The H1 interrupt and DMA request are enabled.                                                                                                                         |

| PACR  |                                                                                                                                                                       |

| 0     | H1 Status Control                                                                                                                                                     |

| 0     | The H1S status bit is set when either the port A initial or final output latch can accept new data It is clear when both latches are full and cannot accept new data. |

| 1     | The H1S status bit is one when both of the port A output latches are empty. It is clear when at least one latch is full.                                              |

| PBCR  |                                                                                                                                                                       |

| 76    | Port B Submode                                                                                                                                                        |

| 0 1   | Submode 01                                                                                                                                                            |

| PBCR  |                                                                                                                                                                       |

| 5 4 3 | H4 Control                                                                                                                                                            |

| 0 X X | Input pin - edge-sensitive status input, H4S is set on an asserted edge.                                                                                              |

| 100   | Output pin - negated, H4S is always cleared.                                                                                                                          |

| 101   | Output pin - asserted, H4S is always cleared.                                                                                                                         |

| 110   | Output pin - interlocked input handshake protocol, H4S is always cleared.                                                                                             |

| 111   | Output pin - pulsed input handshake protocol, H4S is always cleared.                                                                                                  |

# Programmable Options Mode 0 - Port A Submode 01 and Port B Submode 01 (continued)

#### **PBCR**

- 2 H4 Interrupt Enable

- 0 The H4 interrupt is disabled.

- 1 The H4 interrupt is enabled.

#### **PBCR**

- 1 H3 SVCRQ Enable

- 0 The H3 interrupt and DMA request are disabled.

- 1 The H3 interrupt and DMA request are enabled.

#### **PBCR**

#### 0 H3 Status Control

- The H3S status bit is set when either the port B initial or final output latch can accept new data. It is clear when both latches are full and cannot accept new data.

- The H3S status bit is one when both of the port B output latches are empty. It is clear when at least one latch is full.

3.3.3. SUBMODE 1X - BIT I/O (PIN-DEFINABLE SINGLE-BUFFERED OUTPUT OR NON-LAT-CHED INPUT). In mode 0, simple bit I/O is available by programming submode 1X in the desired port's control register. This submode is intended for applications in which several independent devices must be controlled or monitored. Data written to the associated (input/output) register is single buffered. If the data direction register bit for that pin is a one (output), the output buffer is enabled. If it is a zero (input) data written is still latched, but is not available at the pin. Data read from the data register is the instantaneous value of the pin or what was written to the data register, depending on the contents of the data direction register. H1(H3) is an edge-sensitive status input pin only and it controls no data related function. The H1S(H3S) status bit is set following the asserted edge of the input waveform. It is cleared by either the RESET pin being asserted, writing a one to the associated status bit in the port status register

(PSR), or when the H12 enable (H34 enable) bit of the port general control register is clear. H2 may be programmed as:

- 1. H2(H4) may be an edge-sensitive status input that is independent of H1(H3) and the transfer of port data. On the asserted edge of H2(H4), the H2S(H4S) status bit is set. It is cleared by either the RESET pin being asserted, writing a one to the particular status bit in the port status register (PSR), or when the H12 enable (H34 enable) bit of the port general control register is clear.

- 2. H2(H4) may be a general-purpose output pin that is always negated. In this case the H2S(H4S) status bit is always clear.

- 3. H2(H4) may be a general-purpose output pin that is always asserted. In this case the H2S(H4S) status bit is always clear.

# Programmable Option Mode 0 - Port A Submode 1X and Port B Submode 1X **PACR** 76 Port A Submode 1 X Submode 1X **PACR** 543 **H2 Control** 0 X X Input pin - edge-sensitive status input, H2S is set on an asserted edge. 1 X 0 Output pin - negated, H2S is always cleared. 1 X 1 Output pin - asserted, H2S is always cleared. **PACR** 2 **H2 Interrupt Enable** 0 The H2 interrupt is disabled. 1 The H2 interrupt is enabled. **PACR H1 SVCRQ Enable** 1 0 The H1 interrupt is disabled. 1 The H1 interrupt is enabled. **PACR** 0 **H1 Status Control** Χ H1 is an edge-sensitive status input, H1S is set by an asserted edge of H1. **PBCR** 76 Port B Submode 1 X Submode 1X. **PBCR** 543 **H4 Control** 0 X X Input pin - edge-sensitive status input, H4S is set on an asserted edge. 1 X 0 Output pin - negated, H4S is always cleared. 1 X 1 Output pin - asserted, H4S is always cleared. **PBCR** 2 **H4 Interrupt Enable** 0 The H4 interrupt is disabled. 1 The H4 interrupt is enabled. **PBCR**

1 H3 SVCRQ Enable 0 The H3 interrupt is disabled. 1 The H3 interrupt is enabled.

# Programmable Options Mode 0 - Port A Submode 1X and Port B Submode 1X (continued)

#### **PBCR**

#### 0 H3 Status Control

X H3 is an edge-sensitive status input, H3S is set by an asserted edge of H3.

#### 3.4. MODE 1 - UNIDIRECTIONAL 16-BIT MODE

In mode 1, ports A and B are concatenated to form a single 16-bit port. The port B submode field controls the configuration of both ports. The possible submodes are :

Port B Submode X0 - Pin-Definable Double-Buffered Input or Single-Buffered Output

Port B Submode X1 - Pin-Definable Double-Buffered Output or Non-Latched Input

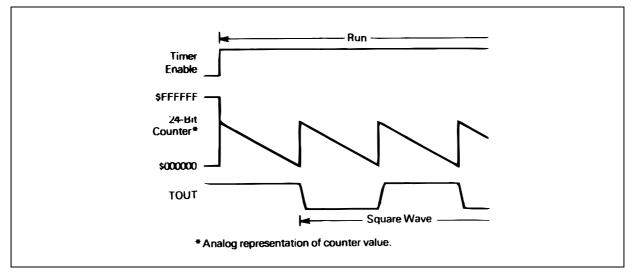

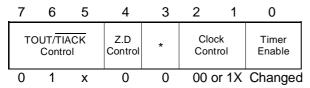

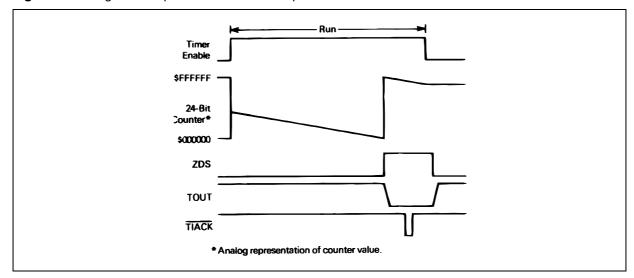

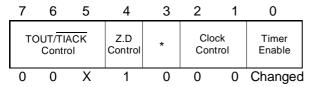

Handshake pins H3 and H4, configured by programming the port B control register, are associated with the 16-bit double-buffered transfer. These 16-bit