# +12 Volt Electronic Fuse

The NIS5232 is a cost effective, resettable fuse which can greatly enhance the reliability of a hard drive or other circuit from both catastrophic and shutdown failures.

It is designed to buffer the load device from excessive input voltage which can damage sensitive circuits. It also includes an overvoltage clamp circuit that limits the output voltage during transients but does not shut the unit down, thereby allowing the load circuit to continue operation.

#### **Features**

- Integrated Power Device

- Power Device Thermally Protected

- No External Current Shunt Required

- 9 V to 18 V Input Range

- 44 mΩ Typical

- Internal Charge Pump

- Internal Undervoltage Lockout Circuit

- Internal Overvoltage Clamp

- ESD Ratings: Human Body Model (HBM); 1500 V Machine Model (MM); 200 V

- UL2367 Approved (UL File #E466553)

- These Devices are Pb-Free and are RoHS Compliant

#### **Typical Applications**

- Hard Drives

- Mother Board Power Management

#### ON Semiconductor®

http://onsemi.com

# 4.2 AMP, 12 VOLT ELECTRONIC FUSE

DFN10 CASE 485C

#### **MARKING DIAGRAM**

1 232 AYW•

| Pin       | Function     |

|-----------|--------------|

| 1         | GND          |

| 2         | dv/dt        |

| 3         | Enable/Fault |

| 4         | ILIMIT       |

| 5         | NC           |

| 6–10      | SOURCE       |

| 11 (flag) | VCC          |

232 = Latching Version

A = Assembly Location

Y = Year

W = Work Week

= Pb–Free Package

(Note: Microdot may be in either location)

#### **ORDERING INFORMATION**

See detailed ordering and shipping information in the ordering information section on page 10 of this data sheet.

**Table 1. FUNCTIONAL PIN DESCRIPTION**

| Pin            | Function           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1              | Ground             | Negative input voltage to the device. This is used as the internal reference for the IC.                                                                                                                                                                                                                                                                                                                                                                                      |

| 2              | dv/dt              | The internal dv/dt circuit controls the slew rate of the output voltage at turn on. It has an internal capacitor that allows it to ramp up over a period of 2 ms. An external capacitor can be added to this pin to increase the ramp time. If an additional time delay is not required, this pin should be left open.                                                                                                                                                        |

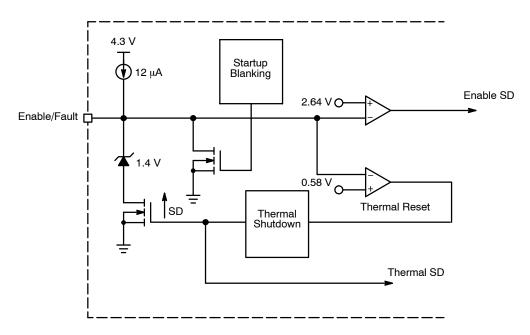

| 3              | Enable/Fault       | The enable/fault pin is a tri-state, bidirectional interface. It can be used to enable or disable the output of the device by pulling it to ground using an open drain or open collector device. If a thermal fault occurs, the voltage on this pin will go to an intermediate state to signal a monitoring circuit that the device is in thermal shutdown. It can also be connected to another device in this family to cause a simultaneous shutdown during thermal events. |

| 4              | I <sub>Limit</sub> | A resistor between this pin and the source pin sets the overload and short circuit current limit levels.                                                                                                                                                                                                                                                                                                                                                                      |

| 6–10           | Source             | This pin is the source of the internal power FET and the output terminal of the fuse.                                                                                                                                                                                                                                                                                                                                                                                         |

| 11 (belly pad) | V <sub>CC</sub>    | Positive input voltage to the device.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

#### **MAXIMUM RATINGS**

| Rating                                                                                                                             | Symbol                | Value                    | Unit       |

|------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--------------------------|------------|

| Input Voltage, operating, steady-state (V <sub>CC</sub> to GND, Note 1)<br>Transient (100 ms)                                      | V <sub>IN</sub>       | -0.6 to 18<br>-0.6 to 25 | V          |

| Thermal Resistance, Junction-to-Air 0.1 in <sup>2</sup> copper (Note 2) 0.5 in <sup>2</sup> copper (Note 2) 4-layer board (Note 4) | $\theta_{	extsf{JA}}$ | 160<br>95<br>50          | °C/W       |

| Thermal Resistance, Junction-to-Lead (Pin 1)                                                                                       | θ <sub>JL</sub>       | 27                       | °C/W       |

| Thermal Resistance, Junction-to-Case                                                                                               | $\theta_{\sf JC}$     | 20                       | °C/W       |

| Total Power Dissipation @ T <sub>A</sub> = 25°C<br>Derate above 25°C                                                               | P <sub>max</sub>      | 1.3<br>10.4              | W<br>mW/°C |

| Operating Temperature Range (Note 3)                                                                                               | T <sub>J</sub>        | -40 to 150               | °C         |

| Nonoperating Temperature Range                                                                                                     | T <sub>J</sub>        | -55 to 155               | °C         |

| Lead Temperature, Soldering (10 Sec)                                                                                               | TL                    | 260                      | °C         |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

- 1. Negative voltage will not damage device provided that the power dissipation is limited to the rated allowable power for the package.

- 2. 1 oz. copper, double-sided FR4.

- 3. Thermal limit is set above the maximum thermal rating. It is not recommended to operate this device at temperatures greater than the maximum ratings for extended periods of time.

- 4. JESD51-7 4-layer board.

$\textbf{ELECTRICAL CHARACTERISTICS} \text{ (Unless otherwise noted: } V_{CC} = 12 \text{ V, } C_L = 100 \text{ } \mu\text{F, dv/dt pin open, } R_{LIMIT} = 10 \text{ } \Omega, T_j = 25^{\circ}\text{C}$ unless otherwise noted.)

| Characteristics                                                                                                     | Symbol               | Min  | Тур        | Max             | Unit  |

|---------------------------------------------------------------------------------------------------------------------|----------------------|------|------------|-----------------|-------|

| POWER FET                                                                                                           |                      |      |            |                 |       |

| Delay Time (enabling of chip to I <sub>D</sub> = 100 mA with 1 A resistive load)                                    | $T_{dly}$            |      | 220        |                 | μs    |

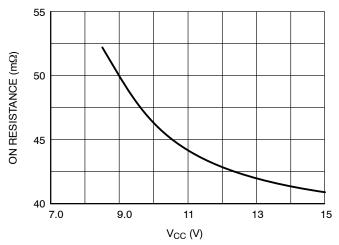

| Kelvin ON Resistance (Note 5)<br>T <sub>J</sub> = 140°C (Note 6)                                                    | R <sub>DSon</sub>    | 35   | 44<br>62   | 55              | mΩ    |

| Off State Output Voltage $(V_{CC} = 18 V_{dc}, V_{GS} = 0 V_{dc}, R_L = \infty)$                                    | V <sub>off</sub>     |      | 190        | 300             | mV    |

| Output Capacitance (V <sub>DS</sub> = 12 V <sub>dc</sub> , V <sub>GS</sub> = 0 V <sub>dc</sub> , f = 1 MHz)         |                      |      | 250        |                 | pF    |

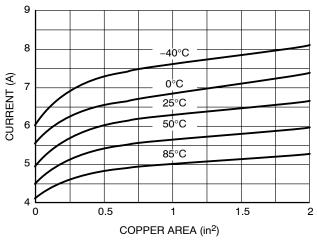

| Continuous Current ( $T_A$ = 25°C, 0.5 in <sup>2</sup> copper) (Note 6) ( $T_A$ = 80°C, minimum copper)             | I <sub>D</sub>       |      | 4.2<br>2.5 |                 | А     |

| THERMAL LATCH                                                                                                       |                      |      |            |                 |       |

| Shutdown Temperature (Note 6)                                                                                       | T <sub>SD</sub>      | 150  | 175        | 200             | °C    |

| UNDER/OVERVOLTAGE PROTECTION                                                                                        |                      |      |            |                 |       |

| Output Clamping Voltage (Overvoltage Protection) (V <sub>CC</sub> = 18 V)                                           | $V_{Clamp}$          | 14   | 15         | 16.2            | V     |

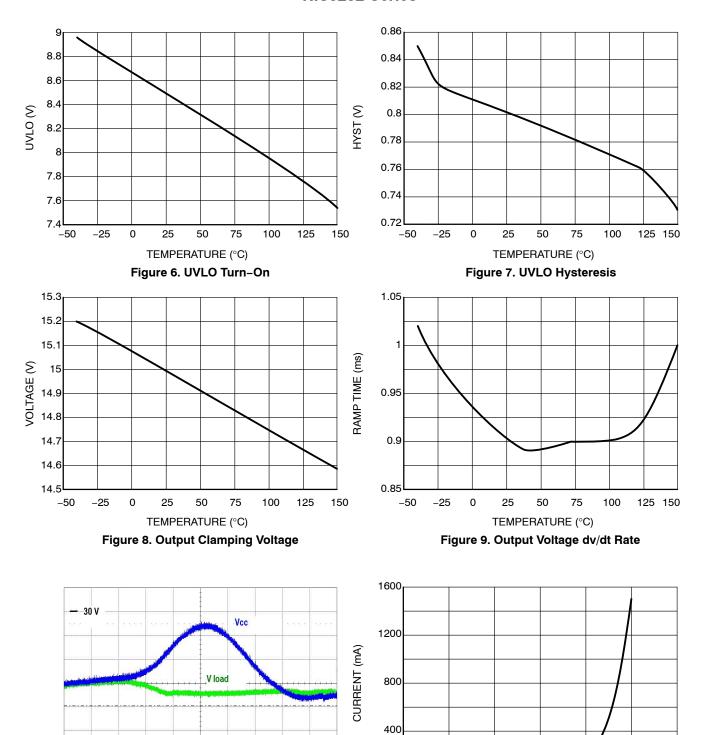

| Undervoltage Lockout (Turn on, voltage going high)                                                                  | V <sub>UVLO</sub>    | 7.7  | 8.5        | 9.3             | V     |

| UVLO Hysteresis                                                                                                     | V <sub>Hyst</sub>    | -    | 0.80       | -               | V     |

| CURRENT LIMIT                                                                                                       |                      |      |            |                 |       |

| Kelvin Short Circuit Current Limit ( $R_{Limit} = 15.4 \Omega$ , Note 7)                                            | I <sub>Lim-SS</sub>  | 2.75 | 3.44       | 4.25            | Α     |

| Kelvin Overload Current Limit ( $R_{Limit} = 15.4 \Omega$ , Note 7)                                                 | I <sub>Lim-OL</sub>  |      | 4.6        |                 | Α     |

| dv/dt CIRCUIT                                                                                                       |                      |      |            |                 |       |

| Output Voltage Ramp Time (Enable to V <sub>OUT</sub> = 11.7 V)                                                      | t <sub>slew</sub>    | 0.5  | 0.9        | 1.8             | ms    |

| Maximum Capacitor Voltage                                                                                           | $V_{max}$            |      |            | V <sub>CC</sub> | V     |

| ENABLE/FAULT                                                                                                        |                      |      |            |                 |       |

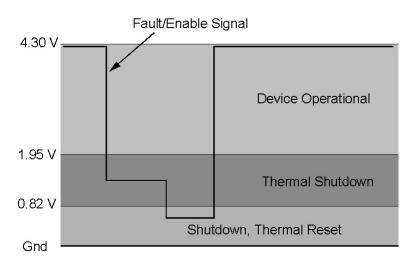

| Logic Level Low (Output Disabled)                                                                                   | $V_{in-low}$         | 0.35 | 0.58       | 0.81            | V     |

| Logic Level Mid (Thermal Fault, Output Disabled)                                                                    | $V_{in-mid}$         | 0.82 | 1.4        | 1.95            | V     |

| Logic Level High (Output Enabled)                                                                                   | $V_{in-high}$        | 1.96 | 2.64       | 3.30            | V     |

| High State Maximum Voltage                                                                                          | V <sub>in-max</sub>  | 3.40 | 4.30       | 5.2             | V     |

| Logic Low Sink Current (V <sub>enable</sub> = 0 V)                                                                  | I <sub>in-low</sub>  |      | -17        | -25             | μΑ    |

| Logic High Leakage Current for External Switch (V <sub>enable</sub> = 3.3 V)                                        | I <sub>in-leak</sub> |      |            | 1.0             | μΑ    |

| Maximum Fanout for Fault Signal (Total number of chips that can be connected to this pin for simultaneous shutdown) | Fan                  |      |            | 3.0             | Units |

| TOTAL DEVICE                                                                                                        |                      |      |            |                 |       |

| Bias Current (Operational)                                                                                          | I <sub>Bias</sub>    |      | 1.8        | 2.5             | mA    |

| Bias Current (Shutdown)                                                                                             | I <sub>Bias</sub>    |      | 1.0        |                 | mA    |

| Minimum Operating Voltage (Notes 6 and 8)                                                                           | V <sub>min</sub>     |      |            | 7.6             | V     |

|                                                                                                                     |                      |      |            |                 |       |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions. 5. Pulse test: Pulse width 300  $\mu$ s, duty cycle 2%.

Refer to explanation of short circuit and overload conditions in application note AND8140.

Device will shut down prior to reaching this level based on actual UVLO trip point.

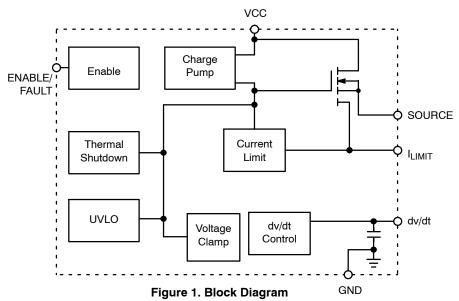

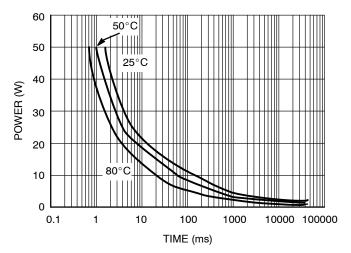

Figure 2. Power Dissipation vs. Thermal Trip Time

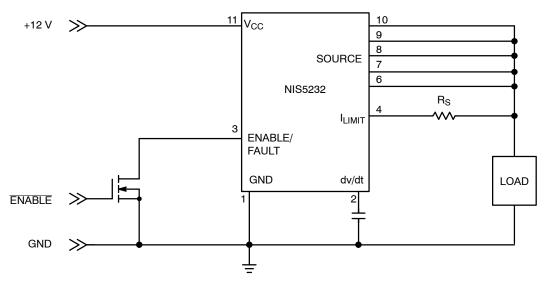

Figure 3. Application Circuit with Direct Current Sensing

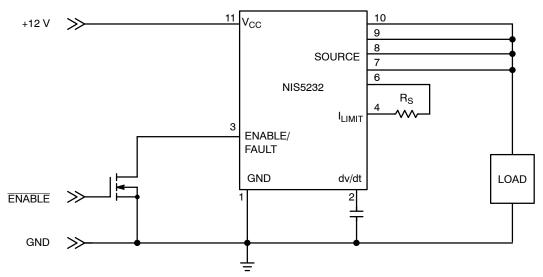

Figure 4. Application Circuit with Kelvin Current Sensing

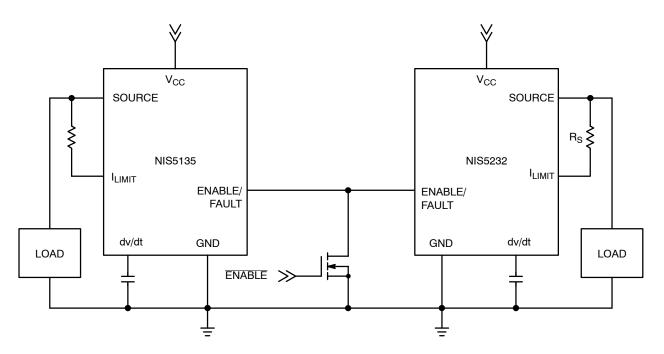

Figure 5. Common Thermal Shutdown

**Figure 10. Input Transient Response**

500 ns/Div

\_\_ Gnd

Figure 11. Body Diode Forward Characteristics

FORWARD VOLTAGE (V)

0.8

0.5

CURRENT (A)

CURRENT (A)

Figure 12. Thermal Limit vs. Copper Area and Ambient Temperature

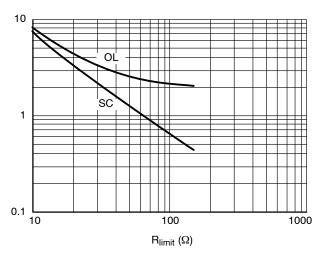

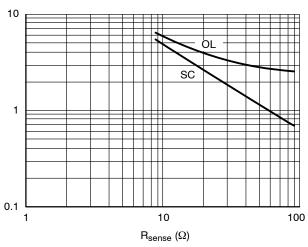

Figure 13. Current Limit vs. R<sub>sense</sub> for Direct Current Sensing

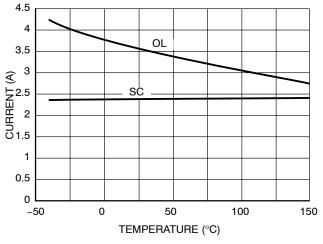

Figure 14. Direct Current Sensing Levels vs. Temperature for 27  $\Omega$  Sense Resistor

Figure 15. Current Limit vs. R<sub>sense</sub> for Kelvin Current Sensing

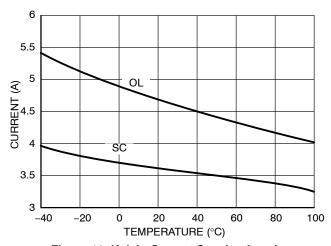

Figure 16. Kelvin Current Sensing Levels vs. Temperature for 15  $\Omega$  Sense Resistor

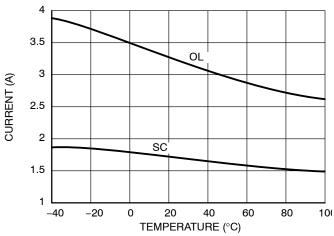

Figure 17. Kelvin Current Sensing Levels vs. Temperature for 33  $\Omega$  Sense Resistor

Figure 18. On Resistance vs. V<sub>CC</sub>

#### **APPLICATION INFORMATION**

## **Basic Operation**

This device is a self-protected, resettable, electronic fuse. It contains circuits to monitor the input voltage, output voltage, output current and die temperature.

On application of the input voltage, the device will apply the input voltage to the load based on the restrictions of the controlling circuits. The dv/dt of the output voltage will be controlled by the internal dv/dt circuit. The output voltage will slew from 0 V to the rated output voltage in 2 ms, unless additional capacitance is added to the dv/dt pin.

The device will remain on as long as the temperature does not exceed the 175°C limit that is programmed into the chip. The current limit circuit does not shut down the part but will reduce the conductivity of the FET to maintain a constant current at the internally set current limit level. The input overvoltage clamp also does not shutdown the part, but will limit the output voltage to 15 V in the event that the input exceeds that level.

An internal charge pump provides bias for the gate voltage of the internal n-channel power FET and also for the current limit circuit. The remainder of the control circuitry operates between the input voltage ( $V_{CC}$ ) and ground.

#### **Current Limit**

The current limit circuit uses a SENSEFET along with a reference and amplifier to control the peak current in the device. The SENSEFET allows for a small fraction of the load current to be measured, which has the advantage of reducing the losses in the sense resistor as well as increasing the value and decreasing the power rating of the sense resistor. Sense resistors are typically in the tens of ohms range with power ratings of several milliwatts making them very inexpensive chip resistors.

The current limit circuit has two limiting values, one for short circuit events which are defined as the mode of operation in which the gate is high and the FET is fully enhanced. The overload mode of operation occurs when the device is actively limiting the current and the gate is at an intermediate level. For a more detailed description of this circuit please refer to application note AND8140.

There are two methods of biasing the current limit circuit for this device. They are shown in the two application figures. Direct current sensing connects the sense resistor between the current limit pin and the load. This method includes the bond wire resistance in the current limit circuit. This resistance has an impact on the current limit levels for a given resistor and may vary slightly depending on the impedance between the sense resistor and the source pins. The on resistance of the device will be slightly lower in this configuration since all five source pins are connected in parallel and therefore, the effective bond wire resistance is one fifth of the resistance for any given pin.

The other method is Kelvin sensing. This method uses one of the source pins as the connection for the current sense resistor. This connection senses the voltage on the die and therefore any bond wire resistance and external impedance on the board have no effect on the current limit levels. In this configuration the on resistance is slightly increased relative to the direct sense method since only four of the source pins are used for power.

# **Overvoltage Clamp**

The overvoltage clamp consists of an amplifier and reference. It monitors the output voltage and if the input voltage exceeds 15 V, the gate drive of the main FET is reduced to limit the output. This is intended to allow operation through transients while protecting the load. If an overvoltage condition exists for many seconds, the device may overheat due to the voltage drop across the FET combined with the load current. In this event, the thermal protection circuit would shut down the device.

#### **Undervoltage Lockout**

The undervoltage lockout circuit uses a comparator with hysteresis to monitor the input voltage. If the input voltage drops below the specified level, the output switch will be switched to a high impedance state.

#### dv/dt Circuit

The dv/dt circuit brings the output voltage up under a linear, controlled rate regardless of the load impedance characteristics. An internal ramp generator creates a linear ramp, and a control circuit forces the output voltage to follow that ramp, scaled by a factor.

The default ramp time is approximately 2 ms. This can be modified by adding an external capacitor at the dv/dt pin. This pin includes an internal current source of approximately 85 nA. Since the current level is very low, it is important to use a ceramic cap or other low leakage capacitor. Aluminum electrolytic capacitors are not recommended for this circuit.

The ramp time from 0 to the nominal output voltage can be determined by the following equation, where t is in seconds:

$$t_{0-12} = 24e6 \cdot (50 \text{ pF} + C_{ext})$$

$$C_{ext} = \frac{t_{0-12}}{24e6} - 50 \text{ pF}$$

Where:

C is in Farads

t is in seconds

Any time that the unit shuts down due to a fault, enable shut-down, or recycling of input power, the timing capacitor will be discharged and the output voltage will ramp from 0 at turn on.

#### Enable/Fault

The Enable/Fault pin is a multi-function, bidirectional pin that can control the output of the chip as well as send

information to other devices regarding the state of the chip. When this pin is low, the output of the fuse will be turned off. When this pin is high the output of the fuse will be turned—on. If a thermal fault occurs, this pin will be pulled low to an intermediate level by an internal circuit.

To use as a simple enable pin, an open drain or open collector device should be connected to this pin. Due to its tri-state operation, it should not be connected to any type of logic with an internal pullup device.

If the chip shuts down due to the die temperature reaching its thermal limit, this pin will be pulled down to an intermediate level. This signal can be monitored by an external circuit to communicate that a thermal shutdown has occurred. If this pin is tied to another device in this family (NIS5232 or NIS5135), a thermal shutdown of one device will cause both devices to disable their outputs. Both devices will turn on once the fault is removed for the auto-retry devices.

For the latching thermal device, the outputs will be enabled after the enable pin has been pulled to ground with an external switch and then allowed to go high or after the input power has been recycled. For the auto retry devices, both devices will restart as soon as the die temperature of the device in shutdown has been reduced to the lower thermal limit.

#### **Thermal Protection**

The NIS5232 includes an internal temperature sensing circuit that senses the temperature on the die of the power FET. If the temperature reaches 175°C, the device will shut down, and remove power from the load. Output power can be restored by either recycling the input power or toggling the enable pin.

The thermal limit has been set high intentionally, to increase the trip time during high power transient events. It is not recommended to operate this device above 150°C for extended periods of time.

Figure 19. Fault/Enable Signal Levels

Figure 20. Enable/Fault Simplified Circuit

## **ORDERING INFORMATION**

| Device        | Features         | Package            | Shipping <sup>†</sup> |

|---------------|------------------|--------------------|-----------------------|

| NIS5232MN1TXG | Thermal Latching | DFN10<br>(Pb-Free) | 3000 / Tape & Reel    |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

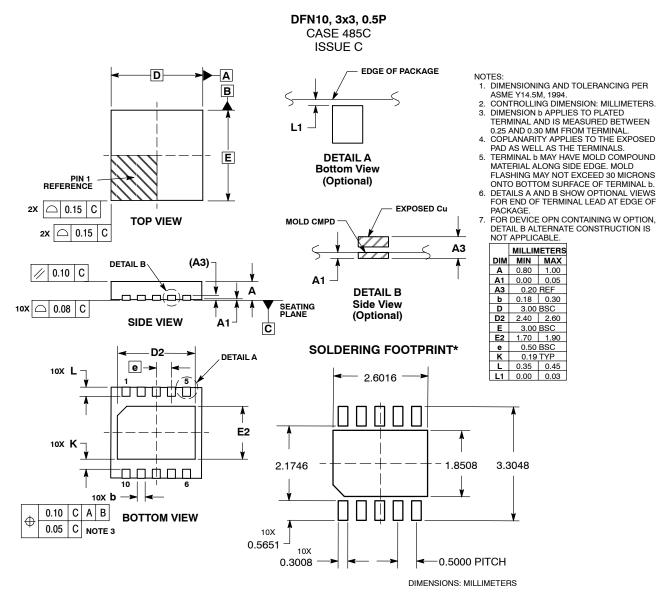

#### PACKAGE DIMENSIONS

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

ON Semiconductor and the interpretability are registered trademarks of Semiconductor Components Industries, LLC (SCILLC) or its subsidiaries in the United States and/or other countries. SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negl

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA **Phone**: 303–675–2175 or 800–344–3860 Toll Free USA/Canada

Fax: 303-675-2175 or 800-344-3860 1011 Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910 Japan Customer Focus Center

Phone: 81-3-5817-1050

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative