# PWM Current-Mode Controller for Free Running Quasi-Resonant Operation

The NCP1337 combines a true current mode modulator and a demagnetization detector which ensures full Borderline/Critical Conduction Mode in any load/line conditions together with minimum drain voltage switching (Quasi–Resonant operation). The transformer core reset detection is done internally, without using any external signal, due to the Soxyless concept. The frequency is internally limited to 130 kHz, preventing the controller to operate above the 150 kHz CISPR–22 EMI starting limit.

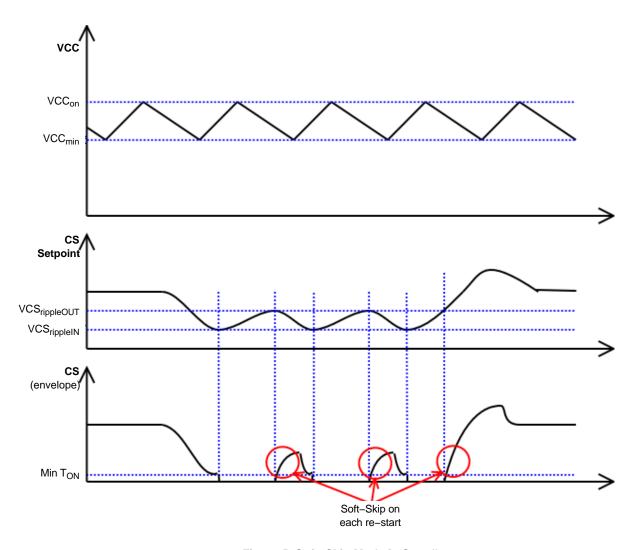

By monitoring the feedback pin activity, the controller enters skip mode as soon as the power demand falls below a predetermined level. As each restart is softened by an internal Soft–Skip  $^{\text{TM}}$ , and as the frequency cannot go below 25 kHz, no audible noise can be heard

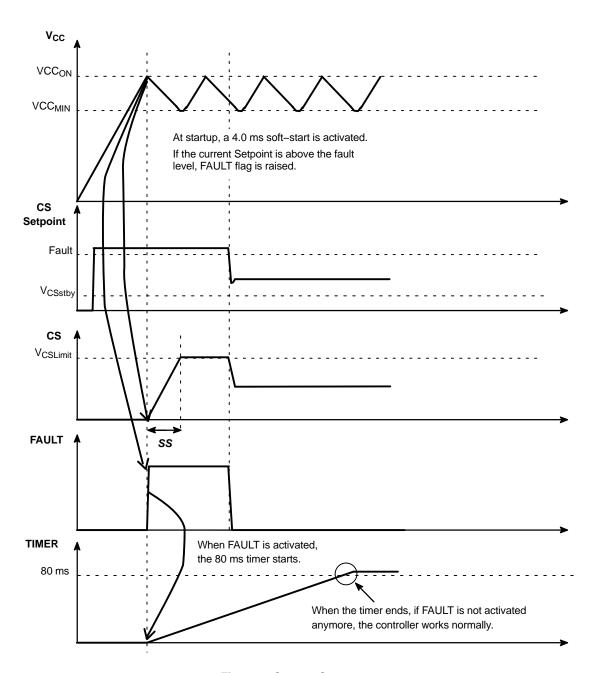

The NCP1337 also features an efficient protective circuitry which, in presence of an overcurrent condition, disables the output pulses and enters a safe burst mode, trying to restart. Once the default has gone, the device auto–recovers. Also included is a bulk voltage monitoring function (known as brown–out protection), an adjustable overpower compensation, and a  $V_{\rm CC}$  OVP. The controller immediately restarts after any of these conditions, unless the fault timer has timed out. Finally, an internal 4.0 ms soft–start eliminates the traditional startup stress.

### **Features**

- Free-Running Borderline/Critical Mode Quasi-Resonant Operation

- Current-Mode

- Soft-Skip Mode with Minimum Switching Frequency for Standby

- Auto-Recovery Short-Circuit Protection Independent of Auxiliary Voltage

- Overvoltage Protection

- Brown-Out Protection

- Two Externally Triggerable Fault Comparators (one for a disable function, and the other for a permanent latch)

- Internal 4.0 ms Soft-Start

- 500 mA Peak Current Drive Sink Capability

- 130 kHz Max Frequency

- Internal Leading Edge Blanking

- Internal Temperature Shutdown

- Direct Optocoupler Connection

- Dynamic Self-Supply with Levels of 12 V (On) and 10 V (Off)

- SPICE Models Available for TRANsient and AC Analysis

- These are Pb-Free Devices

### **Typical Applications**

- AC-DC Adapters for Notebooks, etc.

- Offline Battery Chargers

- Consumer Electronics (DVD Players, Set-Top Boxes, TVs, etc.)

- Auxiliary Power Supplies (USB, Appliances, TVs, etc.)

# ON Semiconductor®

www.onsemi.com

PDIP-7 P SUFFIX CASE 626B

**MARKING**

SOIC-7 D SUFFIX CASE 751U

A = Assembly Location

WL, L = Wafer Lot YY, Y = Year WW, W = Work Week

G, ■ = Pb–Free Package

(Note: Microdot may be in either location)

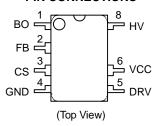

## PIN CONNECTIONS

#### ORDERING INFORMATION

| Device      | Package             | Shipping†        |

|-------------|---------------------|------------------|

| NCP1337PG   | PDIP-7<br>(Pb-Free) | 50 Units/Rail    |

| NCP1337DR2G | SOIC-7<br>(Pb-Free) | 2500 Tape & Reel |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

# PIN FUNCTION DESCRIPTION

| Pin No. | Symbol | Function                                       | Description                                                                                                                                                                                          |

|---------|--------|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | ВО     | Brown-out and external triggering              | <ul> <li>By connecting this pin to the input voltage through a resistor divider, the<br/>controller ensures operation at a safe mains level, thanks to a 500 mV<br/>brown-out comparator.</li> </ul> |

|         |        |                                                | <ul> <li>If an external event brings this pin above 3.0 V, the controller's output is<br/>disabled.</li> </ul>                                                                                       |

|         |        |                                                | <ul> <li>If an external event brings this pin above 5.0 V, the controller is<br/>permanently latched-off.</li> </ul>                                                                                 |

| 2       | FB     | Sets the peak current setpoint                 | By connecting an optocoupler or an auxiliary winding to this pin, the peak current setpoint is adjusted accordingly to the output power demand.                                                      |

|         |        |                                                | When the requested peak current setpoint is below the internal standby level, the device enters Soft–Skip mode.                                                                                      |

| 3       | CS     | Current sense input and overpower compensation | This pin senses the primary current and routes it to the internal comparator via an L.E.B.                                                                                                           |

|         |        | adjustment                                     | <ul> <li>Inserting a resistor in series with the pin allows to control the overpower<br/>compensation level.</li> </ul>                                                                              |

| 4       | GND    | IC ground                                      |                                                                                                                                                                                                      |

| 5       | DRV    | Output driver                                  | To be connected to an external MOSFET.                                                                                                                                                               |

| 6       | VCC    | IC supply                                      | <ul> <li>Connected to a tank capacitor (and possibly an auxiliary winding).</li> <li>When V<sub>CC</sub> reaches 18.6 V, an internal OVP stops the output pulses.</li> </ul>                         |

| 8       | HV     | High-voltage pin                               | <ul> <li>Connected to the high-voltage rail, this pin injects a constant current into<br/>the V<sub>CC</sub> bulk capacitor and ensures a clean lossless startup sequence.</li> </ul>                |

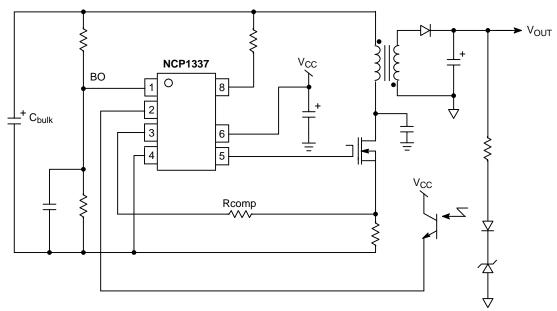

Figure 1. Typical Application Schematic

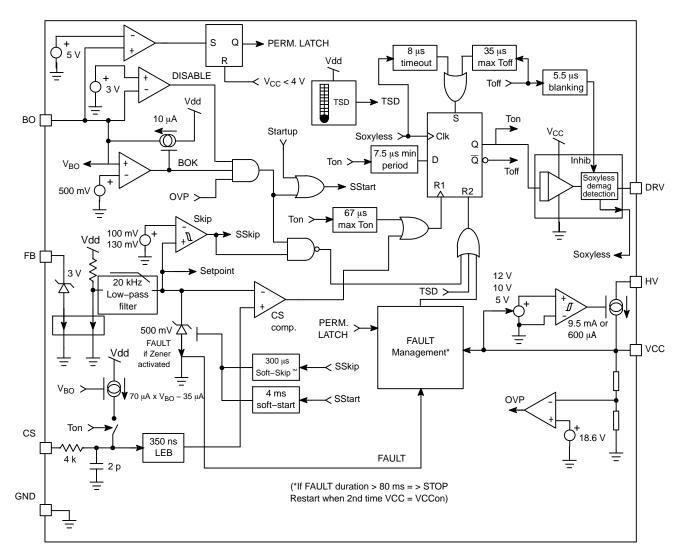

Figure 2. Internal Circuit Architecture

### **MAXIMUM RATINGS**

| Rating                                                                                     | Symbol               | Value       | Unit |

|--------------------------------------------------------------------------------------------|----------------------|-------------|------|

| Voltage on Pin 8 (HV) when Pin 6 (V $_{CC}$ ) is Decoupled to Ground with 10 $\mu\text{F}$ | V <sub>HV</sub>      | -0.3 to 500 | V    |

| Maximum Current in Pin 8 (HV)                                                              | -                    | 20          | mA   |

| Power Supply Voltage, Pin 6 (V <sub>CC</sub> ) and Pin 5 (DRV)                             | V <sub>CCmax</sub>   | -0.3 to 20  | V    |

| Maximum Current in Pin 6 (V <sub>CC</sub> )                                                | -                    | ±30         | mA   |

| Maximum V <sub>CC</sub> Slew Rate (dV/dt)                                                  | dV <sub>CC</sub> /dt | 9.0         | V/ms |

| Maximum Voltage on all Pins except Pin 8 (HV), Pin 6 (V <sub>CC</sub> ) and Pin 5 (DRV)    | -                    | -0.3 to 10  | V    |

| Maximum Current into all Pins except Pin 8 (HV), Pin 6 (V <sub>CC</sub> ) and Pin 5 (DRV)  | -                    | ±10         | mA   |

| Maximum Current into Pin 6 (DRV) during ON Time and T <sub>BLANK</sub>                     | -                    | ±1.0        | Α    |

| Maximum Current into Pin 6 (DRV) after T <sub>BLANK</sub> during OFF Time                  | -                    | ±15         | mA   |

| Thermal Resistance, Junction-to-Case                                                       | $R_{	heta JC}$       | 57          | °C/W |

| Thermal Resistance, Junction-to-Air, SOIC Version                                          | $R_{	hetaJA}$        | 178         | °C/W |

| Thermal Resistance, Junction-to-Air, DIP Version                                           | $R_{	hetaJA}$        | 100         | °C/W |

| Maximum Junction Temperature                                                               | TJ <sub>MAX</sub>    | 150         | °C   |

| Operating Temperature Range                                                                | -                    | -40 to +125 | °C   |

| Storage Temperature Range                                                                  | _                    | -60 to +150 | °C   |

| ESD Capability, HBM Model per JESD22, Method A114E (All Pins except HV)                    | _                    | 2.0         | kV   |

| ESD Capability, Machine Model per JESD22, Method A115A                                     | _                    | 200         | V    |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

<sup>1.</sup> This device contains latchup protection and exceeds 100 mA per JEDEC standard JESD78.

# **ELECTRICAL CHARACTERISTICS**

(For typical values  $T_J = 25^{\circ}C$ , for min/max values  $T_J = 0^{\circ}C$  to  $+125^{\circ}C$ , Max  $T_J = 150^{\circ}C$ ,  $V_{CC} = 11$  V, unless otherwise noted.)

| Characteristic                                                                                                              | Pin | Symbol                   | Min  | Тур  | Max  | Unit     |

|-----------------------------------------------------------------------------------------------------------------------------|-----|--------------------------|------|------|------|----------|

| SUPPLY SECTION                                                                                                              | L   |                          |      |      |      | I        |

| V <sub>CC</sub> Increasing Level at which the Controller Starts                                                             | 6   | VCC <sub>ON</sub>        | 11   | 12   | 13   | V        |

| V <sub>CC</sub> Decreasing Level at which the Controller Stops                                                              |     | VCC <sub>MIN</sub>       | 9.0  | 10   | 11   | V        |

| Protection Mode is Activated if $V_{CC}$ reaches this Level whereas the HV Current Source is ON                             | 6   | VCC <sub>OFF</sub>       | _    | 9.0  | _    | V        |

| V <sub>CC</sub> Decreasing Level at which the Latch–Off Phase Ends                                                          | 6   | VCC <sub>LATCH</sub>     | 3.6  | 5.0  | 6.0  | V        |

| Margin between V <sub>CC</sub> Level at which Latch Fault is Released and VCC <sub>LATCH</sub>                              | _   | V <sub>MARGIN</sub>      | 0.3  | _    | -    | V        |

| V <sub>CC</sub> Increasing Level at which the Controller Enters Protection Mode                                             | 6   | VCC <sub>OVP</sub>       | 17.6 | 18.6 | 19.6 | V        |

| V <sub>CC</sub> Level below which HV Current Source is Reduced                                                              | 6   | VCC <sub>INHIB</sub>     | _    | 1.5  | _    | V        |

| Internal IC Consumption, No Output Load on Pin 5, F <sub>SW</sub> = 60 kHz                                                  | 6   | ICC1                     | _    | 1.2  | -    | mA       |

| Internal IC Consumption, 1.0 nF Output Load on Pin 5, F <sub>SW</sub> = 60 kHz                                              | 6   | ICC2                     | _    | 2.0  | _    | mA       |

| Internal IC Consumption, Latch–Off Phase, V <sub>CC</sub> = 8.0 V                                                           | 6   | ICC3                     | _    | 600  | _    | μΑ       |

| Internal IC Consumption in Skip                                                                                             | 6   | ICC <sub>LOW</sub>       | _    | 600  | _    | μΑ       |

| INTERNAL STARTUP CURRENT SOURCE                                                                                             | I   | _                        | 1    | l    | ı    | <u>I</u> |

| Minimum Guaranteed Startup Voltage on HV Pin                                                                                | 8   | $V_{HVmin}$              | _    | _    | 55   | V        |

| High–Voltage Current Source when $V_{CC} > VCC_{INHIB}$<br>( $V_{CC} = 10.5 \text{ V}, V_{HV} = 60 \text{ V}$ )             | 8   | IC1                      | 5.5  | 9.5  | 15   | mA       |

| High–Voltage Current Source when V <sub>CC</sub> < VCC <sub>INHIB</sub> (V <sub>CC</sub> = 0 V, V <sub>HV</sub> = 60 V)     |     | IC2                      | 0.3  | 0.6  | 1.1  | mA       |

| Leakage Current Flowing when the HV Current Source is OFF (V <sub>CC</sub> = 17 V, V <sub>HV</sub> = 500 V)                 |     | I <sub>HVLeak</sub>      | _    | _    | 90   | μА       |

| DRIVE OUTPUT                                                                                                                | 11  |                          |      |      |      | I        |

| Output Voltage Rise-Time @ CL = 1.0 nF, 10-90% of Output Signal                                                             | 5   | T <sub>R</sub>           | _    | 50   | _    | ns       |

| Output Voltage Fall-Time @ CL = 1.0 nF, 10-90% of Output Signal                                                             | 5   | T <sub>F</sub>           | _    | 20   | _    | ns       |

| Source Resistance                                                                                                           | 5   | R <sub>OH</sub>          | _    | 20   | _    | Ω        |

| Sink Resistance                                                                                                             |     | R <sub>OL</sub>          | _    | 8.0  | _    | Ω        |

| TEMPERATURE SHUTDOWN                                                                                                        | I   |                          | 1    | l    | ı    | <u>I</u> |

| Temperature Shutdown                                                                                                        | _   | TSD                      | 130  | _    | _    | °C       |

| Hysteresis on Temperature Shutdown                                                                                          |     | _                        | _    | 30   | _    | °C       |

| CURRENT COMPARATOR                                                                                                          | I   |                          | 1    | l    | ı    | <u>I</u> |

| Maximum Internal Current Setpoint (@ I <sub>FB</sub> = I <sub>FB100%</sub> )                                                |     | V <sub>CSLimit</sub>     | 475  | 500  | 525  | mV       |

| Minimum Internal Current Setpoint (@ I <sub>FB</sub> = I <sub>FBrippleIN</sub> )                                            | 3   | V <sub>CSrippleIN</sub>  | _    | 100  | _    | mV       |

| Internal Current Setpoint for I <sub>FB</sub> = I <sub>FBrippleOUT</sub>                                                    |     | V <sub>CSrippleOUT</sub> | _    | 130  | _    | mV       |

| Propagation Delay from Current Detection to Gate OFF State                                                                  |     | T <sub>DEL</sub>         | _    | 120  | 150  | ns       |

| Leading Edge Blanking Duration                                                                                              | 3   | T <sub>LEB</sub>         | _    | 350  | _    | ns       |

| Internal Current Offset Injected on the CS Pin during ON Time (Over Power Compensation)  @ 1.0 V on Pin 1 and Vpin3 = 0.5 V | 3   | lopc                     | _    | 35   | _    | μΑ       |

| @ 2.0 V on Pin 1 and Vpin3 = 0.5 V                                                                                          | _   |                          | _    | 105  | _    |          |

| Maximum ON Time                                                                                                             | 5   | MaxT <sub>ON</sub>       | 52   | 67   | 82   | μs       |

# **ELECTRICAL CHARACTERISTICS** (continued)

(For typical values  $T_J = 25^{\circ}C$ , for min/max values  $T_J = 0^{\circ}C$  to +125°C, Max  $T_J = 150^{\circ}C$ ,  $V_{CC} = 11$  V, unless otherwise noted.)

| Characteristic                                                                                  |   | Symbol                   | Min  | Тур | Max  | Unit |

|-------------------------------------------------------------------------------------------------|---|--------------------------|------|-----|------|------|

| FEEDBACK SECTION                                                                                |   |                          |      |     |      |      |

| FB Current under which FAULT is Detected                                                        |   | I <sub>FBopen</sub>      | -    | 40  | -    | μΑ   |

| FB Current for which Internal Setpoint is 100%                                                  | 2 | I <sub>FB100%</sub>      | -    | 50  | -    | μΑ   |

| FB Current above which DRV Pulses are Stopped                                                   | 2 | I <sub>FBrippleIN</sub>  | -    | 220 | -    | μΑ   |

| FB Current under which DRV Pulses are Reauthorized after having reached I <sub>FBrippleIN</sub> | 2 | I <sub>FBrippleOUT</sub> | -    | 205 | -    | μΑ   |

| FB Current above which FB Pin Voltage is not Regulated anymore                                  | 2 | I <sub>FBregMax</sub>    | _    | 500 | -    | μΑ   |

| FB Pin Voltage when I <sub>FBopen</sub> < I <sub>FB</sub> < I <sub>FBregMax</sub>               | 2 | V <sub>FB</sub>          | 2.8  | 3.0 | 3.2  | V    |

| Duration before Entering Protection Mode after FAULT Detection                                  | _ | T <sub>FAULT</sub>       | _    | 80  | -    | ms   |

| Internal Soft–Start Duration (Up to V <sub>CSLimit</sub> )                                      | _ | T <sub>SS</sub>          | _    | 4.0 | -    | ms   |

| Internal Soft–Skip Duration (Up to V <sub>CSLimit</sub> )                                       | _ | T <sub>SSkip</sub>       | _    | 300 | -    | μS   |

| BROWN-OUT AND LATCH SECTION                                                                     | • |                          |      | •   | •    |      |

| Brown-Out Detection Level                                                                       |   | V <sub>BO</sub>          | 460  | 500 | 540  | mV   |

| Current Flowing out of Pin 1 when Brown–Out Comparator has Toggled                              | 1 | I <sub>BO</sub>          | _    | 10  | -    | μΑ   |

| Vpin1 Threshold that Disables the Output                                                        |   | V <sub>DISABLE</sub>     | 2.8  | 3.0 | 3.3  | V    |

| Vpin1 Threshold that Activates the Permanent Latch                                              |   | V <sub>LATCH</sub>       | 4.75 | 5.0 | 5.25 | V    |

| DEMAGNETIZATION DETECTION BLOCK                                                                 |   |                          |      |     | •    | •    |

| Current Threshold for Demagnetization Detection                                                 | 5 | I <sub>SOXYth</sub>      | _    | 210 | _    | μΑ   |

| Max Voltage on DRV Pin During OFF Time after T <sub>BLANK</sub> (when Sinking 15 mA)            | 5 | V <sub>DRVIowMAX</sub>   | -    | -   | 1.5  | V    |

| Min Voltage on DRV Pin During OFF Time after T <sub>BLANK</sub> (when Sourcing 15 mA)           |   | V <sub>DRVIowMIN</sub>   | -0.6 | -   | -    | V    |

| Propagation Delay from Demag Detection to Gate ON State (I <sub>GATE</sub> Slope of 500 A/s)    |   | T <sub>DMG</sub>         | _    | 180 | 220  | ns   |

| Blanking Window after Gate OFF State before Detecting<br>Demagnetization                        |   | T <sub>BLANK</sub>       | -    | 5.5 | -    | μs   |

| Timeout on Demag Signal                                                                         | 5 | T <sub>OUT</sub>         | -    | 8.0 | _    | μS   |

| Maximum OFF Time                                                                                | 5 | MaxT <sub>OFF</sub>      | -    | 35  | 42   | μS   |

| Minimum Switching Period                                                                        | 5 | MinPeriod                | 6.8  | 7.7 | 8.5  | μS   |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

### APPLICATION INFORMATION

### INTRODUCTION

The NCP1337 implements a standard current mode architecture where the switch-off time is dictated by the peak current setpoint, whereas the core-reset detection triggers the turn-on event. This component represents the ideal candidate where low part-count is the key parameter, particularly in low-cost AC-DC adapters, consumer electronics, auxiliary supplies, etc. Due to its high-performance, high-voltage technology, the NCP1337 incorporates all the necessary features needed to build a rugged and reliable Switch-Mode Power Supply (SMPS):

- Quasi-Resonant Operation: Valley-switching

operation is ensured whatever the operating conditions

are, due to the internal soxyless circuitry. As a result,

there are virtually no primary switch turn-on losses,

and no secondary diode recovery losses, and EMI and

video noise perturbations are reduced. The converter

also stays a first-order system and accordingly eases

the feedback loop design.

- Dynamic Self–Supply (DSS): Due to its Very High Voltage Integrated Circuit (VHVIC) technology, ON Semiconductor's NCP1337 allows for a direct pin connection to the high–voltage DC rail. A dynamic current source charges up a capacitor and thus provides a fully independent V<sub>CC</sub> level. As a result, low power applications will not require any auxiliary winding to supply the controller. In applications where this winding is anyway required (see "Power Dissipation" section in the application note), the DSS will simplify the V<sub>CC</sub> capacitor selection.

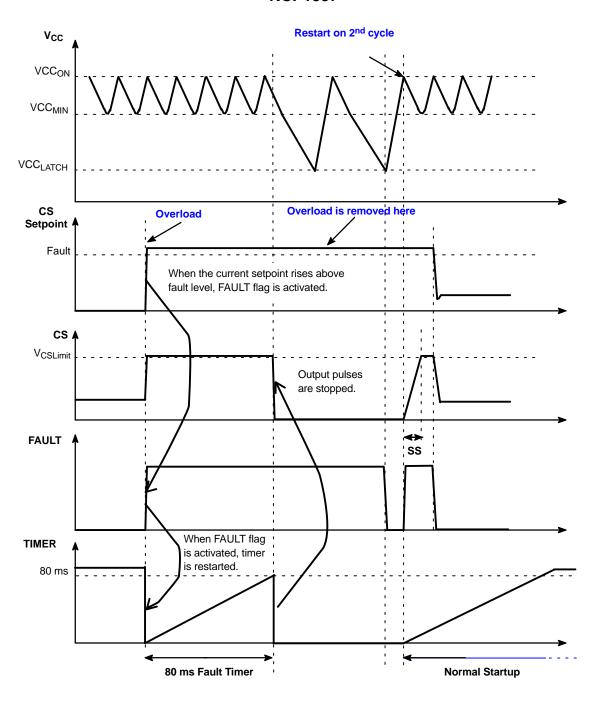

- Overcurrent Protection (OCP): When the feedback current is below minimum value, a fault is detected. If this fault is present for more than 80 ms, NCP1337 enters an auto-recovery soft burst mode. All pulses are stopped and the V<sub>CC</sub> capacitor discharges down to 5.0 V. Then, by monitoring the V<sub>CC</sub> level, the startup current source is activated ON and OFF to create a burst mode. After the current source being activated twice, the controller tries to restart, with a 4.0 ms soft-start. If the fault has gone, the SMPS resumes operation. If the fault is still there, the burst sequence

- starts again. The soft-start, together with a minimum frequency clamp, allow to reduce the noise generated in the transformer in short-circuit conditions.

- Overvoltage Protection (OVP): By continuously monitoring the V<sub>CC</sub> voltage level, the NCP1337 stops switching whenever an overvoltage condition is detected.

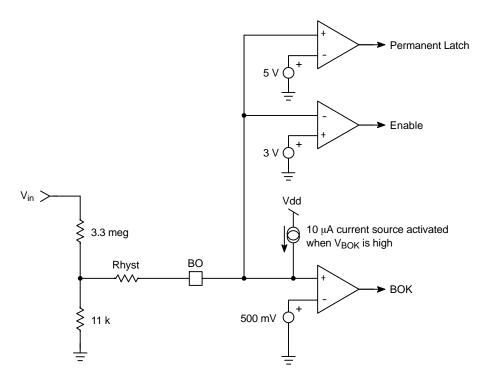

- Brown-Out Detection (BO): By monitoring the level on Pin 1 during normal operation, the controller protects the SMPS against low mains condition. When Pin 1 level falls below 500 mV, the controller stops switching until this level goes back and resumes operation, unless the fault timer has timed out. By adjusting the resistor divider connected between the high input voltage and this pin, start and stop levels are programmable.

- Over Power Compensation (OPC): An internal current source injects out of Pin 3 (CS pin) a current proportional to the voltage applied on Pin 1. As this voltage is an image of the input voltage, by inserting a resistor in series with Pin 3, it is possible to create an offset on the current sense signal that will compensate the effect of the input voltage variation.

- External Latch Trip Point: By externally forcing a level on Pin 1 (e.g., with a signal coming from a temperature sensor) greater than 3.0 V (but below 5.0 V), it is possible to disable the output of the controller. If the voltage is forced over 5.0 V, the controller is permanently latched—off: to resume normal operation, the V<sub>CC</sub> voltage should go below 4.0 V, which implies to unplug the SMPS from the mains.

- Standby Ability: Under low load conditions, NCP1337 enters a Soft–Skip mode: when the CS setpoint becomes lower than 20% of the maximum peak current, output pulses are stopped, then switching is starting again when FB loop forces a setpoint higher than 25%. As this occurs at low peak current, with Soft–Skip activated, and as the T<sub>OFF</sub> is clamped, noise–free operation is guaranteed, even with a cheap transformer.

# **Timing Diagrams**

Figure 3. Startup Sequence

Figure 4. Overload

Figure 5. Soft-Skip Mode in Standby

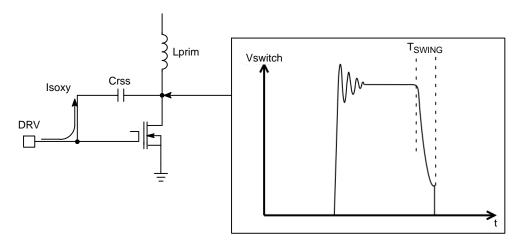

### Soxyless

The "Valley point detection" is based on the observation of the Power MOSFET Drain voltage variations. When the transformer is fully demagnetized, the Drain voltage evolution from the plateau level down to the V<sub>IN</sub> asymptote is governed by the resonating energy transfer between the L<sub>P</sub> transformer inductor and the global capacitance present on the Drain. These voltage oscillations create current oscillation in the parasitic capacitor across the switching

MOSFET (modelized by the Crss capacitance between Gate and Drain): a negative current (flowing out of DRV pin) takes place during the decreasing part of the Drain oscillation, and a positive current (entering into the DRV pin) during the increasing part.

The Drain valley corresponds to the inversion of the current (i.e., the zero crossing): by detecting this point, we always ensure a true valley turn—on.

Figure 6. Soxyless Concept

The current in the Power MOSFET gate is:

Igate = Vringing/Zc (with Zc the capacitance impedance) so

Igate = Vringing •

$$(2 • \pi • Fres • Crss)$$

The magnitude of this gate current depends on the MOSFET, the resonating frequency and the voltage swing present on the Drain at the end of the plateau voltage.

The dead time T<sub>SWING</sub> is given by the equation:

Tswing =

$$0.5/\text{Fres} = \pi * \sqrt{\text{Lp * Cdrain}}$$

(eq. 1)

(where  $L_P$  is the primary transformer inductance and  $C_{DRAIN}$  the total capacitance present on the MOSFET

Drain. This capacitance includes the snubber capacitor if any, the transformer windings stray capacitance plus the parasitic MOSFET capacitances  $C_{OSS}$  and  $C_{RSS}$ ).

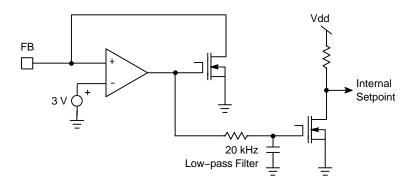

### **Internal Feedback Circuitry**

To simplify the implementation of a primary regulation, it is necessary to inject a current into the FB pin (instead of sourcing it out). But to have a precise primary regulation, the voltage present on FB pin must be regulated. Figure 8 gives the FB pin internal implementation: the circuitry combines the functions of a current to voltage converter and a voltage regulator.

Figure 7. Internal Implementation of FB Pin

The input information is the current injected in FB pin by the feedback loop. The range of current is from 40  $\mu A$  for overload detection to 220  $\mu A$  corresponding to  $V_{CSrippleIN}$ . In transients, currents from 0 to more than 400  $\mu A$  may also appear: the circuitry is able to sustain them.

To regulate the FB pin voltage, the operational amplifier needs to have a high gain and a wide bandwidth. But the feedback information used internally needs to be filtered, because we don't want the controller to be sensitive to the switching noise. For this purpose, a 20 kHz filter is added after the shunt regulator, and any reading of the feedback signal (for ripple mode, fault detection, or setpoint elaboration) is done after.

### **Soft Burst Mode (Protection Mode)**

The NCP1337 features a fault timer to detect an overload completely independently of the  $V_{CC}$  voltage. As soon as the feedback loop asks for the maximum power, a fault is detected, and an internal timer is started. When the fault disappears the timer is reset, but if the timer reaches 80 ms, the protection mode is activated.

Once this protection is toggled, output pulses are stopped and DSS is deactivated (HV current source turn–on threshold changes from  $VCC_{MIN}$  to  $VCC_{LATCH}$ ).  $V_{CC}$  slowly decreases (the current consumption is ICC3), and the HV current source is switched ON when  $V_{CC}$  reaches  $VCC_{LATCH}$ . As a result  $V_{CC}$  increases until  $VCC_{ON}$ , but the controller does not start as the output is still forced low.  $V_{CC}$  decreases again down to  $VCC_{LATCH}$ , and a new start–up cycle occurs. On the second attempt, the output is released, and NCP1337 effectively starts, with the soft–start activated. Figure 4 illustrates this behavior.

### **Safety Features**

The NCP1337 includes several safety features to help the power supply designer to build a rugged design:

- OVP (Overvoltage on V<sub>CC</sub>): Activated when voltage on pin V<sub>CC</sub> is higher than 18.6 V

- Brown–Out (Undervoltage lockout on bulk voltage): Activated when voltage on pin BO is below 500 mV

- Disable (Comparator activated by an external signal): Activated when the voltage on BO pin is higher than 3.0 V but below 5.0 V

- TSD (Temperature shutdown): Typically activated when the die temperature is above 150°C, released at 120°C

All these events have the same consequence for the controller: the DRV pulses are stopped. When the condition disappears, the controller restarts with the soft-start

activated. However, as the fault timer is still active, it can time out while the switching is stopped. As a result the controller will go into protection mode, and won't restart instantaneously.

Permanent Latch (Comparator activated by an external signal): Activated when the voltage on BO pin is above 5.0 V

When this comparator is activated, the DRV pulses are stopped, and the DSS is deactivated (only the start–up current source is turned on each time  $V_{CC}$  reaches  $V_{CC}$  reaches  $V_{CC}$  maintaining  $V_{CC}$  between 5.0 V and 12 V): the controller stays in this position until the  $V_{CC}$  voltage is decreased below 4.0 V, i.e., when the power supply is unplugged from the mains (in normal operation, as soon as a voltage is present on the HV pin,  $V_{CC}$  is always kept above 5.0 V).

### Soft-Skip Mode

The soft ripple mode is a skip mode with a large hysteresis on the skip comparator in order to ensure a noise–free and high–efficiency operation in low–load conditions (standby). When internal setpoint is reaching  $V_{\text{CSrippleIN}} = 100 \text{ mV}$  (corresponding to 20% of the maximum setpoint), the output pulses are stopped. Then FB loop asks for more power and internal setpoint is increasing: when it reaches  $V_{\text{CSrippleOUT}} = 130 \text{ mV}$  (corresponding to 25% of the maximum setpoint), the output starts switching again. Soft–Skip is activated in each activity following a stop period. See Figure 5 for detailed timing diagram.

# **HV Current Source**

NCP1337 features a DSS, to allow operation without any auxiliary voltage. But to protect the die in case of short–circuit on  $V_{CC}$  pin, the current delivered by the HV current source is lowered when  $V_{CC}$  voltage is below 1.5 V.

In the case the current consumed on the DRV pin is higher than the DSS capability (high Qg MOSFET or failure), the HV current source is switched ON when  $V_{CC}$  reaches  $VCC_{MIN}$ , but the voltage on  $V_{CC}$  pin keep on decreasing. If there is no UVLO threshold to stop the DRV pulses, the gate voltage will become too low and the risk is high to destroy the MOSFET. NCP1337 features an additional comparator, which threshold is 9.0 V: when  $V_{CC}$  reaches this level whereas the HV current source is ON, DRV pulses are stopped and the protection mode is activated.

The maximum dV/dt that can be applied to the VCC pin is 9.0 V/ms. The supply capacitor is selected to ensure the maximum dV/dt is not exceeded.

### Brown-Out

The brown–out protection comparator has a fixed reference of 500 mV. When the comparator is activated (i.e., when the input voltage  $V_{\rm IN}$  is above the starting level), a 10  $\mu A$  internal current source is activated and creates an offset across the bottom resistor of the external resistor divider. It gives the minimum hysteresis of the brown–out protection. By adding a series resistor between the divider and the BO pin, it is possible to adjust (increase) the hysteresis.

The BO pin also features two additional comparators: the first one (that toggles at 3.0 V) stops the DRV pulses, whereas the second one (that toggles at 5.0 V) permanently latches off the controller (the  $V_{CC}$  should be forced below 4.0 V to release the latch).

Figure 8 gives the internal implementation of the BO pin.

Figure 8. Internal Implementation of BO Pin

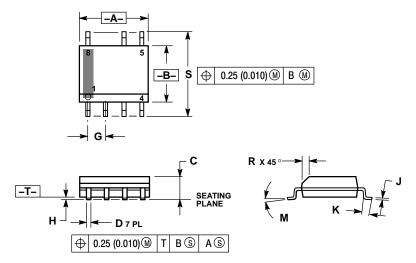

### **PACKAGE DIMENSIONS**

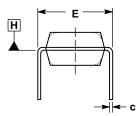

### SOIC-7 **D SUFFIX** CASE 751U **ISSUE E**

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

2. CONTROLLING DIMENSION: MILLIMETER.

3. DIMENSION A AND B ARE DATUMS AND T IS A DATUM SURFACE.

4. DIMENSION A AND B DO NOT INCLUDE MOLD PROTRUSION.

5. MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER SIDE.

|     | MILLIMETERS |          | INCHES |       |  |  |

|-----|-------------|----------|--------|-------|--|--|

| DIM | MIN MAX     |          | MIN    | MAX   |  |  |

| Α   | 4.80        | 5.00     | 0.189  | 0.197 |  |  |

| В   | 3.80        | 4.00     | 0.150  | 0.157 |  |  |

| С   | 1.35        | 1.75     | 0.053  | 0.069 |  |  |

| D   | 0.33        | 0.51     | 0.013  | 0.020 |  |  |

| G   | 1.27        | 1.27 BSC |        | 0 BSC |  |  |

| Н   | 0.10        | 0.25     | 0.004  | 0.010 |  |  |

| J   | 0.19        | 0.25     | 0.007  | 0.010 |  |  |

| K   | 0.40        | 1.27     | 0.016  | 0.050 |  |  |

| М   | 0 °         | 8 °      | 0 °    | 8 °   |  |  |

| N   | 0.25        | 0.50     | 0.010  | 0.020 |  |  |

| S   | 5.80        | 6.20     | 0.228  | 0.244 |  |  |

## **SOLDERING FOOTPRINT\***

$\left(\frac{\text{mm}}{\text{inches}}\right)$ SCALE 6:1

\*For additional information on our Pb–Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

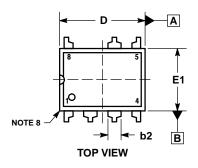

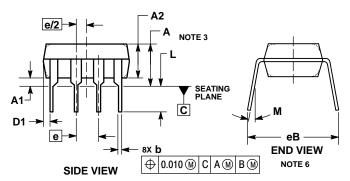

### PACKAGE DIMENSIONS

# PDIP-7 (PDIP-8 LESS PIN 7) **P SUFFIX**

CASE 626B **ISSUE C**

**END VIEW** WITH LEADS CONSTRAINED NOTE 5

- DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

- CONTROLLING DIMENSION: INCHES.

DIMENSIONS A, A1 AND L ARE MEASURED WITH THE PACK-AGE SEATED IN JEDEC SEATING PLANE GAUGE GS-3.

DIMENSIONS D, D1 AND E1 DO NOT INCLUDE MOLD FLASH

- OR PROTRUSIONS. MOLD FLASH OR PROTRUSIONS ARE NOT TO EXCEED 0.10 INCH.

- DIMENSION E IS MEASURED AT A POINT 0.015 BELOW DATUM PLANE H WITH THE LEADS CONSTRAINED PERPENDICULAR TO DATUM C.

DIMENSION E3 IS MEASURED AT THE LEAD TIPS WITH THE

- DATUM PLANE H IS COINCIDENT WITH THE BOTTOM OF THE LEADS, WHERE THE LEADS EXIT THE BODY.

PACKAGE CONTOUR IS OPTIONAL (ROUNDED OR SQUARE

- CORNERS)

|     | INCHES    |           | MILLIMETERS |       |  |

|-----|-----------|-----------|-------------|-------|--|

| DIM | MIN       | MAX       | MIN MAX     |       |  |

| Α   |           | 0.210     |             | 5.33  |  |

| A1  | 0.015     |           | 0.38        |       |  |

| A2  | 0.115     | 0.195     | 2.92        | 4.95  |  |

| b   | 0.014     | 0.022     | 0.35        | 0.56  |  |

| b2  | 0.060 TYP |           | 1.52 TYP    |       |  |

| С   | 0.008     | 0.014     | 0.20        | 0.36  |  |

| D   | 0.355     | 0.400     | 9.02        | 10.16 |  |

| D1  | 0.005     |           | 0.13        |       |  |

| E   | 0.300     | 0.325     | 7.62        | 8.26  |  |

| E1  | 0.240     | 0.280     | 6.10        | 7.11  |  |

| е   | 0.100     | 0.100 BSC |             | BSC   |  |

| eВ  |           | 0.430     |             | 10.92 |  |

| L   | 0.115     | 0.150     | 2.92        | 3.81  |  |

| M   |           | 10°       |             | 10°   |  |

Soft-Skip is a trademark of Semiconductor Components Industries, LLC (SCILLC).

ON Semiconductor and the una are registered trademarks of Semiconductor Components Industries, LLC (SCILLC) or its subsidiaries in the United States and/or other countries. SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent- Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

### **PUBLICATION ORDERING INFORMATION**

### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910

Japan Customer Focus Center Phone: 81–3–5817–1050

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative