## 1.8V Low Power Open-Drain Output Comparator

#### **Features**

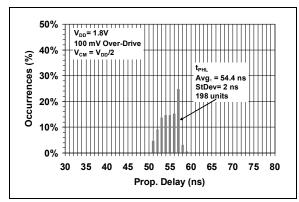

- Propagation Delay at 1.8V<sub>DD</sub>:

- 56 ns (typical) High to Low

- Low Quiescent Current: 100 μA (typical)

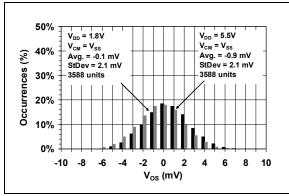

- Input Offset Voltage: ±3 mV (typical)

- Rail-to-Rail Input: V<sub>SS</sub> 0.3V to V<sub>DD</sub> + 0.3V

- · Open-Drain Output

- Wide Supply Voltage Range: 1.8V to 5.5V

- · Available in Single, Dual, and Quad

- Packages: SC70, SOT-23-5, SOIC, MSOP, TSSOP

#### **Typical Applications**

- · Laptop computers

- Mobile Phones

- · Hand-held Electronics

- RC Timers

- · Alarm and Monitoring Circuits

- · Window Comparators

- · Multi-vibrators

#### **Design Aids**

- · Microchip Advanced Part Selector (MAPS)

- Analog Demostration and Evaluation Boards

- · Application Notes

#### **Related Device**

Push-Pull Output: MCP6561/1R/1U/2/4

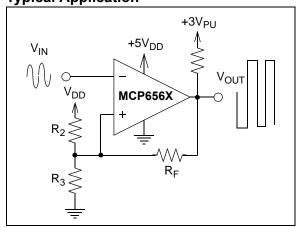

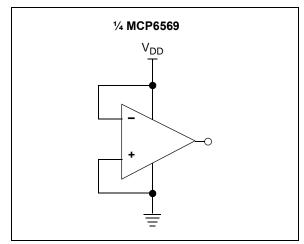

**Typical Application**

#### **Description**

The Microchip Technology, Inc. MCP6566/6R/6U/7/9 families of Open-Drain output comparators are offered in single, dual and guad configurations.

These comparators are optimized for low power 1.8V, single-supply applications with greater than rail-to-rail input operation. The internal input hysteresis eliminates output switching due to internal input noise voltage, reducing current draw. The open-drain output of the MCP6566/6R/6U/7/9 family requires a pull up resistor and it supports pull-up voltages above and below  $\rm V_{\rm DD}$  which can be used to level shift. The output toggle frequency can reach a typical of 4 MHz (typical) while limiting supply current surges and dynamic power consumption during switching.

This family operates with single supply voltage of 1.8V to 5.5V while drawing less than 100  $\mu$ A/comparator of quiescent current (typical).

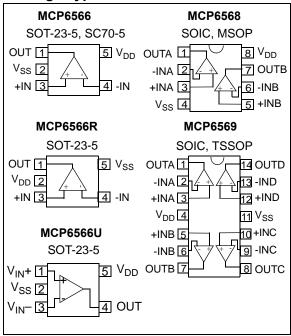

### **Package Types**

NOTES:

# 1.0 ELECTRICAL CHARACTERISTICS

#### 1.1 Maximum Ratings\*

| V <sub>DD</sub> - V <sub>SS</sub>           | 6.5V                              |

|---------------------------------------------|-----------------------------------|

| Open-Drain Output                           | V <sub>SS</sub> + 10.5V           |

| All other inputs and outputs $V_{SS} - 0.3$ | $3V \text{ to } V_{DD} + 0.3V$    |

| Difference Input voltage                    | V <sub>DD</sub> - V <sub>SS</sub> |

| Output Short Circuit Current                | ±25 mA                            |

| Current at Input Pins                       | ±2 mA                             |

| Current at Output and Supply Pins           | ±50 mA                            |

| Storage temperature                         | -65°C to +150°C                   |

| Ambient temp. with power applied            | -40°C to +125°C                   |

| Junction temp                               | +150°C                            |

ESD protection on all pins (HBM/MM) ......≥ 4 kV/300V \*Notice: Stresses above those listed under "Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

#### DC CHARACTERISTICS

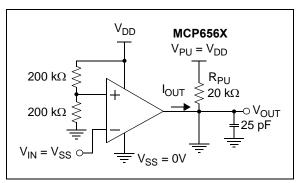

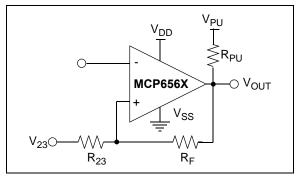

**Electrical Characteristics:** Unless otherwise indicated:  $V_{DD}$  = +1.8V to +5.5V,  $V_{SS}$  = GND,  $T_A$  = +25°C,  $V_{IN}$ + =  $V_{DD}$ /2,  $V_{IN}$ - =  $V_{SS}$ , and  $R_{Pull-Up}$  = 20 k $\Omega$  to  $V_{PU}$  =  $V_{DD}$  (see Figure 1-1).

| Parameters                           | Symbol                   | Min                  | Тур                  | Max                  | Units              | Conditions                                               |

|--------------------------------------|--------------------------|----------------------|----------------------|----------------------|--------------------|----------------------------------------------------------|

| Power Supply                         |                          |                      |                      |                      |                    |                                                          |

| Supply Voltage                       | $V_{DD}$                 | 1.8                  | _                    | 5.5                  | V                  |                                                          |

| Quiescent Current per comparator     | ΙQ                       | 60                   | 100                  | 130                  | μΑ                 | I <sub>OUT</sub> = 0                                     |

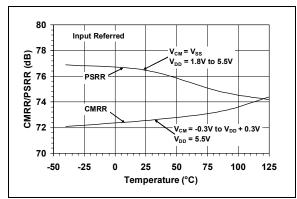

| Power Supply Rejection Ratio         | PSRR                     | 63                   | 70                   |                      | dB                 | $V_{CM} = V_{SS}$                                        |

| Input                                |                          |                      |                      |                      |                    |                                                          |

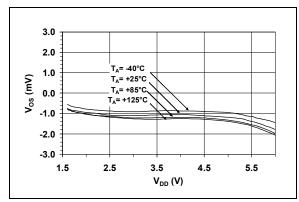

| Input Offset Voltage                 | Vos                      | -10                  | ±3                   | +10                  | mV                 | V <sub>CM</sub> = V <sub>SS</sub> (Note 1)               |

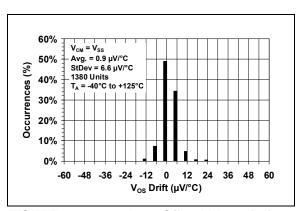

| Input Offset Drift                   | $\Delta V_{OS}/\Delta T$ | _                    | ±2                   |                      | μV/°C              | $V_{CM} = V_{SS}$                                        |

| Input Offset Current                 | I <sub>OS</sub>          | _                    | ±1                   | 1                    | pA                 | $V_{CM} = V_{SS}$                                        |

| Input Bias Current                   | I <sub>B</sub>           | _                    | 1                    | _                    | pА                 | $T_A = +25^{\circ}C, V_{IN^-} = V_{DD}/2$                |

|                                      |                          | _                    | 60                   |                      | pА                 | $T_A = +85^{\circ}C, V_{IN^-} = V_{DD}/2$                |

|                                      |                          | _                    | 1500                 | 5000                 | pA                 | $T_A = +125^{\circ}C, V_{IN}^- = V_{DD}/2$               |

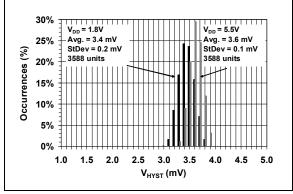

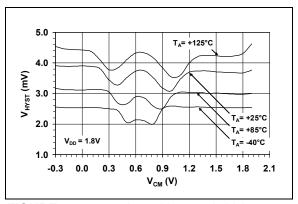

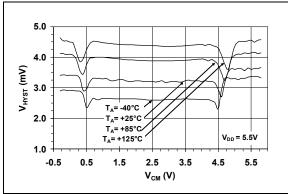

| Input Hysteresis Voltage             | V <sub>HYST</sub>        | 1.0                  | _                    | 5.0                  | mV                 | V <sub>CM</sub> = V <sub>SS</sub> (Notes 1, 2)           |

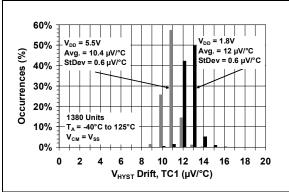

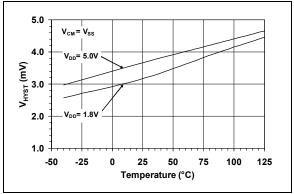

| Input Hysteresis Linear Temp. Co.    | TC <sub>1</sub>          | _                    | 10                   |                      | μV/°C              |                                                          |

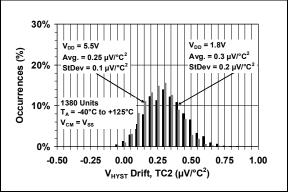

| Input Hysteresis Quadratic Temp. Co. | TC <sub>2</sub>          | _                    | 0.3                  | _                    | μV/°C <sup>2</sup> |                                                          |

| Common-Mode Input Voltage Range      | $V_{CMR}$                | V <sub>SS</sub> -0.2 | _                    | V <sub>DD</sub> +0.2 | V                  | V <sub>DD</sub> = 1.8V                                   |

|                                      |                          | V <sub>SS</sub> -0.3 | _                    | V <sub>DD</sub> +0.3 | V                  | V <sub>DD</sub> = 5.5V                                   |

| Common-Mode Rejection Ratio          | CMRR                     | 54                   | 66                   | _                    | dB                 | $V_{CM}$ = -0.3V to $V_{DD}$ +0.3V, $V_{DD}$ = 5.5V      |

|                                      |                          | 50                   | 63                   | _                    | dB                 | $V_{CM} = V_{DD}/2$ to $V_{DD} + 0.3V$ , $V_{DD} = 5.5V$ |

|                                      |                          | 54                   | 65                   | -                    | dB                 | $V_{CM}$ = -0.3V to $V_{DD}$ /2, $V_{DD}$ = 5.5V         |

| Common Mode Input Impedance          | Z <sub>CM</sub>          | _                    | 10 <sup>13</sup>   4 | _                    | Ω  pF              |                                                          |

| Differential Input Impedance         | Z <sub>DIFF</sub>        | _                    | 10 <sup>13</sup>   2 | _                    | Ω  pF              |                                                          |

Note 1: The input offset voltage is the center of the input-referred trip points. The input hysteresis is the difference between the input-referred trip points.

- 2:  $V_{HYST}$  at different temperatures is estimated using  $V_{HYST}$  (T<sub>A</sub>) =  $V_{HYST}$  @  $_{+25^{\circ}C}$  + (T<sub>A</sub>  $_{-25^{\circ}C}$ ) TC<sub>1</sub> + (T<sub>A</sub>  $_{-25^{\circ}C}$ )<sup>2</sup> TC<sub>2</sub>.

- 3: Limit the output current to Absolute Maximum Rating of 50 mA.

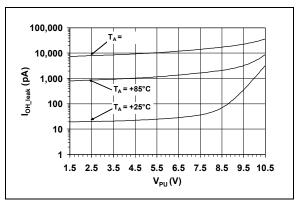

- 4: The pull up voltage for the open drain output V<sub>PULL\_UP</sub> can be as high as the absolute maximum rating of 10.5V. In this case, I<sub>OH leak</sub> can be higher than 1 μA (see Figure 2-30).

## DC CHARACTERISTICS (CONTINUED)

**Electrical Characteristics:** Unless otherwise indicated:  $V_{DD}$  = +1.8V to +5.5V,  $V_{SS}$  = GND,  $T_A$  = +25°C,  $V_{IN}$ + =  $V_{DD}$ /2,  $V_{IN}$ - =  $V_{SS}$ , and  $R_{Pull-Up}$  = 20 k $\Omega$  to  $V_{PU}$  =  $V_{DD}$  (see Figure 1-1).

| Parameters                        | Symbol               | Min | Тур | Max            | Units | Conditions                                                 |  |  |  |

|-----------------------------------|----------------------|-----|-----|----------------|-------|------------------------------------------------------------|--|--|--|

| Push-Pull Output                  |                      |     |     |                |       |                                                            |  |  |  |

| Pull-up Voltage                   | V <sub>PULL_UP</sub> | 1.6 | _   | 5.5            | V     |                                                            |  |  |  |

| High Level Output Voltage         | V <sub>OH</sub>      | _   | _   | $V_{PULL\_UP}$ | V     | (see Figure 1-1) (Notes 3, 4)                              |  |  |  |

| High Level Output Current leakage | I <sub>OH_leak</sub> | _   | _   | 1              | μΑ    | Note 4                                                     |  |  |  |

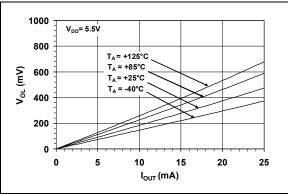

| Low Level Output Voltage          | V <sub>OL</sub>      |     | _   | 0.6            | ٧     | $I_{OUT} = 3 \text{ mA/8 mA} @ V_{DD} = 1.8 \text{V/5.5V}$ |  |  |  |

| Short Circuit Current (Notes 3)   | I <sub>SC</sub>      | _   | ±30 | _              | mA    | Not to exceed Absolute Max. Rating                         |  |  |  |

| Output Pin Capacitance            | C <sub>OUT</sub>     | _   | 8   | _              | pF    |                                                            |  |  |  |

- **Note** 1: The input offset voltage is the center of the input-referred trip points. The input hysteresis is the difference between the input-referred trip points.

- 2:  $V_{HYST}$  at different temperatures is estimated using  $V_{HYST}$  ( $T_A$ ) =  $V_{HYST}$  @  $_{+25^{\circ}C}$  + ( $T_A$   $_{-25^{\circ}C}$ )  $TC_1$  + ( $T_A$   $_{-25^{\circ}C}$ )  $TC_2$ .

- 3: Limit the output current to Absolute Maximum Rating of 50 mA.

- 4: The pull up voltage for the open drain output V<sub>PULL\_UP</sub> can be as high as the absolute maximum rating of 10.5V. In this case, I<sub>OH leak</sub> can be higher than 1 μA (see Figure 2-30).

#### **AC CHARACTERISTICS**

| <b>Electrical Characteristics:</b> Unless otherwise indicated,: Unless otherwise indicated,: $V_{DD} = +1.8V$ to $+5.5V$ , $V_{SS} = GND$ , $T_A = +25^{\circ}C$ , $V_{IN+} = V_{DD}/2$ , $V_{IN-} = V_{SS}$ , $R_{Pull-Up} = 20$ k $\Omega$ to $V_{PU} = V_{DD}$ , and $C_L = 25$ pf (see Figure 1-1). |                  |   |     |    |                   |                                    |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---|-----|----|-------------------|------------------------------------|--|--|

| Parameters Symbo   Min   Typ   Max   Units   Conditions                                                                                                                                                                                                                                                 |                  |   |     |    |                   |                                    |  |  |

| Propagation Delay                                                                                                                                                                                                                                                                                       |                  |   |     |    |                   |                                    |  |  |

| High-to-Low,100 mV Overdrive                                                                                                                                                                                                                                                                            | t <sub>PHL</sub> | _ | 56  | 80 | ns                | $V_{CM} = V_{DD}/2, V_{DD} = 1.8V$ |  |  |

|                                                                                                                                                                                                                                                                                                         |                  | _ | 34  | 80 | ns                | $V_{CM} = V_{DD}/2, V_{DD} = 5.5V$ |  |  |

| Output                                                                                                                                                                                                                                                                                                  | •                |   |     |    |                   |                                    |  |  |

| Fall Time                                                                                                                                                                                                                                                                                               | t <sub>F</sub>   | _ | 20  | _  | ns                |                                    |  |  |

| Maximum Toggle Frequency                                                                                                                                                                                                                                                                                | f <sub>TG</sub>  | _ | 4   | _  | MHz               | V <sub>DD</sub> = 5.5V             |  |  |

|                                                                                                                                                                                                                                                                                                         |                  | 1 | 2   | _  | MHz               | V <sub>DD</sub> = 1.8V             |  |  |

| Input Voltage Noise                                                                                                                                                                                                                                                                                     | E <sub>NI</sub>  | _ | 350 | _  | μV <sub>P-P</sub> | 10 Hz to 10 MHz (Note 1)           |  |  |

- Note 1: ENI is based on SPICE simulation.

- 2: Rise time t<sub>R</sub> and t<sub>PLH</sub> depend on the load (R<sub>L</sub> and C<sub>L</sub>). These specification are valid for the specified load only.

#### **TEMPERATURE SPECIFICATIONS**

| <b>Electrical Characteristics:</b> Unless otherwise indicated: $V_{DD} = +1.8V$ to $+5.5V$ and $V_{SS} = GND$ . |                |     |       |      |       |            |  |  |

|-----------------------------------------------------------------------------------------------------------------|----------------|-----|-------|------|-------|------------|--|--|

| Parameters                                                                                                      | Symbo<br>I     | Min | Тур   | Max  | Units | Conditions |  |  |

| Temperature Ranges                                                                                              |                |     |       |      |       |            |  |  |

| Specified Temperature Range                                                                                     | T <sub>A</sub> | -40 | _     | +125 | °C    |            |  |  |

| Operating Temperature Range                                                                                     | T <sub>A</sub> | -40 | _     | +125 | °C    |            |  |  |

| Storage Temperature Range                                                                                       | T <sub>A</sub> | -65 | _     | +150 | °C    |            |  |  |

| Thermal Package Resistances                                                                                     |                |     |       |      |       |            |  |  |

| Thermal Resistance, SC70-5                                                                                      | $\theta_{JA}$  | _   | 331   | _    | °C/W  |            |  |  |

| Thermal Resistance, SOT-23-5                                                                                    | $\theta_{JA}$  | _   | 220.7 | _    | °C/W  |            |  |  |

| Thermal Resistance, 8L-MSOP                                                                                     | $\theta_{JA}$  | _   | 211   | _    | °C/W  |            |  |  |

| Thermal Resistance, 8L-SOIC                                                                                     | $\theta_{JA}$  | _   | 149.5 | _    | °C/W  |            |  |  |

| Thermal Resistance, 14L-SOIC                                                                                    | $\theta_{JA}$  | _   | 95.3  | _    | °C/W  |            |  |  |

| Thermal Resistance, 14L-TSSOP                                                                                   | $\theta_{JA}$  | _   | 100   | _    | °C/W  |            |  |  |

## 1.2 Test Circuit Configuration

This test circuit configuration is used to determine the AC and DC specifications.

**FIGURE 1-1:** AC and DC Test Circuit for the Open-Drain Output Comparators.

NOTES:

#### 2.0 TYPICAL PERFORMANCE CURVES

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore outside the warranted range.

FIGURE 2-1: Input Offset Voltage.

FIGURE 2-2: Input Offset Voltage Drift.

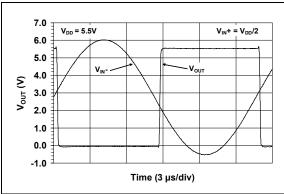

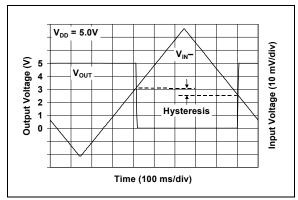

FIGURE 2-3: Input vs. Output Signal, No Phase Reversal.

FIGURE 2-4: Input Hysteresis Voltage.

FIGURE 2-5: Input Hysteresis Voltage Drift - Linear Temp. Co. (TC1).

FIGURE 2-6: Input Hysteresis Voltage Drift - Quadratic Temp. Co. (TC2).

**Note:** Unless otherwise indicated,  $V_{DD}$  = +1.8V to +5.5V,  $V_{SS}$  = GND,  $T_A$  = +25°C,  $V_{IN}$ + =  $V_{DD}$ /2,  $V_{IN^-}$  = GND,  $R_L$  = 20 k $\Omega$  to  $V_{PU}$  =  $V_{DD}$ , and  $C_L$  = 25 pF.

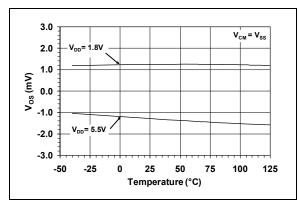

FIGURE 2-7: Temperature.

Input Offset Voltage vs.

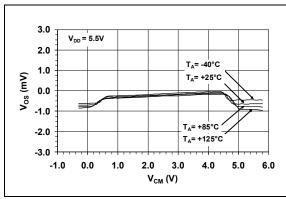

**FIGURE 2-8:** Input Offset Voltage vs. Common-mode Input Voltage.

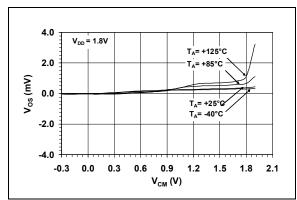

**FIGURE 2-9:** Input Offset Voltage vs. Common-mode Input Voltage.

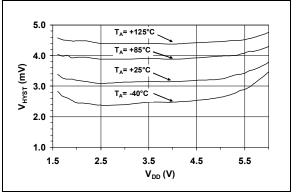

**FIGURE 2-10:** Input Hysteresis Voltage vs. Temperature.

**FIGURE 2-11:** Input Hysteresis Voltage vs. Common-mode Input Voltage.

FIGURE 2-12: Input Hysteresis Voltage vs. Common-mode Input Voltage.

**FIGURE 2-13:** Input Offset Voltage vs. Supply Voltage vs. Temperature.

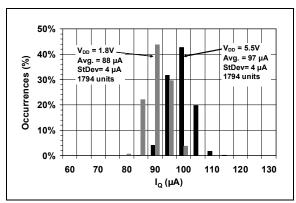

FIGURE 2-14: Quiescent Current.

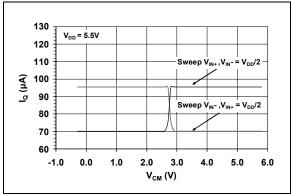

**FIGURE 2-15:** Quiescent Current vs. Common-mode Input Voltage.

**FIGURE 2-16:** Input Hysteresis Voltage vs. Supply Voltage vs. Temperature.

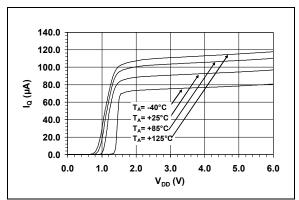

**FIGURE 2-17:** Quiescent Current vs. Supply Voltage vs Temperature.

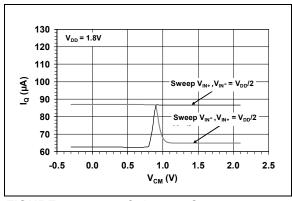

FIGURE 2-18: Quiescent Current vs. Common-mode Input Voltage.

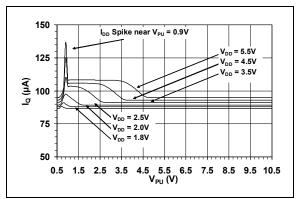

**FIGURE 2-19:** Quiescent Current vs. Pull-up Voltage.

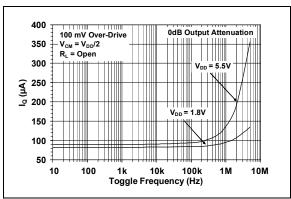

**FIGURE 2-20:** Quiescent Current vs. Toggle Frequency.

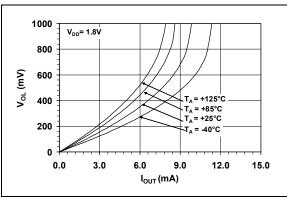

FIGURE 2-21: Output Headroom vs Output Current.

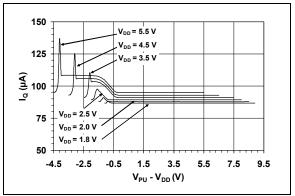

**FIGURE 2-22:** Quiescent Current vs. Pull-up to Supply Voltage Difference.

FIGURE 2-23: Output Leakage Current vs. Pull-up Voltage.

FIGURE 2-24: Output Headroom Vs Output Current.

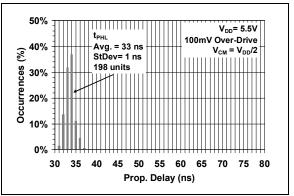

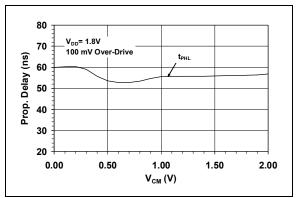

**FIGURE 2-25:** High-to-Low Propagation Delays.

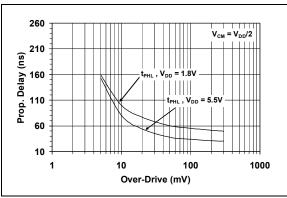

FIGURE 2-26: Propagation Delay vs. Input Over-Drive.

**FIGURE 2-27:** Propagation Delay vs. Supply Voltage.

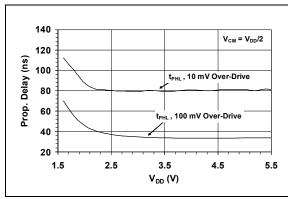

**FIGURE 2-28:** High-to-Low Propagation Delays.

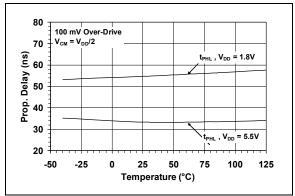

**FIGURE 2-29:** Propagation Delay vs. Temperature.

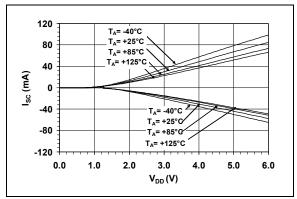

FIGURE 2-30: Short Circuit Current vs. Supply Voltage vs. Temperature.

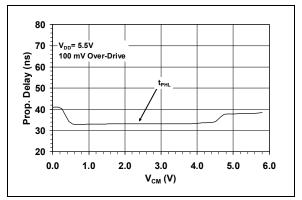

**FIGURE 2-31:** Propagation Delay vs. Common-mode Input Voltage.

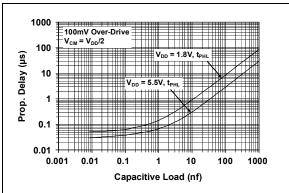

FIGURE 2-32: Propagation Delay vs. Capacitive Load.

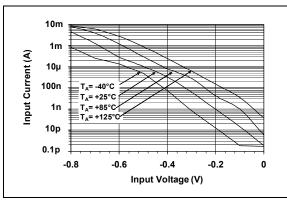

**FIGURE 2-33:** Input Bias Current vs. Input Voltage vs Temperature.

**FIGURE 2-34:** Propagation Delay vs. Common-mode Input Voltage.

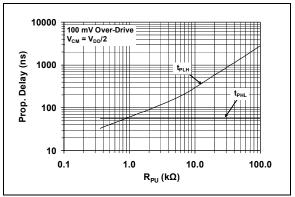

**FIGURE 2-35:** Propagation Delay vs. Pull-up Resistor.

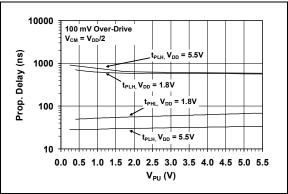

**FIGURE 2-36:** Propagation Delay vs. Pull-up Voltage.

**FIGURE 2-37:** Common-mode Rejection Ratio and Power Supply Rejection Ratio vs. Temperature.

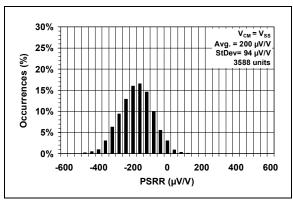

**FIGURE 2-38:** Power Supply Rejection Ratio (PSRR).

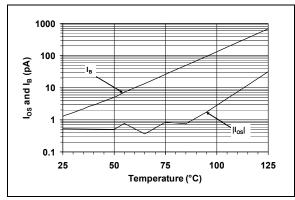

**FIGURE 2-39:** Input Offset Current and Input Bias Current vs. Temperature.

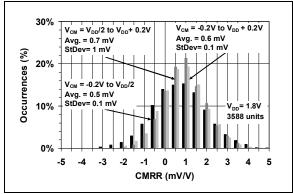

**FIGURE 2-40:** Common-mode Rejection Ratio (CMRR).

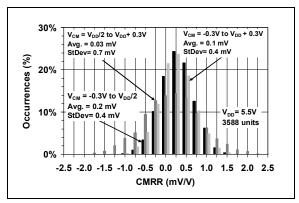

**FIGURE 2-41:** Common-mode Rejection Ratio (CMRR).

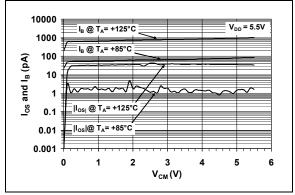

FIGURE 2-42: Input Offset Current and Input Bias Current vs. Common-mode Input Voltage vs. Temperature.

**Note:** Unless otherwise indicated,  $V_{DD}$  = +1.8V to +5.5V,  $V_{SS}$  = GND,  $T_A$  = +25°C,  $V_{IN}$ + =  $V_{DD}$ /2,  $V_{IN^-}$  = GND,  $R_L$  = 20 k $\Omega$  to  $V_{PU}$  =  $V_{DD}$ , and  $C_L$  = 25 pF.

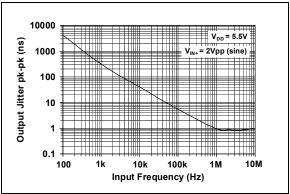

FIGURE 2-43:

Output Jitter vs. Input

Frequency.

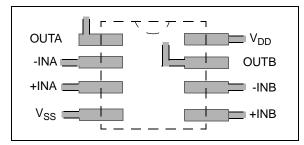

#### 3.0 PIN DESCRIPTIONS

Descriptions of the pins are listed in Table 3-1.

TABLE 3-1: PIN FUNCTION TABLE

| MCP6566             | MCP6566R | MCP6566U | MCP6568       | MCP6569        |                                       |                                    |

|---------------------|----------|----------|---------------|----------------|---------------------------------------|------------------------------------|

| SC70-5,<br>SOT-23-5 | SOT-23-5 | SOT-23-5 | MSOP,<br>SOIC | SOIC,<br>TSSOP | Symbol                                | Description                        |

| 1                   | 1        | 5        | 1             | 1              | OUT, OUTA                             | Digital Output (comparator A)      |

| 4                   | 4        | 3        | 2             | 2              | V <sub>IN</sub> -, V <sub>INA</sub> - | Inverting Input (comparator A)     |

| 3                   | 3        | 1        | 3             | 3              | $V_{IN}$ +, $V_{INA}$ +               | Non-inverting Input (comparator A) |

| 5                   | 2        | 4        | 8             | 4              | $V_{DD}$                              | Positive Power Supply              |

| _                   | _        |          | 5             | 5              | V <sub>INB</sub> +                    | Non-inverting Input (comparator B) |

| _                   | _        |          | 6             | 6              | V <sub>INB</sub> -                    | Inverting Input (comparator B)     |

| _                   | _        |          | 7             | 7              | OUTB                                  | Digital Output (comparator B)      |

| _                   | _        |          | _             | 8              | OUTC                                  | Digital Output (comparator C)      |

| _                   | _        |          | _             | 9              | V <sub>INC</sub> -                    | Inverting Input (comparator C)     |

| _                   | _        |          | _             | 10             | V <sub>INC</sub> +                    | Non-inverting Input (comparator C) |

| 2                   | 5        | 2        | 4             | 11             | V <sub>SS</sub>                       | Negative Power Supply              |

| _                   | _        | _        | _             | 12             | V <sub>IND</sub> +                    | Non-inverting Input (comparator D) |

| _                   | _        |          | _             | 13             | V <sub>IND</sub> -                    | Inverting Input (comparator D)     |

| _                   | _        | _        | _             | 14             | OUTD                                  | Digital Output (comparator D)      |

#### 3.1 Analog Inputs

The comparator non-inverting and inverting inputs are high-impedance CMOS inputs with low bias currents.

#### 3.2 Digital Outputs

The comparator outputs are CMOS, open-drain digital outputs. They are designed to make level shifting and wired-OR easy to implement.

### 3.3 Power Supply ( $V_{SS}$ and $V_{DD}$ )

The positive power supply pin ( $V_{DD}$ ) is 1.8V to 5.5V higher than the negative power supply pin ( $V_{SS}$ ). For normal operation, the other pins are at voltages between  $V_{SS}$  and  $V_{DD}$ .

Typically, these parts are used in a single (positive) supply configuration. In this case,  $V_{SS}$  is connected to ground and  $V_{DD}$  is connected to the supply.  $V_{DD}$  will need a local bypass capacitor (typically 0.01  $\mu$ F to 0.1  $\mu$ F) within 2 mm of the  $V_{DD}$  pin. These can share a bulk capacitor with nearby analog parts (within 100 mm), but it is not required.

NOTES:

#### 4.0 APPLICATIONS INFORMATION

The MCP6566/6R/6U/7/9 family of open-drain output comparators are fabricated on Microchip's state-of-the-art CMOS process. They are suitable for a wide range of high speed applications requiring low power consumption.

#### 4.1 Comparator Inputs

#### 4.1.1 NORMAL OPERATION

The input stage of this family of devices uses two differential input stages in parallel. This configuration provides three regions of operation, one operates at low input voltages, one at high input voltages, and one at mid input voltage. With this topology, the input voltage range is 0.3V above  $\rm V_{DD}$  and 0.3V below  $\rm V_{SS}$ , while providing low offset voltage through out the common mode range. The input offset voltage is measured at both  $\rm V_{SS}$  - 0.3V and  $\rm V_{DD}$  + 0.3V to ensure proper operation.

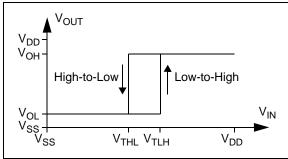

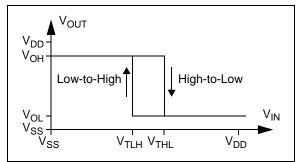

The MCP6566/6R/6U/7/9 family has internally-set hysteresis  $V_{HYST}$  that is small enough to maintain input offset accuracy and large enough to eliminate output chattering caused by the comparator's own input noise voltage  $E_{NI}$ . Figure 4-1 depicts this behavior. Input offset voltage ( $V_{OS}$ ) is the center (average) of the (input-referred) low-high and high-low trip points. Input hysteresis voltage ( $V_{HYST}$ ) is the difference between the same trip points.

**FIGURE 4-1:** The MCP6566/6R/6U/7/9 comparators' internal hysteresis eliminates output chatter caused by input noise voltage.

## 4.1.2 INPUT VOLTAGE AND CURRENT LIMITS

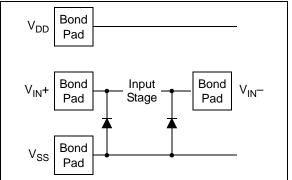

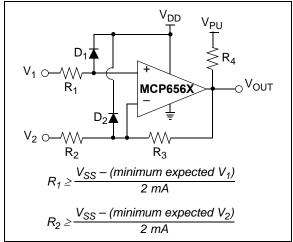

The ESD protection on the inputs can be depicted as shown in Figure 4-2. This structure was chosen to protect the input transistors, and to minimize input bias current ( $I_B$ ). The input ESD diodes clamp the inputs when they try to go more than one diode drop below  $V_{SS}$ . They also clamp any voltages that go too far above  $V_{DD}$ ; their breakdown voltage is high enough to allow normal operation, and low enough to bypass ESD events within the specified limits.

FIGURE 4-2: Simplified Analog Input ESD Structures.

In order to prevent damage and/or improper operation of these amplifiers, the circuits they are in must limit the currents (and voltages) at the  $V_{IN}+$  and  $V_{IN}-$  pins (see Section 1.1 "Maximum Ratings\*" at the beginning of Section 1.0 "Electrical Characteristics"). Figure 4-3 shows the recommended approach to protecting these inputs. The internal ESD diodes prevent the input pins  $(V_{IN}+$  and  $V_{IN}-)$  from going too far below ground, and the resistors  $R_1$  and  $R_2$  limit the possible current drawn out of the input pin. Diodes  $D_1$  and  $D_2$  prevent the input pin  $(V_{IN}+$  and  $V_{IN}-)$  from going too far above  $V_{DD}$ . When implemented as shown, resistors  $R_1$  and  $R_2$  also limit the current through  $D_1$  and  $D_2$ .

FIGURE 4-3: Protecting the Analog Inputs.

It is also possible to connect the diodes to the left of the resistors  $\mathsf{R}_1$  and  $\mathsf{R}_2.$  In this case, the currents through the diodes  $\mathsf{D}_1$  and  $\mathsf{D}_2$  need to be limited by some other mechanism. The resistor then serves as in-rush current limiter; the DC current into the input pins (V<sub>IN</sub>+ and V<sub>IN</sub>-) should be very small.

A significant amount of current can flow out of the inputs when the common mode voltage ( $V_{CM}$ ) is below ground ( $V_{SS}$ ); see Figure 4-3. Applications that are high impedance may need to limit the useable voltage range.

#### 4.1.3 PHASE REVERSAL

The MCP6566/6R/6U/7/9 comparator family uses CMOS transistors at the input. They are designed to prevent phase inversion when the input pins exceed the supply voltages. Figure 2-3 shows an input voltage exceeding both supplies with no resulting phase inversion.

#### 4.2 Open-Drain Output

The open-drain output is designed to make level-shifting and wired-OR logic easy to implement. The output stage minimizes switching current (shoot-through current from supply-to-supply) when the output changes state. See Figures 2-15, 2-18, 2-35 and 2-36, for more information.

#### 4.3 Externally Set Hysteresis

Greater flexibility in selecting hysteresis (or input trip points) is achieved by using external resistors. Hysteresis reduces output chattering when one input is slowly moving past the other. It also helps in systems where it is best not to cycle between high and low states too frequently (e.g., air conditioner thermostatic control). Output chatter also increases the dynamic supply current.

#### 4.3.1 NON-INVERTING CIRCUIT

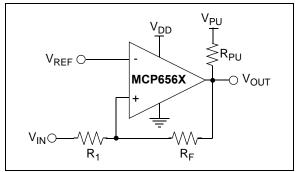

Figure 4-4 shows a non-inverting circuit for singlesupply applications using just two resistors. The resulting hysteresis diagram is shown in Figure 4-5.

**FIGURE 4-4:** Non-Inverting Circuit with Hysteresis for Single-Supply.

FIGURE 4-5: Hysteresis Diagram for the Non-Inverting Circuit.

The trip points for Figures 4-4 and 4-5 are:

#### **EQUATION 4-1:**

$$\begin{split} V_{TLH} &= V_{REF} \bigg( I + \frac{R_I}{R_F} \bigg) - V_{OL} \bigg( \frac{R_I}{R_F} \bigg) \\ V_{THL} &= V_{REF} \bigg( I + \frac{R_I}{R_F} \bigg) - V_{OH} \bigg( \frac{R_I}{R_F} \bigg) \end{split}$$

Where:

$V_{TLH}$  = trip voltage from low-to-high  $V_{THL}$  = trip voltage from high-to-low

#### 4.3.2 **INVERTING CIRCUIT**

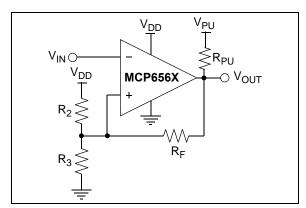

Figure 4-6 shows an inverting circuit for single-supply using three resistors. The resulting hysteresis diagram is shown in Figure 4-7.

FIGURE 4-6: Hysteresis.

Inverting Circuit with

FIGURE 4-7: Hysteresis Diagram for the Inverting Circuit.

In order to determine the trip voltages (V<sub>THI</sub> and V<sub>TI H</sub>) for the circuit shown in Figure 4-6, R2 and R3 can be simplified to the Thevenin equivalent circuit with respect to V<sub>DD</sub>, as shown in Figure 4-8.

FIGURE 4-8:

Thevenin Equivalent Circuit.

Where:

$$R_{23} = \frac{R_2 R_3}{R_2 + R_3}$$

$$V_{23} = \frac{R_3}{R_2 + R_3} \times V_{DD}$$

Using this simplified circuit, the trip voltage can be calculated using the following equation:

#### **EQUATION 4-2:**

$$\begin{split} V_{THL} &= V_{OH} \!\! \left( \! \frac{R_{23}}{R_{23} + R_F} \! \right) + V_{23} \!\! \left( \! \frac{R_F}{R_{23} + R_F} \! \right) \\ V_{TLH} &= V_{OL} \!\! \left( \! \frac{R_{23}}{R_{23} + R_F} \! \right) + V_{23} \!\! \left( \! \frac{R_F}{R_{23} + R_F} \! \right) \end{split}$$

Where:

$V_{TLH}$ trip voltage from low-to-high trip voltage from high-to-low  $V_{THL}$

Figure 2-21 and Figure 2-24 can be used to determine typical values for VOH and VOL.

#### 4.4 **Bypass Capacitors**

With this family of comparators, the power supply pin (V<sub>DD</sub> for single supply) should have a local bypass capacitor (i.e., 0.01 µF to 0.1 µF) within 2 mm for good edge rate performance.

#### 4.5 **Capacitive Loads**

Reasonable capacitive loads (e.g., logic gates) have little impact on propagation delay (see Figure 2-32). The supply current increases with increasing toggle frequency (Figure 2-20), especially with higher capacitive loads. The output slew rate and propogation delay performance will be reduced with higher capacitive loads.

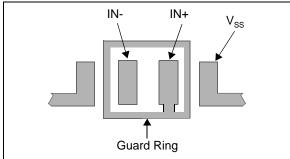

#### 4.6 PCB Surface Leakage

In applications where low input bias current is critical, PCB (Printed Circuit Board) surface leakage effects need to be considered. Surface leakage is caused by humidity, dust or other contamination on the board. Under low humidity conditions, a typical resistance between nearby traces is  $10^{12}\Omega$ . A 5V difference would cause 5 pA of current to flow. This is greater than the MCP6566/6R/6U/7/9 family's bias current at +25°C (1 pA, typical).

The easiest way to reduce surface leakage is to use a guard ring around sensitive pins (or traces). The guard ring is biased at the same voltage as the sensitive pin. An example of this type of layout is shown in Figure 4-9.

FIGURE 4-9: Example Guard Ring Layout for Inverting Circuit.

- 1. Inverting Configuration (Figures 4-6 and 4-9):

- a) Connect the guard ring to the non-inverting input pin (V<sub>IN</sub>+). This biases the guard ring to the same reference voltage as the comparator (e.g., V<sub>DD</sub>/2 or ground).

- b) Connect the inverting pin (V<sub>IN</sub>-) to the input pad without touching the guard ring.

- 2. Non-inverting Configuration (Figure 4-4):

- a) Connect the non-inverting pin (V<sub>IN</sub>+) to the input pad without touching the guard ring.

- b) Connect the guard ring to the inverting input pin (V<sub>IN</sub>-).

#### 4.7 PCB Layout Technique

When designing the PCB layout it is critical to note that analog and digital signal traces are adequately separated to prevent signal coupling. If the comparator output trace is at close proximity to the input traces then large output voltage changes from, V<sub>SS</sub> to V<sub>DD</sub> or visa versa, may couple to the inputs and cause the device output to oscillate. To prevent such oscillation, the output traces must be routed away from the input pins. The SC70-5 and SOT-23-5 are relatively immune because the output pin OUT (pin 1) is separated by the power pin  $V_{DD}/V_{SS}$  (pin 2) from the input pin +IN (as long as the analog and digital traces remain separated through out the PCB). However, the pinouts for the dual and quad packages (SOIC, MSOP, TSSOP) have OUT and -IN pins (pin 1 and 2) close to each other. The recommended layout for these packages is shown in Figure 4-10.

FIGURE 4-10: Recommended Layout.

#### 4.8 Unused Comparators

An unused amplifier in a quad package (MCP6569) should be configured as shown in Figure 4-11. This circuit prevents the output from toggling and causing crosstalk. It uses the minimum number of components and draws minimal current (see Figure 2-15 and Figure 2-15).

FIGURE 4-11: Unused Comparators.

#### 4.9 Typical Applications

#### 4.9.1 PRECISE COMPARATOR

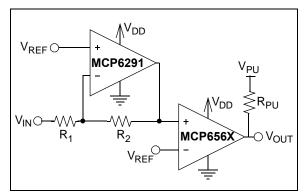

Some applications require higher DC precision. An easy way to solve this problem is to use an amplifier (such as the MCP6291) to gain-up the input signal before it reaches the comparator. Figure 4-12 shows an example of this approach.

**FIGURE 4-12:** Precise Inverting Comparator.

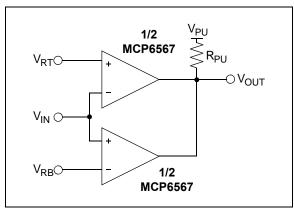

#### 4.9.2 WINDOWED COMPARATOR

Figure 4-13 shows one approach to designing a windowed comparator. The AND gate produces a logic '1' when the input voltage is between  $V_{RB}$  and  $V_{RT}$  (where  $V_{RT} > V_{RB}$ ).

FIGURE 4-13: Windowed Comparator.

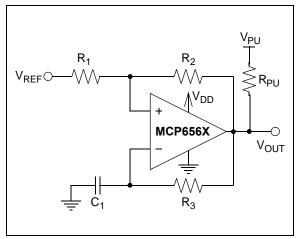

#### 4.9.3 BISTABLE MULTI-VIBRATOR

A simple bistable multi-vibrator design is shown in Figure 4-14.  $V_{REF}$  needs to be between the power supplies ( $V_{SS} = \mbox{GND}$  and  $V_{DD})$  to achieve oscillation. The output duty cycle changes with  $V_{REF}$

FIGURE 4-14: Bistable Multi-vibrator.

NOTES:

#### 5.0 DESIGN AIDS

# 5.1 Microchip Advanced Part Selector (MAPS)

MAPS is a software tool that helps semiconductor professionals efficiently identify Microchip devices that fit a particular design requirement. Available at no cost from the Microchip web site at www.microchip.com/maps, the MAPS is an overall selection tool for Microchip's product portfolio that includes Analog, Memory, MCUs and DSCs. Using this tool you can define a filter to sort features for a parametric search of devices and export side-by-side technical comparison reports. Helpful links are also provided for Data sheets, Purchase, and Sampling of Microchip parts.

#### 5.2 Analog Demonstration and Evaluation Boards

Microchip offers a broad spectrum of Analog Demonstration and Evaluation Boards that are designed to help you achieve faster time to market. For a complete listing of these boards and their corresponding user's guides and technical information, visit the Microchip web site at www.microchip.com/ analogtools. Three of our boards that are especially useful are:

- 8-Pin SOIC/MSOP/TSSOP/DIP Evaluation Board, P/N SOIC8EV

- 14-Pin SOIC/TSSOP/DIP Evaluation Board, P/N SOIC14EV

- 5/6-Pin SOT23 Evaluation Board, P/N VSUPEV2

#### 5.3 Application Notes

The following Microchip Application Notes are available on the Microchip web site at www.microchip.com and are recommended as supplemental reference resources:

AN895, "Oscillator Circuit For RTD Temperature Sensors", DS00895.

NOTES:

#### 6.0 PACKAGING INFORMATION

#### 6.1 **Package Marking Information**

5-Lead SOT-23 (MCP6566, MCP6566R)

| Device                          | Code |  |  |  |

|---------------------------------|------|--|--|--|

| MCP6566T                        | JYNN |  |  |  |

| MCP6566RT                       | JZNN |  |  |  |

| MCP6566UT                       | WLNN |  |  |  |

| Note: Applies to 5-Lead SOT-23. |      |  |  |  |

Example:

Example:

8-Lead SOIC (150 mil) (MCP6567)

Legend: XX...X Customer-specific information

Year code (last digit of calendar year) ΥY Year code (last 2 digits of calendar year) WW Week code (week of January 1 is week '01')

NNN Alphanumeric traceability code

(e3) Pb-free JEDEC designator for Matte Tin (Sn)

This package is Pb-free. The Pb-free JEDEC designator (@3)

can be found on the outer packaging for this package.

In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line, thus limiting the number of available characters for customer-specific information.

## **Package Marking Information (Continued)**

MCP6569 E/SL@3 0934256

14-Lead TSSOP (MCP6569)

Example:

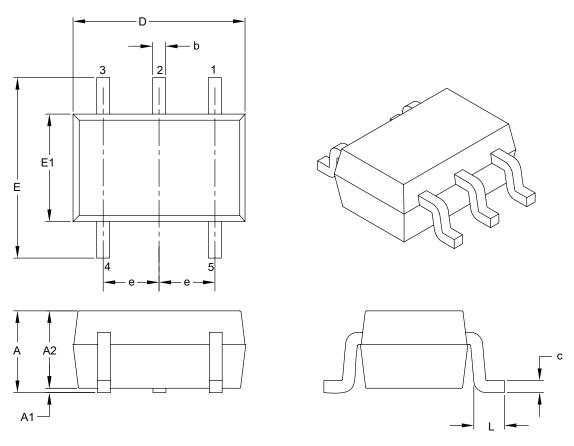

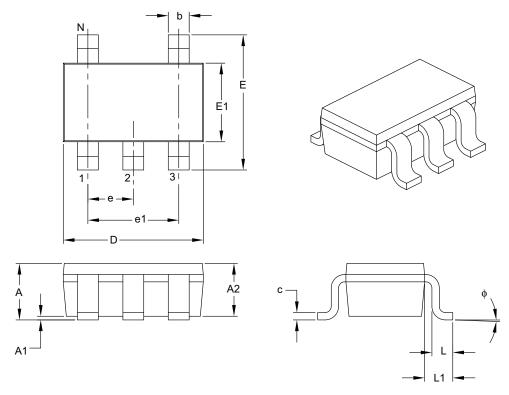

## 5-Lead Plastic Small Outline Transistor (LT) [SC70]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units            |          | MILLIMETERS |      |  |

|--------------------------|------------------|----------|-------------|------|--|

|                          | Dimension Limits | MIN      | NOM         | MAX  |  |

| Number of Pins           | N                |          | 5           |      |  |

| Pitch                    | е                |          | 0.65 BSC    |      |  |

| Overall Height           | A                | 0.80 – 1 |             |      |  |

| Molded Package Thickness | A2               | 0.80     | _           | 1.00 |  |

| Standoff                 | A1               | 0.00     | _           | 0.10 |  |

| Overall Width            | E                | 1.80     | 2.10        | 2.40 |  |

| Molded Package Width     | E1               | 1.15     | 1.25        | 1.35 |  |

| Overall Length           | D                | 1.80     | 2.00        | 2.25 |  |

| Foot Length              | L                | 0.10     | 0.20        | 0.46 |  |

| Lead Thickness           | С                | 0.08     | _           | 0.26 |  |

| Lead Width               | b                | 0.15     | -           | 0.40 |  |

#### Notes:

- 1. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.127 mm per side.

- 2. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-061B

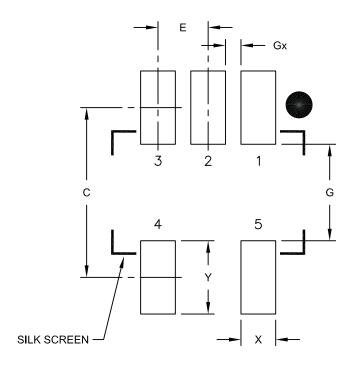

### 5-Lead Plastic Small Outline Transistor (LT) [SC70]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

|                       | Units            | MILLIMETERS |      |      |  |

|-----------------------|------------------|-------------|------|------|--|

| Dimension             | Dimension Limits |             | NOM  | MAX  |  |

| Contact Pitch         | Е                | E 0.65 BSC  |      |      |  |

| Contact Pad Spacing   | С                |             | 2.20 |      |  |

| Contact Pad Width     | Х                |             |      | 0.45 |  |

| Contact Pad Length    | Υ                |             |      | 0.95 |  |

| Distance Between Pads | G                | 1.25        |      |      |  |

| Distance Between Pads | Gx               | 0.20        |      | ·    |  |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2061A

### 5-Lead Plastic Small Outline Transistor (OT) [SOT-23]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units            |      | MILLIMETERS |      |  |

|--------------------------|------------------|------|-------------|------|--|

|                          | Dimension Limits | MIN  | NOM         | MAX  |  |

| Number of Pins           | N                |      | 5           | •    |  |

| Lead Pitch               | е                |      | 0.95 BSC    |      |  |

| Outside Lead Pitch       | e1               |      | 1.90 BSC    |      |  |

| Overall Height           | A                | 0.90 | -           | 1.45 |  |

| Molded Package Thickness | A2               | 0.89 | _           | 1.30 |  |

| Standoff                 | A1               | 0.00 | _           | 0.15 |  |

| Overall Width            | E                | 2.20 | _           | 3.20 |  |

| Molded Package Width     | E1               | 1.30 | _           | 1.80 |  |

| Overall Length           | D                | 2.70 | _           | 3.10 |  |

| Foot Length              | L                | 0.10 | _           | 0.60 |  |

| Footprint                | L1               | 0.35 | _           | 0.80 |  |

| Foot Angle               | ф                | 0°   | _           | 30°  |  |

| Lead Thickness           | С                | 0.08 | _           | 0.26 |  |

| Lead Width               | b                | 0.20 | _           | 0.51 |  |

#### Notes:

- 1. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.127 mm per side.

- 2. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-091B

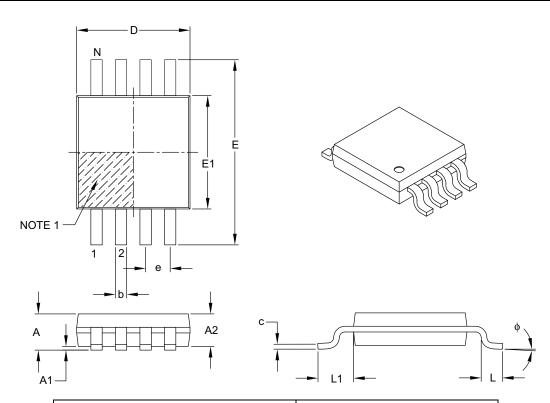

## 8-Lead Plastic Micro Small Outline Package (MS) [MSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units     | MILLIMETERS |          |      |  |

|--------------------------|-----------|-------------|----------|------|--|

| Dimension                | on Limits | MIN         | NOM      | MAX  |  |

| Number of Pins           | N         |             | 8        |      |  |

| Pitch                    | е         |             | 0.65 BSC |      |  |

| Overall Height           | Α         | _           | -        | 1.10 |  |

| Molded Package Thickness | A2        | 0.75        | 0.85     | 0.95 |  |

| Standoff                 | A1        | 0.00        | -        | 0.15 |  |

| Overall Width            | Е         | 4.90 BSC    |          |      |  |

| Molded Package Width     | E1        | 3.00 BSC    |          |      |  |

| Overall Length           | D         |             | 3.00 BSC |      |  |

| Foot Length              | L         | 0.40        | 0.60     | 0.80 |  |

| Footprint                | L1        | 0.95 REF    |          |      |  |

| Foot Angle               | ф         | 0°          | _        | 8°   |  |

| Lead Thickness           | С         | 0.08        | _        | 0.23 |  |

| Lead Width               | b         | 0.22        | _        | 0.40 |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15 mm per side.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-111B

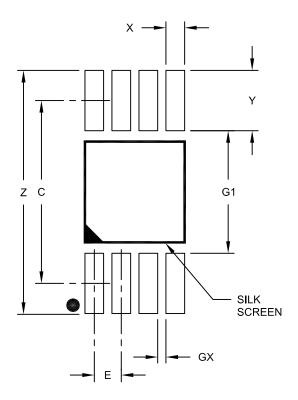

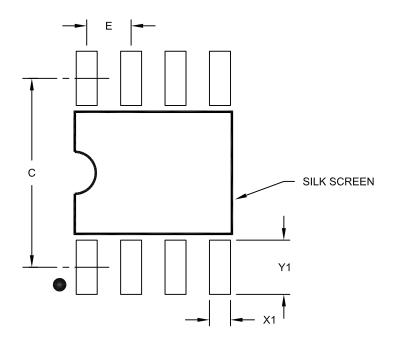

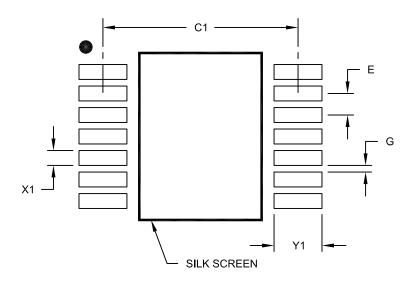

#### 8-Lead Plastic Micro Small Outline Package (MS) [MSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

|                         | Units  |      |          | S    |

|-------------------------|--------|------|----------|------|

| Dimension               | Limits | MIN  | NOM      | MAX  |

| Contact Pitch           | E      |      | 0.65 BSC |      |

| Contact Pad Spacing     | C      |      | 4.40     |      |

| Overall Width           | Z      |      |          | 5.85 |

| Contact Pad Width (X8)  | X1     |      |          | 0.45 |

| Contact Pad Length (X8) | Y1     |      |          | 1.45 |

| Distance Between Pads   | G1     | 2.95 |          |      |

| Distance Between Pads   | GX     | 0.20 |          |      |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2111A

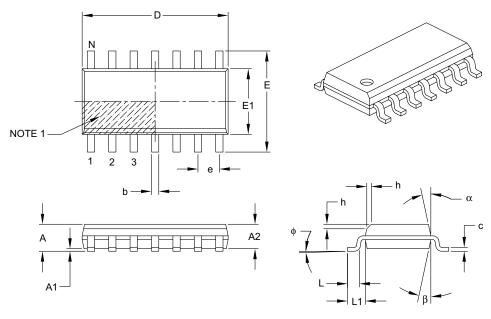

### 8-Lead Plastic Small Outline (SN) - Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units          |          | MILLIMETERS | 3    |

|--------------------------|----------------|----------|-------------|------|

| Di                       | mension Limits | MIN      | NOM         | MAX  |

| Number of Pins           | N              |          | 8           |      |

| Pitch                    | е              |          | 1.27 BSC    |      |

| Overall Height           | Α              | ı        | _           | 1.75 |

| Molded Package Thickness | A2             | 1.25     | _           | ı    |

| Standoff §               | A1             | 0.10     | _           | 0.25 |

| Overall Width            | E              | 6.00 BSC |             |      |

| Molded Package Width     | E1             | 3.90 BSC |             |      |

| Overall Length           | D              | 4.90 BSC |             |      |

| Chamfer (optional)       | h              | 0.25     | _           | 0.50 |

| Foot Length              | L              | 0.40     | _           | 1.27 |

| Footprint                | L1             | 1.04 REF |             |      |

| Foot Angle               | ф              | 0°       | _           | 8°   |

| Lead Thickness           | С              | 0.17     | _           | 0.25 |

| Lead Width               | b              | 0.31     | _           | 0.51 |

| Mold Draft Angle Top     | α              | 5°       | _           | 15°  |

| Mold Draft Angle Bottom  | β              | 5°       | _           | 15°  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-057B

## 8-Lead Plastic Small Outline (SN) - Narrow, 3.90 mm Body [SOIC]

**Ste:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

| Units                   |    | MILLIMETERS |          |      |

|-------------------------|----|-------------|----------|------|

| Dimension Limits        |    | MIN         | NOM      | MAX  |

| Contact Pitch           | E  |             | 1.27 BSC |      |

| Contact Pad Spacing     | С  |             | 5.40     |      |

| Contact Pad Width (X8)  | X1 |             |          | 0.60 |

| Contact Pad Length (X8) | Y1 |             |          | 1.55 |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2057A

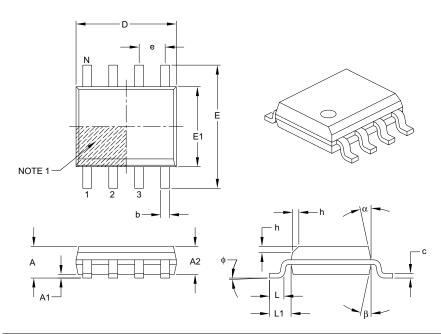

### 14-Lead Plastic Small Outline (SL) - Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units            |          | MILLIMETERS | 3    |

|--------------------------|------------------|----------|-------------|------|

|                          | Dimension Limits | MIN      | NOM         | MAX  |

| Number of Pins           | N                |          | 14          |      |

| Pitch                    | е                |          | 1.27 BSC    |      |

| Overall Height           | A                | _        | _           | 1.75 |

| Molded Package Thickness | A2               | 1.25     | _           | _    |

| Standoff §               | A1               | 0.10     | _           | 0.25 |

| Overall Width            | E                |          | 6.00 BSC    |      |

| Molded Package Width     | E1               |          | 3.90 BSC    |      |

| Overall Length           | D                |          | 8.65 BSC    |      |

| Chamfer (optional)       | h                | 0.25     | _           | 0.50 |

| Foot Length              | L                | 0.40     | _           | 1.27 |

| Footprint                | L1               | 1.04 REF |             |      |

| Foot Angle               | ф                | 0°       | _           | 8°   |

| Lead Thickness           | С                | 0.17     | _           | 0.25 |

| Lead Width               | b                | 0.31     | _           | 0.51 |

| Mold Draft Angle Top     | α                | 5°       | _           | 15°  |

| Mold Draft Angle Bottom  | β                | 5°       | _           | 15°  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-065B

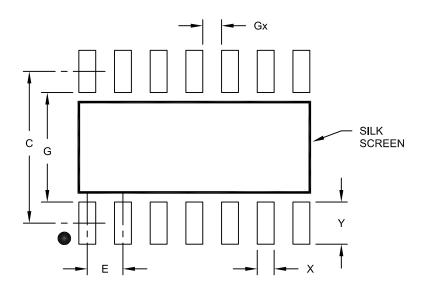

## 14-Lead Plastic Small Outline (SL) - Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

|                       | Units            | N    | <b>IILLIMETER</b> | S    |

|-----------------------|------------------|------|-------------------|------|

| Dimension             | Dimension Limits |      | NOM               | MAX  |

| Contact Pitch         | Е                |      | 1.27 BSC          |      |

| Contact Pad Spacing   | С                |      | 5.40              |      |

| Contact Pad Width     | Х                |      |                   | 0.60 |

| Contact Pad Length    | Υ                |      |                   | 1.50 |

| Distance Between Pads | Gx               | 0.67 |                   |      |

| Distance Between Pads | G                | 3.90 |                   |      |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2065A

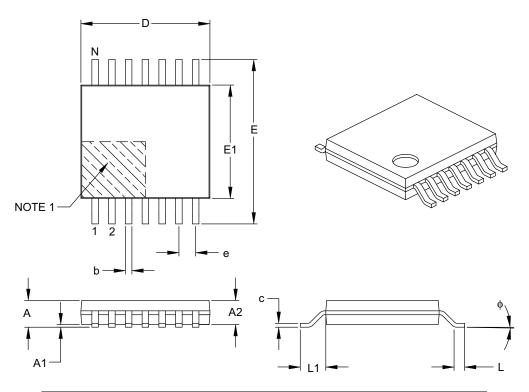

### 14-Lead Plastic Thin Shrink Small Outline (ST) – 4.4 mm Body [TSSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units    |          | MILLIMETERS | 3    |

|--------------------------|----------|----------|-------------|------|

| Dimension                | n Limits | MIN      | NOM         | MAX  |

| Number of Pins           | N        |          | 14          |      |

| Pitch                    | е        |          | 0.65 BSC    |      |

| Overall Height           | Α        | _        | _           | 1.20 |

| Molded Package Thickness | A2       | 0.80     | 1.00        | 1.05 |

| Standoff                 | A1       | 0.05     | _           | 0.15 |

| Overall Width            | Е        | 6.40 BSC |             |      |

| Molded Package Width     | E1       | 4.30     | 4.40        | 4.50 |

| Molded Package Length    | D        | 4.90     | 5.00        | 5.10 |

| Foot Length              | L        | 0.45     | 0.60        | 0.75 |

| Footprint                | L1       | 1.00 REF |             |      |

| Foot Angle               | ф        | 0°       | _           | 8°   |

| Lead Thickness           | С        | 0.09     | _           | 0.20 |

| Lead Width               | b        | 0.19     | _           | 0.30 |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15 mm per side.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

${\tt BSC: Basic \ Dimension. \ Theoretically \ exact \ value \ shown \ without \ tolerances.}$

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-087B

#### 14-Lead Plastic Thin Shrink Small Outline (ST) - 4.4 mm Body [TSSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### **RECOMMENDED LAND PATTERN**

| Units                    |    | MILLIMETERS |          |      |

|--------------------------|----|-------------|----------|------|

| Dimension Limits         |    | MIN         | NOM      | MAX  |

| Contact Pitch            | Е  |             | 0.65 BSC |      |

| Contact Pad Spacing      | C1 |             | 5.90     |      |

| Contact Pad Width (X28)  | X1 |             |          | 0.45 |

| Contact Pad Length (X28) | Y1 |             |          | 1.45 |

| Distance Between Pads    | G  | 0.20        |          |      |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2087A

NOTES:

#### APPENDIX A: REVISION HISTORY

### **Revision B (August 2009)**

The following is the list of modifications:

- 1. Added MCP6566U throughout the document.

- 2. Updated package outline drawings.

### Revision A (March 2009)

• Original Release of this Document.

NOTES:

#### PRODUCT IDENTIFICATION SYSTEM

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO           | <u>х</u> / <u>х</u> х                                                                                                                                        | Examples:                                                                        |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| •                 | <br>erature Package<br>nge                                                                                                                                   | a) MCP6566T-E/LT: Tape and Reel,<br>Extended Temperature,<br>5LD SC70 package.   |

| Device            | MCP6566T: Single Comparator (Tape and Reel) (SC70, SOT-23)                                                                                                   | b) MCP6566T-E/OT: Tape and Reel Extended Temperature, 5LD SOT-23 package.        |

|                   | MCP6566RT: Single Comparator (Tape and Reel) (SOT-23 only)  MCP6566UT: Single Comparator (Tape and Reel) (SOT-23 only)                                       | a) MCP6566RT-E/OT: Tape and Reel<br>Extended Temperature,<br>5LD SOT-23 package. |

|                   | MCP6567: Dual Comparator MCP6567T: Dual Comparator(Tape and Reel) MCP6569: Quad Comparator MCP6569T: Quad Comparator(Tape and Reel)                          | a) MCP6566UT-E/OT: Tape and Reel<br>Extended Temperature,<br>5LD SOT-23 package. |

| Temperature Range | E = -40°C to +125°C                                                                                                                                          | a) MCP6567-E/MS: Extended Temperature 8LD MSOP package.                          |

| Package           | LT = Plastic Small Outline Transistor (SC70), 5-lead OT = Plastic Small Outline Transistor (SOT-23), 5-lead                                                  | b) MCP6567-E/SN: Extended Temperature 8LD SOIC package.                          |

|                   | MS = Plastic Micro Small Outline Transistor, 8-lead SN = Plastic Small Outline Transistor, 8-lead ST = Plastic Thin Shrink Small Outline Transistor, 14-lead | a) MCP6569T-E/SL: Tape and Reel<br>Extended Temperature<br>14LD SOIC package.    |

|                   | SL = Plastic Small Outline Transistor, 14-lead                                                                                                               | b) MCP6569T-E/ST: Tape and Reel Extended Temperature 14LD TSSOP package.         |

NOTES:

#### Note the following details of the code protection feature on Microchip devices:

- · Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the

intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our

knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data

Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

#### **Trademarks**

The Microchip name and logo, the Microchip logo, dsPIC, Keeloq, Keeloq logo, MPLAB, PIC, PICmicro, PICSTART, rfPIC and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MXDEV, MXLAB, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Octopus, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, PIC<sup>32</sup> logo, REAL ICE, rfLAB, Select Mode, Total Endurance, TSHARC, UniWinDriver, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

$\ensuremath{\mathsf{SQTP}}$  is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2009, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

QUALITY MANAGEMENT SYSTEM

CERTIFIED BY DNV

ISO/TS 16949:2002

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

## WORLDWIDE SALES AND SERVICE

#### **AMERICAS**

Corporate Office

2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277

Technical Support:

http://support.microchip.com

Web Address: www.microchip.com

**Atlanta**

Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

**Boston**

Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca. IL

Tel: 630-285-0071 Fax: 630-285-0075

Cleveland

Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas**

Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit

Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Kokomo

Kokomo, IN Tel: 765-864-8360 Fax: 765-864-8387

Los Angeles

Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara

Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto

Mississauga, Ontario,

Canada Tel: 905-673-0699

Fax: 905-673-6509

#### ASIA/PACIFIC

**Asia Pacific Office**

Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon

Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431

**Australia - Sydney** Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

China - Beijing

Tel: 86-10-8528-2100 Fax: 86-10-8528-2104

China - Chengdu

Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Hong Kong SAR

Tel: 852-2401-1200 Fax: 852-2401-3431

China - Nanjing

Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

China - Qingdao

Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

China - Shanghai

Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

China - Shenyang

Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

China - Shenzhen

Tel: 86-755-8203-2660 Fax: 86-755-8203-1760

China - Wuhan

Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

China - Xiamen

Tel: 86-592-2388138 Fax: 86-592-2388130

China - Xian

Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

China - Zhuhai

Tel: 86-756-3210040 Fax: 86-756-3210049

#### ASIA/PACIFIC

India - Bangalore

Tel: 91-80-3090-4444 Fax: 91-80-3090-4080

India - New Delhi

Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune

Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

Japan - Yokohama

Tel: 81-45-471- 6166 Fax: 81-45-471-6122

Korea - Daegu

Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul

Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur

Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang

Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila

Tel: 63-2-634-9065 Fax: 63-2-634-9069

Singapore

Tel: 65-6334-8870 Fax: 65-6334-8850

Taiwan - Hsin Chu

Tel: 886-3-6578-300 Fax: 886-3-6578-370 Taiwan - Kaohsiung

Tel: 886-7-536-4818

Fax: 886-7-536-4803

Taiwan - Taipei

Tel: 886-2-2500-6610 Fax: 886-2-2508-0102

Thailand - Bangkok

Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### **EUROPE**

Austria - Wels

Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 Denmark - Copenhagen

Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris

Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Germany - Munich

Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Italy - Milan

Tel: 39-0331-742611 Fax: 39-0331-466781

Netherlands - Drunen

Tel: 31-416-690399 Fax: 31-416-690340

Spain - Madrid

Tel: 34-91-708-08-90 Fax: 34-91-708-08-91 UK - Wokingham

Tel: 44-118-921-5869 Fax: 44-118-921-5820

03/26/09