# Overvoltage Crowbar Sensing Circuit

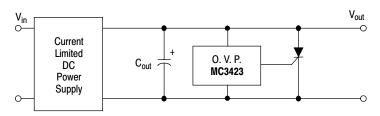

This overvoltage protection circuit (OVP) protects sensitive electronic circuitry from overvoltage transients or regulator failures when used in conjunction with an external "crowbar" SCR. The device senses the overvoltage condition and quickly "crowbars" or short circuits the supply, forcing the supply into current limiting or opening the fuse or circuit breaker.

The protection voltage threshold is adjustable and the MC3423 can be programmed for minimum duration of overvoltage condition before tripping, thus supplying noise immunity.

The MC3423 is essentially a "two terminal" system, therefore it can be used with either positive or negative supplies.

# **Features**

• Pb-Free Package is Available

#### **MAXIMUM RATINGS**

| Rating                              | Symbol                           | Value       | Unit |

|-------------------------------------|----------------------------------|-------------|------|

| Differential Power Supply Voltage   | V <sub>CC</sub> -V <sub>EE</sub> | 40          | Vdc  |

| Sense Voltage (1)                   | V <sub>Sense1</sub>              | 6.5         | Vdc  |

| Sense Voltage (2)                   | V <sub>Sense2</sub>              | 6.5         | Vdc  |

| Remote Activation Input Voltage     | V <sub>act</sub>                 | 7.0         | Vdc  |

| Output Current                      | I <sub>O</sub>                   | 300         | mA   |

| Operating Ambient Temperature Range | T <sub>A</sub>                   | 0 to +70    | °C   |

| Operating Junction Temperature      | TJ                               | 125         | °C   |

| Storage Temperature Range           | T <sub>stg</sub>                 | -65 to +150 | °C   |

Maximum ratings are those values beyond which device damage can occur. Maximum ratings applied to the device are individual stress limit values (not normal operating conditions) and are not valid simultaneously. If these limits are exceeded, device functional operation is not implied, damage may occur and reliability may be affected.

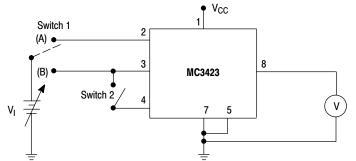

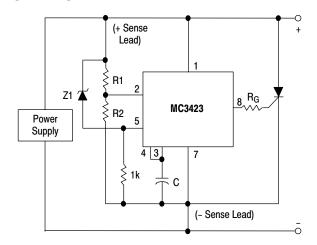

Figure 1. Simplified Application

http://onsemi.com

MARKING DIAGRAMS

MC3423P1 = Device Code A = Assembly Location

WL = Wafer Lot YY = Year WW = Work Week

3423 = Device Code A = Assembly Location

L = Wafer Lot

Y = Year

W = Work Week

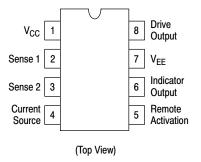

#### PIN CONNECTIONS

### **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 7 of this data sheet.

$\textbf{ELECTRICAL CHARACTERISTICS} \ (5.0 \ V \leq V_{CC} - V_{EE} \leq 36 \ V, \ T_{low} < T_{A} \ , \ T_{high}, \ unless \ otherwise \ noted.)$

| Characteristics                                                                                                                                         | Symbol                                       | Min                  | Тур                  | Max        | Unit  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|----------------------|----------------------|------------|-------|

| Supply Voltage Range                                                                                                                                    | V <sub>CC</sub> -V <sub>EE</sub>             | 4.5                  | _                    | 40         | Vdc   |

| Output Voltage (I <sub>O</sub> = 100 mA)                                                                                                                | Vo                                           | V <sub>CC</sub> -2.2 | V <sub>CC</sub> -1.8 | -          | Vdc   |

| Indicator Output Voltage (I <sub>O(Ind)</sub> = 1.6 mA)                                                                                                 | V <sub>OL</sub> (Ind)                        | -                    | 0.1                  | 0.4        | Vdc   |

| Sense Trip Voltage (T <sub>A</sub> = 25°C)                                                                                                              | V <sub>Sense1</sub> ,<br>V <sub>Sense2</sub> | 2.45                 | 2.6                  | 2.75       | Vdc   |

| Temperature Coefficient of V <sub>Sense1</sub> (Figure 2)                                                                                               | TCV <sub>S1</sub>                            | -                    | 0.06                 | -          | %/°C  |

| Remote Activation Input Current $(V_{IH} = 2.0 \text{ V}, V_{CC} - V_{EE} = 5.0 \text{ V})$ $(V_{IL} = 0.8 \text{ V}, V_{CC} - V_{EE} = 5.0 \text{ V})$ | I <sub>IH</sub>                              | -<br>-               | 5.0<br>–120          | 40<br>–180 | μΑ    |

| Source Current                                                                                                                                          | I <sub>Source</sub>                          | 0.1                  | 0.2                  | 0.3        | mA    |

| Output Current Risetime (T <sub>A</sub> = 25°C)                                                                                                         | t <sub>r</sub>                               | -                    | 400                  | _          | mA/μs |

| Propagation Delay Time (T <sub>A</sub> = 25°C)                                                                                                          | t <sub>pd</sub>                              | -                    | 0.5                  | _          | μs    |

| Supply Current                                                                                                                                          | I <sub>D</sub>                               | -                    | 6.0                  | 10         | mA    |

NOTES:  $T_{low}$  to  $T_{high} = 0^{\circ}$  to  $+70^{\circ}$ C

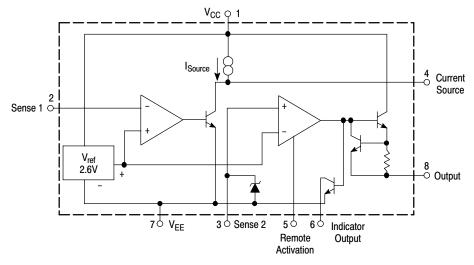

Figure 2. Representative Block Diagram

|                      | Switch 1   | Switch 2 |

|----------------------|------------|----------|

| V <sub>Sense 1</sub> | Position A | Closed   |

| V <sub>Sense 2</sub> | Position B | Open     |

Ramp  $V_{I}$  until output goes high; this is the  $V_{Sense}$  threshold.

Figure 3. Sense Voltage Test Circuit

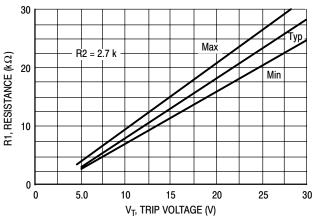

$$V_{trip} \,=\, V_{ref} \left(1 \,+\, \frac{R1}{R2}\right) \,\,\approx\, 2.6 \; V \left(1 \,+\, \frac{R1}{R2}\right) \label{eq:Vtrip}$$

$R2 \leq 10~k\Omega$  for minimum drift

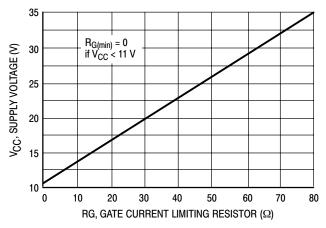

For minimum value of R<sub>G</sub>, see Figure 9.

\*See text for explanation.

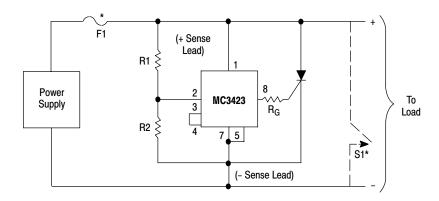

Figure 4. Basic Circuit Configuration

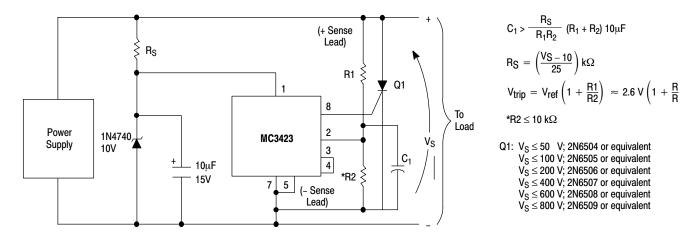

Figure 5. Circuit Configuration for Supply Voltage Above 36 V

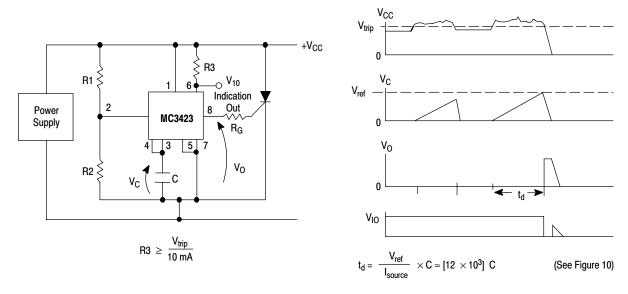

Figure 6. Basic Configuration for Programmable Duration of Overvoltage Condition Before Trip

# APPLICATION INFORMATION

# **Basic Circuit Configuration**

The basic circuit configuration of the MC3423 OVP is shown in Figure 3 for supply voltages from 4.5 V to 36 V. and in Figure 4 for trip voltages above 36 V. The threshold or trip voltage at which the MC3423 will trigger and supply gate drive to the crowbar SCR, Q1, is determined by the selection of R1 and R2. Their values can be determined by the equation given in Figures 3 and 4, or by the graph shown in Figure 8. The minimum value of the gate current limiting resistor, R<sub>G</sub>, is given in Figure 9. Using this value of R<sub>G</sub>, the SCR, Q1, will receive the greatest gate current possible without damaging the MC3423. If lower output currents are required, R<sub>G</sub> can be increased in value. The switch, S1, shown in Figure 3 may be used to reset the crowbar. Otherwise, the power supply, across which the SCR is connected, must be shut down to reset the crowbar. If a non current-limited supply is used, a fuse or circuit breaker, F1, should be used to protect the SCR and/or the load.

The circuit configurations shown in Figures 3 and 4 will have a typical propagating delay of  $1.0~\mu s$ . If faster operation is desired, Pin 3 may be connected to Pin 2 with Pin 4 left floating. This will result in decreasing the propagating delay to approximately  $0.5~\mu s$  at the expense of a slightly increased TC for the trip voltage value.

# Configuration for Programmable Minimum Duration of Overvoltage Condition Before Tripping

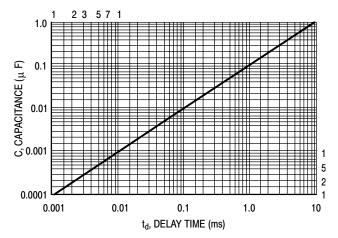

In many instances, the MC3423 OVP will be used in a noise environment. To prevent false tripping of the OVP circuit by noise which would not normally harm the load, MC3423 has a programmable delay feature. To implement this feature, the circuit configuration of Figure 5 is used. In this configuration, a capacitor is connected from Pin 3 to V<sub>EE</sub>. The value of this capacitor determines the minimum duration of the overvoltage condition which is necessary to trip the OVP. The value of C can be found from Figure 10. The circuit operates in the following manner: When V<sub>CC</sub> rises above the trip point set by R1 and R2, an internal current source (Pin 4) begins charging the capacitor, C, connected to Pin 3. If the overvoltage condition disappears before this occurs, the capacitor is discharged at a rate  $\cong 10$ times faster than the charging rate, resetting the timing feature until the next overvoltage condition occurs.

Occasionally, it is desired that immediate crowbarring of the supply occur when a high overvoltage condition occurs, while retaining the false tripping immunity of Figure 5. In this case, the circuit of Figure 6 can be used. The circuit will operate as previously described for small overvoltages, but will immediately trip if the power supply voltage exceeds  $V_{Z1} + 1.4\ V$ .

Figure 7. Configuration for Programmable

Duration of Overvoltage Condition Before

Trip/With Immediate Trip at

High Overvoltages

#### **Additional Features**

# 1. Activation Indication Output

An additional output for use as an indicator of OVP activation is provided by the MC3423. This output is an open collector transistor which saturates when the OVP is activated. In addition, it can be used to clock an edge triggered flip—flop whose output inhibits or shuts down the power supply when the OVP trips. This reduces or eliminates the heatsinking requirements for the crowbar SCR.

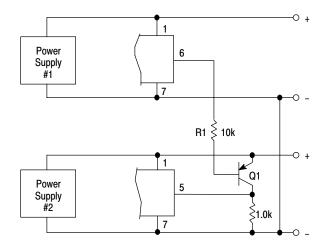

# 2. Remote Activation Input

Another feature of the MC3423 is its remote activation input, Pin 5. If the voltage on this CMOS/TTL compatible input is held below 0.8 V, the MC3423 operates normally. However, if it is raised to a voltage above 2.0 V, the OVP output is activated independent of whether or not an overvoltage condition is present. It should be noted that Pin 5 has an internal pullup current source. This feature can be used to accomplish an orderly and sequenced shutdown of system power supplies during a system fault condition. In addition, the activation indication output of one MC3423 can be used to activate another MC3423 if a single transistor inverter is used to interface the former's indication output to the latter's remote activation input, as shown in Figure 7. In this circuit, the indication output (Pin 6) of the MC3423 on power supply 1 is used to activate the MC3423 associated with power supply 2. Q1 is any small PNP with adequate voltage rating.

Figure 8. Circuit Configuration for Activating One MC3423 from Another

Note that both supplies have their negative output leads tied together (i.e., both are positive supplies). If their positive leads are common (two negative supplies) the emitter of Q1 would be moved to the positive lead of supply 1 and R1 would therefore have to be resized to deliver the appropriate drive to Q1.

# **Crowbar SCR Considerations**

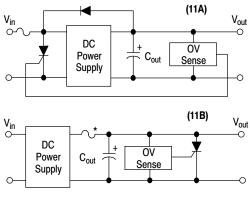

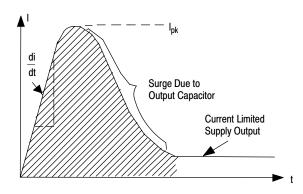

Referring to Figure 11, it can be seen that the crowbar SCR, when activated, is subject to a large current surge from the output capacitance, Cout. This capacitance consists of the power supply output caps, the load's decoupling caps, and in the case of Figure 11A, the supply's input filter caps. This surge current is illustrated in Figure 12, and can cause SCR failure or degradation by any one of three mechanisms: di/dt, absolute peak surge, or I<sup>2</sup>t. The interrelationship of these failure methods and the breadth of the applications make specification of the SCR by the semiconductor manufacturer difficult and expensive. Therefore, the designer must empirically determine the SCR and circuit elements which result in reliable and effective OVP operation. However, an understanding of the factors which influence the SCR's di/dt and surge capabilities simplifies this task.

# di/dt

As the gate region of the SCR is driven on, its area of conduction takes a finite amount of time to grow, starting as a very small region and gradually spreading. Since the anode current flows through this turned—on gate region, very high current densities can occur in the gate region if high anode currents appear quickly (di/dt). This can result in immediate destruction of the SCR or gradual degradation of its forward blocking voltage capabilities—depending on the severity of the occasion.

Figure 9. R1 versus Trip Voltage

Figure 10. Minimum R<sub>G</sub> versus Supply Voltage

Figure 11. Capacitance versus Minimum Overvoltage Duration

\*Needed if supply not current limited

Figure 12. Typical Crowbar OVP Circuit Configurations

Figure 13. Crowbar SCR Surge Current Waveform

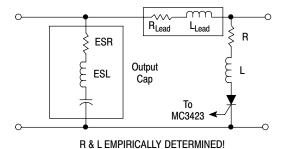

Figure 14. Circuit Elements Affecting SCR Surge and di/dt

The usual design compromise then is to use a garden variety fuse (3AG or 3AB style) which cannot be relied on to blow before the thyristor does, and trust that if the SCR does fail, it will fail short circuit. In the majority of the designs, this will be the case, though this is difficult to guarantee. Of course, a sufficiently high surge will cause an open. These comments also apply to the fuse in Figure 11B.

The value of di/dt that an SCR can safely handle is influenced by its construction and the characteristics of the

gate drive signal. A center–gate–fire SCR has more di/dt capability than a corner–gate–fire type, and heavily overdriving (3 to 5 times  $I_{GT}$ ) the SCR gate with a fast  $<1.0~\mu s$  rise time signal will maximize its di/dt capability. A typical maximum number in phase control SCRs of less than 50 A(RMS) rating might be 200 A/ $\mu s$ , assuming a gate current of five times  $I_{GT}$  and  $<1.0~\mu s$  rise time. If having done this, a di/dt problem is seen to still exist, the designer can also decrease the di/dt of the current waveform by adding inductance in series with the SCR, as shown in Figure 13. Of course, this reduces the circuit's ability to rapidly reduce the DC bus voltage and a tradeoff must be made between speedy voltage reduction and di/dt.

# **Surge Current**

If the peak current and/or the duration of the surge is excessive, immediate destruction due to device overheating will result. The surge capability of the SCR is directly proportional to its die area. If the surge current cannot be reduced (by adding series resistance – see Figure 13) to a safe level which is consistent with the systems requirements for speedy bus voltage reduction, the designer must use a higher current SCR. This may result in the average current capability of the SCR exceeding the steady state current requirements imposed by the DC power supply.

#### A WORD ABOUT FUSING

Before leaving the subject of the crowbar SCR, a few words about fuse protection are in order. Referring back to Figure 11A, it will be seen that a fuse is necessary if the power supply to be protected is not output current limited. This fuse is not meant to prevent SCR failure but rather to prevent a fire!

In order to protect the SCR, the fuse would have to possess an I<sup>2</sup>t rating less than that of the SCR and yet have a high enough continuous current rating to survive normal supply output currents. In addition, it must be capable of successfully clearing the high short circuit currents from the supply. Such a fuse as this is quite expensive, and may not even be available.

# **CROWBAR SCR SELECTION GUIDE**

As an aid in selecting an SCR for crowbar use, the following selection guide is presented.

| Device           | I <sub>RMS</sub> | I <sub>FSM</sub> | Package         |

|------------------|------------------|------------------|-----------------|

| 2N6400 Series    | 16 A             | 160 A            | TO-220 Plastic  |

| 2N6504 Series    | 25 A             | 160 A            | TO-220 Plastic  |

| 2N1842 Series    | 16 A             | 125 A            | Metal Stud      |

| 2N2573 Series    | 25 A             | 260 A            | Metal TO-3 Type |

| 2N681 Series     | 25 A             | 200 A            | Metal Stud      |

| MCR3935-1 Series | 35 A             | 350 A            | Metal Stud      |

| MCR81-5 Series   | 80 A             | 1000 A           | Metal Stud      |

# **ORDERING INFORMATION**

| Device     | Operating Temperature Range                       | Package             | Shipping <sup>†</sup> |

|------------|---------------------------------------------------|---------------------|-----------------------|

| MC3423D    |                                                   | SOIC-8              | 98 Units / Rail       |

| MC3423DG   |                                                   | SOIC-8<br>(Pb-Free) | 98 Units / Rail       |

| MC3423DR2  | 1                                                 | SOIC-8              | 2500 Tape & Reel      |

| MC3423DR2G | $T_A = 0^{\circ} \text{ to } +70^{\circ}\text{C}$ | SOIC-8<br>(Pb-Free) | 2500 Tape & Reel      |

| MC3423P1   |                                                   | PDIP-8              | 1000 Units / Rail     |

| MC3423P1G  |                                                   | PDIP-8<br>(Pb-Free) | 1000 Units / Rail     |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

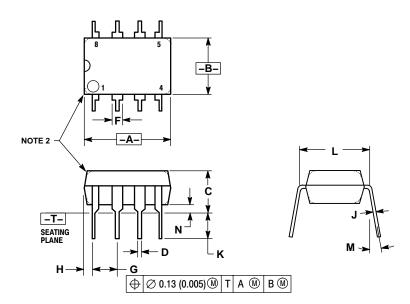

# **PACKAGE DIMENSIONS**

PDIP-8 P1 SUFFIX CASE 626-05 ISSUE L

- NOTES:

1. DIMENSION L TO CENTER OF LEAD WHEN FORMED PARALLEL.

2. PACKAGE CONTOUR OPTIONAL (ROUND OR SQUARE CORNERS).

3. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

|     | MILLIMETERS |       | INCHES    |       |

|-----|-------------|-------|-----------|-------|

| DIM | MIN         | MAX   | MIN       | MAX   |

| Α   | 9.40        | 10.16 | 0.370     | 0.400 |

| В   | 6.10        | 6.60  | 0.240     | 0.260 |

| С   | 3.94        | 4.45  | 0.155     | 0.175 |

| D   | 0.38        | 0.51  | 0.015     | 0.020 |

| F   | 1.02        | 1.78  | 0.040     | 0.070 |

| G   | 2.54 BSC    |       | 0.100 BSC |       |

| Н   | 0.76        | 1.27  | 0.030     | 0.050 |

| J   | 0.20        | 0.30  | 0.008     | 0.012 |

| K   | 2.92        | 3.43  | 0.115     | 0.135 |

| L   | 7.62 BSC    |       | 0.300 BSC |       |

| M   |             | 10°   |           | 10°   |

| N   | 0.76        | 1.01  | 0.030     | 0.040 |

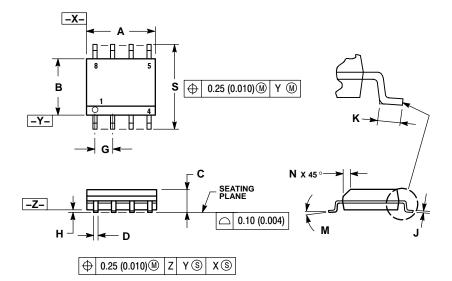

# SOIC-8 **D SUFFIX** CASE 751-07 **ISSUE AE**

#### NOTES:

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

2. CONTROLLING DIMENSION: MILLIMETER.

3. DIMENSION A AND B DO NOT INCLUDE MOLD PROTRUSION.

4. MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER SIDE.

- PER SIDE.

5. DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127 (0.005) TOTAL IN EXCESS OF THE D DIMENSION AT

- MAXIMUM MATERIAL CONDITION.

6. 751–01 THRU 751–06 ARE OBSOLETE. NEW STANDARD IS 751–07.

|     | MILLIMETERS |      | INCHES    |       |

|-----|-------------|------|-----------|-------|

| DIM | MIN         | MAX  | MIN       | MAX   |

| Α   | 4.80        | 5.00 | 0.189     | 0.197 |

| В   | 3.80        | 4.00 | 0.150     | 0.157 |

| U   | 1.35        | 1.75 | 0.053     | 0.069 |

| D   | 0.33        | 0.51 | 0.013     | 0.020 |

| G   | 1.27 BSC    |      | 0.050 BSC |       |

| Н   | 0.10        | 0.25 | 0.004     | 0.010 |

| J   | 0.19        | 0.25 | 0.007     | 0.010 |

| K   | 0.40        | 1.27 | 0.016     | 0.050 |

| М   | 0 °         | 8 °  | 0 °       | 8 °   |

| N   | 0.25        | 0.50 | 0.010     | 0.020 |

| s   | 5.80        | 6.20 | 0.228     | 0.244 |

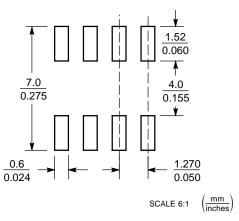

# **SOLDERING FOOTPRINT\***

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any iability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

# **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 61312, Phoenix, Arizona 85082–1312 USA Phone: 480–829–7710 or 800–344–3860 Toll Free USA/Canada Fax: 480–829–7709 or 800–344–3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800–282–9855 Toll Free LISA/Canada

Japan: ON Semiconductor, Japan Customer Focus Center 2–9–1 Kamimeguro, Meguro–ku, Tokyo, Japan 153–0051 Phone: 81–3–5773–3850

ON Semiconductor Website: http://onsemi.com

Order Literature: http://www.onsemi.com/litorder

For additional information, please contact your local Sales Representative.