## 10-Bit, 80Msps Low Noise 3V ADC

### **FEATURES**

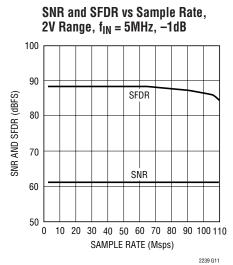

Sample Rate: 80Msps

■ Single 3V Supply (2.7V to 3.4V)

■ Low Power: 211mW

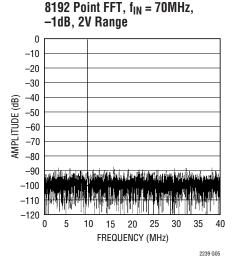

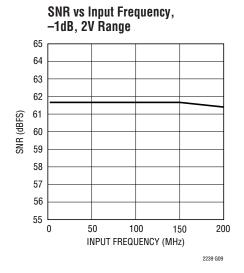

61.6dB SNR at 70MHz Input

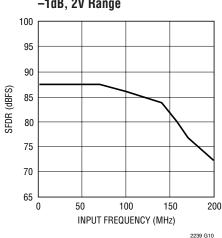

■ 85dB SFDR at 70MHz Input

No Missing Codes

■ Flexible Input: 1V<sub>P-P</sub> to 2V<sub>P-P</sub> Range

■ 575MHz Full Power Bandwidth S/H

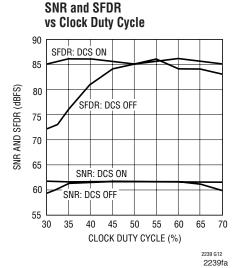

Clock Duty Cycle Stabilizer

Shutdown and Nap Modes

■ Pin Compatible Family

125Msps: LTC2253 (12-Bit), LTC2251 (10-Bit) 105Msps: LTC2252 (12-Bit), LTC2250 (10-Bit) 80Msps: LTC2229 (12-Bit), LTC2239 (10-Bit) 65Msps: LTC2228 (12-Bit), LTC2238 (10-Bit) 40Msps: LTC2237 (12-Bit), LTC2237 (10-Bit)

40Msps: LTC2227 (12-Bit), LTC2237 (10-Bit)

25Msps: LTC2226 (12-Bit), LTC2236 (10-Bit)

10Msps: LTC2225 (12-Bit)

■ 32-Pin (5mm × 5mm) QFN Package

## **APPLICATIONS**

- Wireless and Wired Broadband Communication

- Imaging Systems

- Ultrasound

- Spectral Analysis

- Portable Instrumentation

## DESCRIPTION

The LTC®2239 is a 10-bit 80Msps, low power 3V A/D converter designed for digitizing high frequency, wide dynamic range signals. The LTC2239 is perfect for demanding imaging and communications applications with AC performance that includes 61.6dB SNR and 85dB SFDR for signals well beyond the Nyquist frequency.

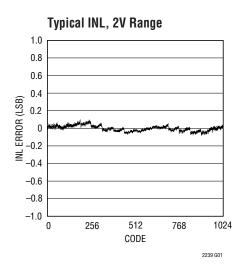

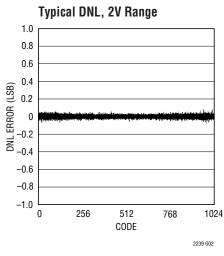

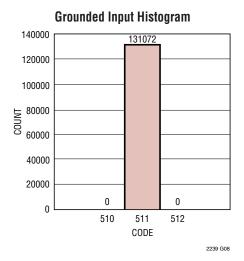

DC specs include  $\pm 0.1$ LSB INL (typ),  $\pm 0.1$ LSB DNL (typ) and  $\pm 0.5$ LSB INL,  $\pm 0.5$ LSB DNL over temperature. The transition noise is a low 0.08LSB<sub>RMS</sub>.

A single 3V supply allows low power operation. A separate output supply allows the outputs to drive 0.5V to 3.6V logic.

A single-ended CLK input controls converter operation. An optional clock duty cycle stabilizer allows high performance at full speed for a wide range of clock duty cycles.

LTC and LT are registered trademarks of Linear Technology Corporation.

All other trademarks are the property of their respective owners.

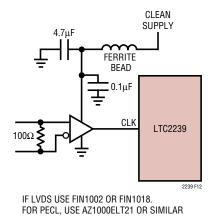

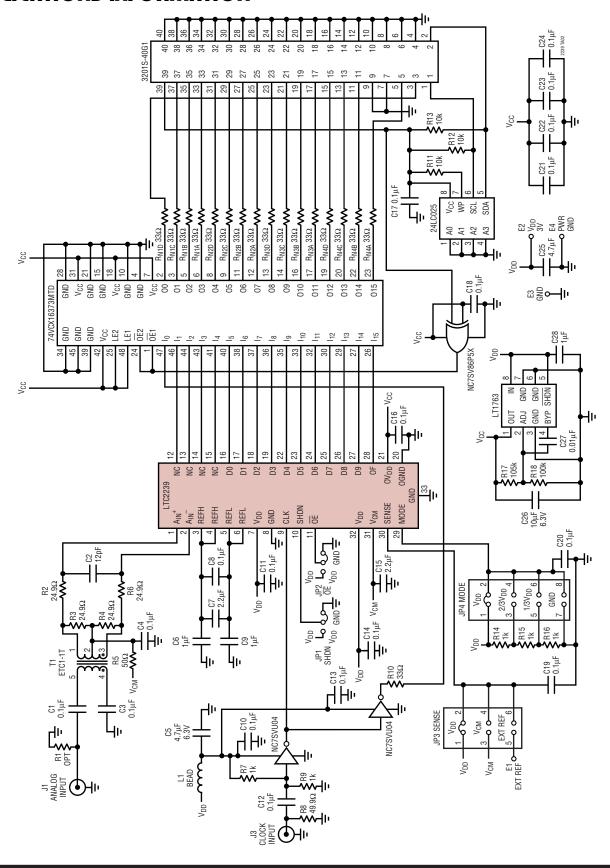

## TYPICAL APPLICATION

2239fa

## **ABSOLUTE MAXIMUM RATINGS**

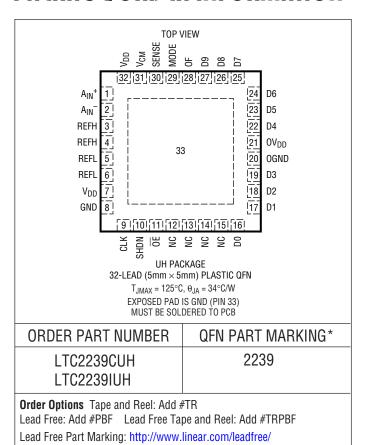

## PACKAGE/ORDER INFORMATION

Consult LTC Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container.

# **CONVERTER CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25 \,^{\circ}\text{C}$ . (Note 4)

| PARAMETER                     | CONDITIONS                               |   | MIN  | TYP       | MAX | UNITS              |

|-------------------------------|------------------------------------------|---|------|-----------|-----|--------------------|

| Resolution (No Missing Codes) |                                          | • | 10   |           |     | Bits               |

| Integral Linearity Error      | Differential Analog Input (Note 5)       | • | -0.5 | ±0.1      | 0.5 | LSB                |

| Differential Linearity Error  | Differential Analog Input                | • | -0.5 | ±0.1      | 0.5 | LSB                |

| Offset Error                  | (Note 6)                                 | • | -12  | <u>+2</u> | 12  | mV                 |

| Gain Error                    | External Reference                       | • | -2.5 | ±0.5      | 2.5 | %FS                |

| Offset Drift                  |                                          |   |      | ±10       |     | μV/°C              |

| Full-Scale Drift              | Internal Reference<br>External Reference |   |      | ±30<br>±5 |     | ppm/°C<br>ppm/°C   |

| Transition Noise              | SENSE = 1V                               |   |      | 0.08      |     | LSB <sub>RMS</sub> |

LINEAR

# **ANALOG INPUT** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . (Note 4)

| SYMBOL              | PARAMETER                                                                                 | CONDITIONS                                                 |   | MIN      | TYP        | MAX      | UNITS             |

|---------------------|-------------------------------------------------------------------------------------------|------------------------------------------------------------|---|----------|------------|----------|-------------------|

| V <sub>IN</sub>     | Analog Input Range (A <sub>IN</sub> <sup>+</sup> – A <sub>IN</sub> <sup>-</sup> )         | 2.7V < V <sub>DD</sub> < 3.4V (Note 7)                     | • | :        | ±0.5 to ±  | 1        | V                 |

| V <sub>IN,CM</sub>  | Analog Input Common Mode (A <sub>IN</sub> <sup>+</sup> + A <sub>IN</sub> <sup>-</sup> )/2 | Differential Input (Note 7)<br>Single Ended Input (Note 7) | • | 1<br>0.5 | 1.5<br>1.5 | 1.9<br>2 | V                 |

| I <sub>IN</sub>     | Analog Input Leakage Current                                                              | $0V < A_{IN}^+, A_{IN}^- < V_{DD}$                         | • | -1       |            | 1        | μА                |

| I <sub>SENSE</sub>  | SENSE Input Leakage                                                                       | OV < SENSE < 1V                                            | • | -3       |            | 3        | μА                |

| I <sub>MODE</sub>   | MODE Pin Leakage                                                                          |                                                            | • | -3       |            | 3        | μА                |

| t <sub>AP</sub>     | Sample-and-Hold Acquisition Delay Time                                                    |                                                            |   |          | 0          |          | ns                |

| t <sub>JITTER</sub> | Sample-and-Hold Acquisition Delay Time Jitter                                             |                                                            |   |          | 0.2        |          | ps <sub>RMS</sub> |

| CMRR                | Analog Input Common Mode Rejection Ratio                                                  |                                                            |   |          | 80         |          | dB                |

# **DYNAMIC ACCURACY** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . $A_{IN} = -1 dBFS$ . (Note 4)

| SYMBOL          | PARAMETER                             | CONDITIONS                                             |   | MIN | TYP  | MAX | UNITS |

|-----------------|---------------------------------------|--------------------------------------------------------|---|-----|------|-----|-------|

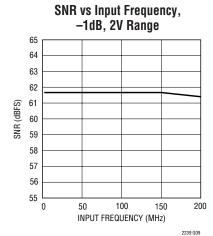

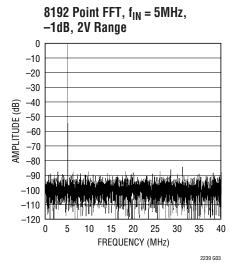

| SNR             | Signal-to-Noise Ratio                 | 5MHz Input                                             |   |     | 61.6 |     | dB    |

|                 |                                       | 40MHz Input                                            | • | 60  | 61.6 |     | dB    |

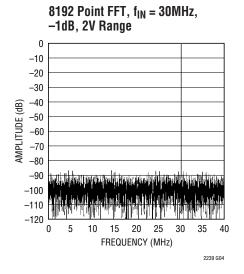

|                 |                                       | 70MHz Input                                            |   |     | 61.6 |     | dB    |

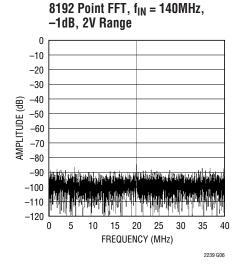

|                 |                                       | 140MHz Input                                           |   |     | 61.6 |     | dB    |

| SFDR            | Spurious Free Dynamic Range           | 5MHz Input                                             |   |     | 85   |     | dB    |

|                 | 2nd or 3rd Harmonic                   | 40MHz Input                                            | • | 69  | 85   |     | dB    |

|                 |                                       | 70MHz Input                                            |   |     | 85   |     | dB    |

|                 |                                       | 140MHz Input                                           |   |     | 80   |     | dB    |

| SFDR            | Spurious Free Dynamic Range           | 5MHz Input                                             |   |     | 85   |     | dB    |

|                 | 4th Harmonic or Higher                | 40MHz Input                                            | • | 75  | 85   |     | dB    |

|                 |                                       | 70MHz Input                                            |   |     | 85   |     | dB    |

|                 |                                       | 140MHz Input                                           |   |     | 85   |     | dB    |

| S/(N+D)         | Signal-to-Noise Plus Distortion Ratio | 5MHz Input                                             |   |     | 61.6 |     | dB    |

|                 |                                       | 40MHz Input                                            | • | 60  | 61.6 |     | dB    |

|                 |                                       | 70MHz Input                                            |   |     | 61.6 |     | dB    |

|                 |                                       | 140MHz Input                                           |   |     | 61.5 |     | dB    |

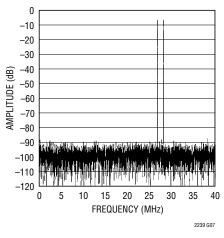

| I <sub>MD</sub> | Intermodulation Distortion            | f <sub>IN1</sub> = 28.2MHz, f <sub>IN2</sub> = 26.8MHz |   |     | 85   |     | dB    |

|                 | Full Power Bandwidth                  | Figure 8 Test Circuit                                  |   |     | 575  |     | MHz   |

## INTERNAL REFERENCE CHARACTERISTICS (Note 4)

| PARAMETER                         | CONDITIONS                    | MIN   | TYP   | MAX   | UNITS  |

|-----------------------------------|-------------------------------|-------|-------|-------|--------|

| V <sub>CM</sub> Output Voltage    | I <sub>OUT</sub> = 0          | 1.475 | 1.500 | 1.525 | V      |

| V <sub>CM</sub> Output Tempco     |                               |       | ±25   |       | ppm/°C |

| V <sub>CM</sub> Line Regulation   | 2.7V < V <sub>DD</sub> < 3.4V |       | 3     |       | mV/V   |

| V <sub>CM</sub> Output Resistance | -1mA < I <sub>OUT</sub> < 1mA |       | 4     |       | Ω      |

# **DIGITAL INPUTS AND DIGITAL OUTPUTS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . (Note 4)

| SYMBOL                         | PARAMETER                 | CONDITIONS                                      |   | MIN | TYP           | MAX | UNITS    |

|--------------------------------|---------------------------|-------------------------------------------------|---|-----|---------------|-----|----------|

| LOGIC INPUT                    | S (CLK, OE, SHDN)         | ·                                               |   |     |               |     |          |

| $\overline{V_{IH}}$            | High Level Input Voltage  | V <sub>DD</sub> = 3V                            | • | 2   |               |     | V        |

| $V_{IL}$                       | Low Level Input Voltage   | V <sub>DD</sub> = 3V                            | • |     |               | 0.8 | V        |

| I <sub>IN</sub>                | Input Current             | $V_{IN} = 0V \text{ to } V_{DD}$                | • | -10 |               | 10  | μА       |

| $\overline{C_{IN}}$            | Input Capacitance         | (Note 7)                                        |   |     | 3             |     | pF       |

| LOGIC OUTP                     | UTS                       |                                                 |   |     |               |     |          |

| 0V <sub>DD</sub> = 3V          |                           |                                                 |   |     |               |     |          |

| $\overline{C_{0Z}}$            | Hi-Z Output Capacitance   | OE = High (Note 7)                              |   |     | 3             |     | pF       |

| I <sub>SOURCE</sub>            | Output Source Current     | V <sub>OUT</sub> = 0V                           |   |     | 50            |     | mA       |

| I <sub>SINK</sub>              | Output Sink Current       | V <sub>OUT</sub> = 3V                           |   |     | 50            |     | mA       |

| V <sub>OH</sub>                | High Level Output Voltage | $I_0 = -10\mu A$ $I_0 = -200\mu A$              | • | 2.7 | 2.995<br>2.99 |     | V        |

| V <sub>OL</sub>                | Low Level Output Voltage  | I <sub>0</sub> = 10μA<br>I <sub>0</sub> = 1.6mA | • |     | 0.005<br>0.09 | 0.4 | V        |

| $OV_{DD} = 2.5V$               |                           |                                                 |   |     |               |     |          |

| $V_{OH}$                       | High Level Output Voltage | $I_0 = -200\mu A$                               |   |     | 2.49          |     | V        |

| $\overline{V_{0L}}$            | Low Level Output Voltage  | I <sub>0</sub> = 1.6mA                          |   |     | 0.09          |     | V        |

| <b>OV</b> <sub>DD</sub> = 1.8V |                           |                                                 |   | •   |               |     | <u> </u> |

| V <sub>OH</sub>                | High Level Output Voltage | $I_0 = -200 \mu A$                              |   |     | 1.79          |     | V        |

| $\overline{V_{0L}}$            | Low Level Output Voltage  | I <sub>0</sub> = 1.6mA                          |   |     | 0.09          |     | V        |

# **POWER REQUIREMENTS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . (Note 8)

| SYMBOL            | PARAMETER             | CONDITIONS                                   |   | MIN | TYP  | MAX | UNITS |

|-------------------|-----------------------|----------------------------------------------|---|-----|------|-----|-------|

| $V_{DD}$          | Analog Supply Voltage | (Note 9)                                     | • | 2.7 | 3    | 3.4 | V     |

| OV <sub>DD</sub>  | Output Supply Voltage | (Note 9)                                     | • | 0.5 | 3    | 3.6 | V     |

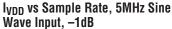

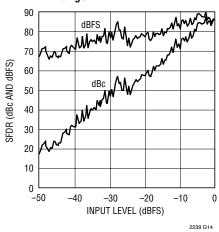

| IV <sub>DD</sub>  | Supply Current        |                                              | • |     | 70.3 | 82  | mA    |

| P <sub>DISS</sub> | Power Dissipation     |                                              | • |     | 211  | 246 | mW    |

| P <sub>SHDN</sub> | Shutdown Power        | SHDN = H, $\overline{\text{OE}}$ = H, No CLK |   |     | 2    |     | mW    |

| P <sub>NAP</sub>  | Nap Mode Power        | SHDN = H, $\overline{OE}$ = L, No CLK        |   |     | 15   |     | mW    |

# **TIMING CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25 \,^{\circ}\text{C}$ . (Note 4)

| SYMBOL              | PARAMETER                      | CONDITIONS                                                        |   | MIN      | TYP          | MAX        | UNITS    |

|---------------------|--------------------------------|-------------------------------------------------------------------|---|----------|--------------|------------|----------|

| f <sub>s</sub>      | Sampling Frequency             | (Note 9)                                                          | • | 1        |              | 80         | MHz      |

| t <sub>L</sub>      | CLK Low Time                   | Duty Cycle Stabilizer Off<br>Duty Cycle Stabilizer On<br>(Note 7) | • | 5.9<br>5 | 6.25<br>6.25 | 500<br>500 | ns<br>ns |

| t <sub>H</sub>      | CLK High Time                  | Duty Cycle Stabilizer Off<br>Duty Cycle Stabilizer On<br>(Note 7) | • | 5.9<br>5 | 6.25<br>6.25 | 500<br>500 | ns<br>ns |

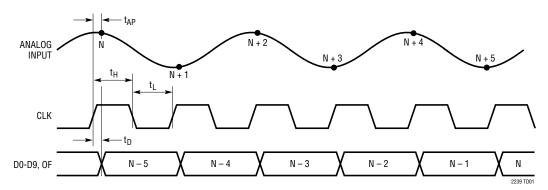

| t <sub>AP</sub>     | Sample-and-Hold Aperture Delay |                                                                   |   |          | 0            |            | ns       |

| $t_D$               | CLK to DATA Delay              | C <sub>L</sub> = 5pF (Note 7)                                     | • | 1.4      | 2.7          | 5.4        | ns       |

|                     | Data Access Time After 0E↓     | C <sub>L</sub> = 5pF (Note 7)                                     | • |          | 4.3          | 10         | ns       |

|                     | BUS Relinquish Time            | (Note 7)                                                          | • |          | 3.3          | 8.5        | ns       |

| Pipeline<br>Latency |                                |                                                                   |   |          | 5            |            | Cycles   |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** All voltage values are with respect to ground with GND and OGND wired together (unless otherwise noted).

**Note 3:** When these pin voltages are taken below GND or above  $V_{DD}$ , they will be clamped by internal diodes. This product can handle input currents of greater than 100mA below GND or above  $V_{DD}$  without latchup.

**Note 4:**  $V_{DD} = 3V$ ,  $f_{SAMPLE} = 80MHz$ , input range =  $2V_{P-P}$  with differential drive, unless otherwise noted.

**Note 5:** Integral nonlinearity is defined as the deviation of a code from a straight line passing through the actual endpoints of the transfer curve. The deviation is measured from the center of the quantization band.

**Note 6:** Offset error is the offset voltage measured from -0.5 LSB when the output code flickers between 00 0000 0000 and 11 1111 1111.

Note 7: Guaranteed by design, not subject to test.

Note 8:  $V_{DD}$  = 3V,  $f_{SAMPLE}$  = 80MHz, input range =  $1V_{P-P}$  with differential drive.

Note 9: Recommended operating conditions.

## TYPICAL PERFORMANCE CHARACTERISTICS

2239fa

## TYPICAL PERFORMANCE CHARACTERISTICS

8192 Point 2-Tone FFT,  $f_{\text{IN}} = 28.2 \text{MHz}$  and 26.8MHz, -1 dB, 2V Range

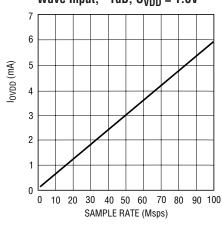

SFDR vs Input Frequency, -1dB, 2V Range

6

## TYPICAL PERFORMANCE CHARACTERISTICS

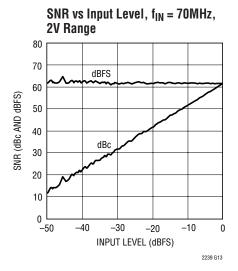

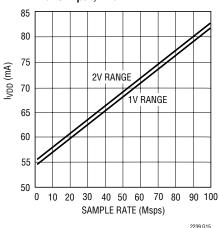

## SFDR vs Input Level, f<sub>IN</sub> = 70MHz, 2V Range

# $I_{OVDD}$ vs Sample Rate, 5MHz Sine Wave Input, –1dB, $O_{VDD}$ = 1.8V

2239 G16

## PIN FUNCTIONS

**A**<sub>IN</sub>+ (**Pin 1**): Positive Differential Analog Input.

**A**<sub>IN</sub>- (**Pin 2**): Negative Differential Analog Input.

**REFH (Pins 3, 4):** ADC High Reference. Short together and bypass to pins 5, 6 with a  $0.1\mu F$  ceramic chip capacitor as close to the pin as possible. Also bypass to pins 5, 6 with an additional  $2.2\mu F$  ceramic chip capacitor and to ground with a  $1\mu F$  ceramic chip capacitor.

**REFL (Pins 5, 6):** ADC Low Reference. Short together and bypass to pins 3, 4 with a  $0.1\mu F$  ceramic chip capacitor as close to the pin as possible. Also bypass to pins 3, 4 with an additional  $2.2\mu F$  ceramic chip capacitor and to ground with a  $1\mu F$  ceramic chip capacitor.

$V_{DD}$  (Pins 7, 32): 3V Supply. Bypass to GND with  $0.1\mu F$  ceramic chip capacitors.

GND (Pin 8): ADC Power Ground.

**CLK (Pin 9):** Clock Input. The input sample starts on the positive edge.

**SHDN (Pin 10):** Shutdown Mode Selection Pin. Connecting SHDN to GND and  $\overline{OE}$  to GND results in normal operation with the outputs enabled. Connecting SHDN to GND and  $\overline{OE}$  to  $V_{DD}$  results in normal operation with the outputs at high impedance. Connecting SHDN to  $V_{DD}$  and  $\overline{OE}$  to GND results in nap mode with the outputs at high impedance. Connecting SHDN to  $V_{DD}$  and  $\overline{OE}$  to  $V_{DD}$  results in sleep mode with the outputs at high impedance.

**OE** (**Pin 11**): Output Enable Pin. Refer to SHDN pin function.

NC (Pins 12 to 15): Do Not Connect These Pins.

**D0 – D9 (Pins 16, 17, 18, 19, 22, 23, 24, 25, 26, 27):** Digital Outputs. D9 is the MSB.

OGND (Pin 20): Output Driver Ground.

**OV**<sub>DD</sub> (**Pin 21**): Positive Supply for the Output Drivers. Bypass to ground with  $0.1\mu F$  ceramic chip capacitor.

**OF (Pin 28):** Over/Under Flow Output. High when an over or under flow has occurred.

**MODE (Pin 29):** Output Format and Clock Duty Cycle Stabilizer Selection Pin. Connecting MODE to GND selects offset binary output format and turns the clock duty cycle stabilizer off.  $1/3\ V_{DD}$  selects offset binary output format and turns the clock duty cycle stabilizer on.  $2/3\ V_{DD}$  selects 2's complement output format and turns the clock duty cycle stabilizer on.  $V_{DD}$  selects 2's complement output format and turns the clock duty cycle stabilizer off.

**SENSE (Pin 30):** Reference Programming Pin. Connecting SENSE to  $V_{CM}$  selects the internal reference and a  $\pm 0.5 V$  input range.  $V_{DD}$  selects the internal reference and a  $\pm 1 V$  input range. An external reference greater than 0.5V and less than 1V applied to SENSE selects an input range of  $\pm V_{SENSE}$ .  $\pm 1 V$  is the largest valid input range.

**V<sub>CM</sub> (Pin 31):** 1.5V Output and Input Common Mode Bias. Bypass to ground with 2.2µF ceramic chip capacitor.

**GND (Exposed Pad) (Pin 33):** ADC Power Ground. The exposed pad on the bottom of the package needs to be soldered to ground.

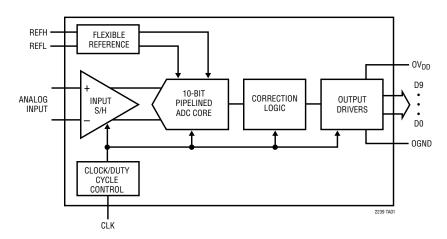

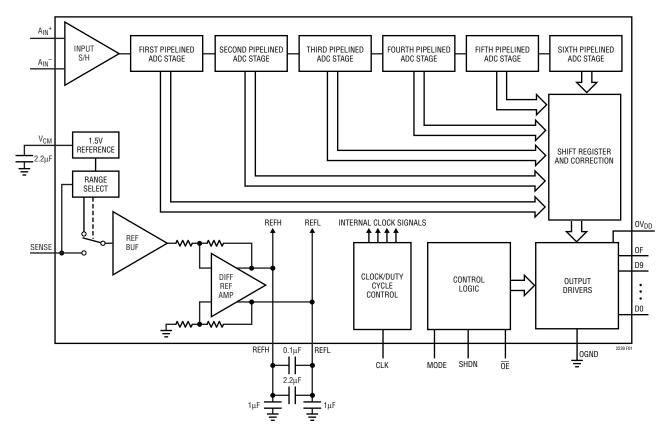

## **FUNCTIONAL BLOCK DIAGRAM**

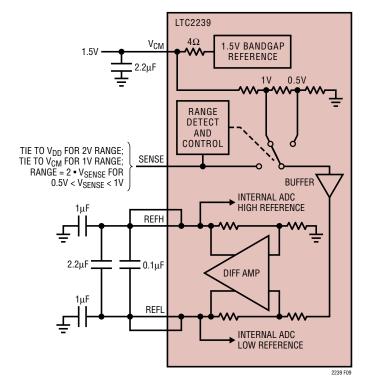

Figure 1. Functional Block Diagram

## TIMING DIAGRAM

#### **DYNAMIC PERFORMANCE**

#### Signal-to-Noise Plus Distortion Ratio

The signal-to-noise plus distortion ratio [S/(N+D)] is the ratio between the RMS amplitude of the fundamental input frequency and the RMS amplitude of all other frequency components at the ADC output. The output is band limited to frequencies above DC to below half the sampling frequency.

#### Signal-to-Noise Ratio

The signal-to-noise ratio (SNR) is the ratio between the RMS amplitude of the fundamental input frequency and the RMS amplitude of all other frequency components except the first five harmonics and DC.

#### **Total Harmonic Distortion**

Total harmonic distortion is the ratio of the RMS sum of all harmonics of the input signal to the fundamental itself. The out-of-band harmonics alias into the frequency band between DC and half the sampling frequency. THD is expressed as:

THD =

$$20 \text{Log} \left( \sqrt{(\text{V2}^2 + \text{V3}^2 + \text{V4}^2 + \dots \text{Vn}^2)} / \text{V1} \right)$$

where V1 is the RMS amplitude of the fundamental frequency and V2 through Vn are the amplitudes of the second through nth harmonics. The THD calculated in this data sheet uses all the harmonics up to the fifth.

#### Intermodulation Distortion

If the ADC input signal consists of more than one spectral component, the ADC transfer function nonlinearity can produce intermodulation distortion (IMD) in addition to THD. IMD is the change in one sinusoidal input caused by the presence of another sinusoidal input at a different frequency.

If two pure sine waves of frequencies fa and fb are applied to the ADC input, nonlinearities in the ADC transfer function can create distortion products at the sum and difference frequencies of mfa  $\pm$  nfb, where m and n = 0, 1, 2, 3, etc. The 3rd order intermodulation products are 2fa + fb, 2fb + fa, 2fa – fb and 2fb – fa. The intermodulation distortion is defined as the ratio of the RMS value of either input tone to the RMS value of the largest 3rd order intermodulation product.

#### Spurious Free Dynamic Range (SFDR)

Spurious free dynamic range is the peak harmonic or spurious noise that is the largest spectral component excluding the input signal and DC. This value is expressed in decibels relative to the RMS value of a full scale input signal.

#### **Input Bandwidth**

The input bandwidth is that input frequency at which the amplitude of the reconstructed fundamental is reduced by 3dB for a full scale input signal.

### **Aperture Delay Time**

The time from when CLK reaches mid-supply to the instant that the input signal is held by the sample and hold circuit.

#### **Aperture Delay Jitter**

The variation in the aperture delay time from conversion to conversion. This random variation will result in noise when sampling an AC input. The signal to noise ratio due to the litter alone will be:

$$SNR_{JITTER} = -20log (2\pi \bullet f_{IN} \bullet t_{JITTER})$$

#### **CONVERTER OPERATION**

As shown in Figure 1, the LTC2239 is a CMOS pipelined multistep converter. The converter has six pipelined ADC stages; a sampled analog input will result in a digitized value five cycles later (see the Timing Diagram section). For optimal AC performance the analog inputs should be driven differentially. For cost sensitive applications, the analog inputs can be driven single-ended with slightly worse harmonic distortion. The CLK input is single-ended. The LTC2239 has two phases of operation, determined by the state of the CLK input pin.

Each pipelined stage shown in Figure 1 contains an ADC, a reconstruction DAC and an interstage residue amplifier. In operation, the ADC quantizes the input to the stage and the quantized value is subtracted from the input by the DAC to produce a residue. The residue is amplified and output by the residue amplifier. Successive stages operate out of phase so that when the odd stages are outputting their residue, the even stages are acquiring that residue and vice versa.

When CLK is low, the analog input is sampled differentially directly onto the input sample-and-hold capacitors, inside the "Input S/H" shown in the block diagram. At the instant that CLK transitions from low to high, the sampled input is held. While CLK is high, the held input voltage is buffered by the S/H amplifier which drives the first pipelined ADC stage. The first stage acquires the output of the S/H during this high phase of CLK. When CLK goes back low, the first stage produces its residue which is acquired by the second stage. At the same time, the input S/H goes back to acquiring the analog input. When CLK goes back high, the second stage produces its residue which is acquired by the third stage. An identical process is repeated for the third, fourth and fifth stages, resulting in a fifth stage residue that is sent to the sixth stage ADC for final evaluation.

Each ADC stage following the first has additional range to accommodate flash and amplifier offset errors. Results from all of the ADC stages are digitally synchronized such that the results can be properly combined in the correction logic before being sent to the output buffer.

#### SAMPLE/HOLD OPERATION AND INPUT DRIVE

#### Sample/Hold Operation

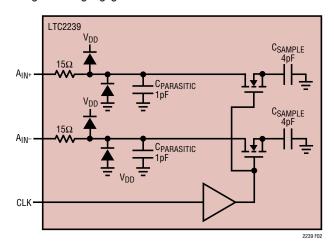

Figure 2 shows an equivalent circuit for the LTC2239 CMOS differential sample-and-hold. The analog inputs are connected to the sampling capacitors ( $C_{SAMPLE}$ ) through NMOS transistors. The capacitors shown attached to each input ( $C_{PARASITIC}$ ) are the summation of all other capacitance associated with each input.

During the sample phase when CLK is low, the transistors connect the analog inputs to the sampling capacitors and they charge to and track the differential input voltage. When CLK transitions from low to high, the sampled input voltage is held on the sampling capacitors. During the hold phase when CLK is high, the sampling capacitors are disconnected from the input and the held voltage is passed to the ADC core for processing. As CLK transitions from high to low, the inputs are reconnected to the sampling capacitors to acquire a new sample. Since the sampling capacitors still hold the previous sample, a charging glitch proportional to the change in voltage between samples will be seen at this time. If the change between the last sample and the new sample is small, the charging glitch seen at the input will be small. If the input change is large, such as the change seen with input frequencies near Nyquist, then a larger charging glitch will be seen.

Figure 2. Equivalent Input Circuit

LINEAR

#### Single-Ended Input

For cost sensitive applications, the analog inputs can be driven single-ended. With a single-ended input the harmonic distortion and INL will degrade, but the SNR and DNL will remain unchanged. For a single-ended input,  $A_{IN}^+$  should be driven with the input signal and  $A_{IN}^-$  should be connected to 1.5V or  $V_{CM}$ .

#### **Common Mode Bias**

For optimal performance the analog inputs should be driven differentially. Each input should swing  $\pm 0.5 V$  for the 2V range or  $\pm 0.25 V$  for the 1V range, around a common mode voltage of 1.5V. The  $V_{CM}$  output pin (Pin 31) may be used to provide the common mode bias level.  $V_{CM}$  can be tied directly to the center tap of a transformer to set the DC input level or as a reference level to an op amp differential driver circuit. The  $V_{CM}$  pin must be bypassed to ground close to the ADC with a  $2.2\mu F$  or greater capacitor.

#### **Input Drive Impedance**

As with all high performance, high speed ADCs, the dynamic performance of the LTC2239 can be influenced by the input drive circuitry, particularly the second and third harmonics. Source impedance and reactance can influence SFDR. At the falling edge of CLK, the sample-and-hold circuit will connect the 4pF sampling capacitor to the input pin and start the sampling period. The sampling period ends when CLK rises, holding the sampled input on the sampling capacitor. Ideally the input circuitry should be fast enough to fully charge the sampling capacitor during the sampling period 1/(2F<sub>ENCODE</sub>); however, this is not always possible and the incomplete settling may degrade the SFDR. The sampling glitch has been designed to be as linear as possible to minimize the effects of incomplete settling.

For the best performance, it is recommended to have a source impedance of  $100\Omega$  or less for each input. The source impedance should be matched for the differential inputs. Poor matching will result in higher even order harmonics, especially the second.

#### **Input Drive Circuits**

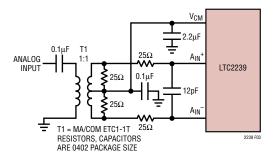

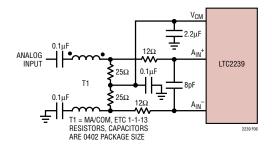

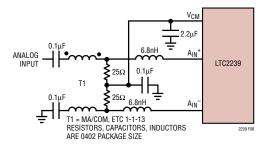

Figure 3 shows the LTC2239 being driven by an RF transformer with a center tapped secondary. The secondary center tap is DC biased with  $V_{CM}$ , setting the ADC input signal at its optimum DC level. Terminating on the transformer secondary is desirable, as this provides a common mode path for charging glitches caused by the sample and hold. Figure 3 shows a 1:1 turns ratio transformer. Other turns ratios can be used if the source impedance seen by the ADC does not exceed  $100\Omega$  for each ADC input. A disadvantage of using a transformer is the loss of low frequency response. Most small RF transformers have poor performance at frequencies below 1MHz.

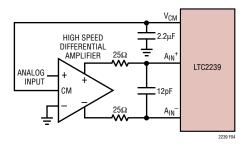

Figure 4 demonstrates the use of a differential amplifier to convert a single ended input signal into a differential input signal. The advantage of this method is that it provides low frequency input response; however, the limited gain bandwidth of most op amps will limit the SFDR at high input frequencies.

Figure 3. Single-Ended to Differential Conversion Using a Transformer

Figure 4. Differential Drive with an Amplifier

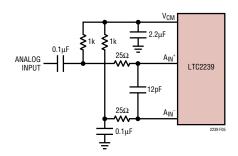

Figure 5 shows a single-ended input circuit. The impedance seen by the analog inputs should be matched. This circuit is not recommended if low distortion is required.

The  $25\Omega$  resistors and 12pF capacitor on the analog inputs serve two purposes: isolating the drive circuitry from the sample-and-hold charging glitches and limiting the wideband noise at the converter input.

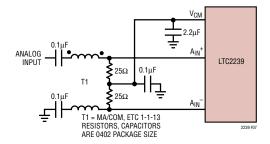

For input frequencies above 70MHz, the input circuits of Figure 6, 7 and 8 are recommended. The balun transformer gives better high frequency response than a flux coupled center tapped transformer. The coupling capacitors allow the analog inputs to be DC biased at 1.5V. In

Figure 5. Single-Ended Drive

Figure 6. Recommended Front End Circuit for Input Frequencies Between 70MHz and 170MHz

Figure 7. Recommended Front End Circuit for Input Frequencies Between 170MHz and 300MHz

Figure 8, the series inductors are impedance matching elements that maximize the ADC bandwidth.

#### **Reference Operation**

Figure 9 shows the LTC2239 reference circuitry consisting of a 1.5V bandgap reference, a difference amplifier and switching and control circuit. The internal voltage reference can be configured for two pin selectable input ranges of 2V ( $\pm 1V$  differential) or 1V ( $\pm 0.5V$  differential). Tying the SENSE pin to  $V_{DD}$  selects the 2V range; tying the SENSE pin to  $V_{CM}$  selects the 1V range.

Figure 8. Recommended Front End Circuit for Input Frequencies Above 300MHz

Figure 9. Equivalent Reference Circuit

2239fa

The 1.5V bandgap reference serves two functions: its output provides a DC bias point for setting the common mode voltage of any external input circuitry; additionally, the reference is used with a difference amplifier to generate the differential reference levels needed by the internal ADC circuitry. An external bypass capacitor is required for the 1.5V reference output,  $V_{CM}$ . This provides a high frequency low impedance path to ground for internal and external circuitry.

The difference amplifier generates the high and low reference for the ADC. High speed switching circuits are connected to these outputs and they must be externally bypassed. Each output has two pins. The multiple output pins are needed to reduce package inductance. Bypass capacitors must be connected as shown in Figure 9.

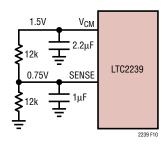

Other voltage ranges in-between the pin selectable ranges can be programmed with two external resistors as shown in Figure 10. An external reference can be used by applying its output directly or through a resistor divider to SENSE. It is not recommended to drive the SENSE pin with a logic device. The SENSE pin should be tied to the appropriate level as close to the converter as possible. If the SENSE pin is driven externally, it should be bypassed to ground as close to the device as possible with a  $1\mu F$  ceramic capacitor.

Figure 10. 1.5V Range ADC

#### **Input Range**

The input range can be set based on the application. The 2V input range will provide the best signal-to-noise performance while maintaining excellent SFDR. The 1V input range will have better SFDR performance, but the SNR will degrade by 0.7dB.

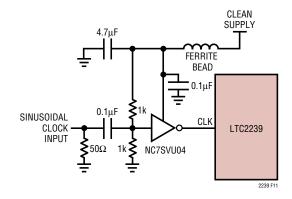

#### **Driving the Clock Input**

The CLK input can be driven directly with a CMOS or TTL level signal. A sinusoidal clock can also be used along with a low-jitter squaring circuit before the CLK pin (see Figure 11).

The noise performance of the LTC2239 can depend on the clock signal quality as much as on the analog input. Any noise present on the clock signal will result in additional aperture jitter that will be RMS summed with the inherent ADC aperture jitter.

In applications where jitter is critical, such as when digitizing high input frequencies, use as large an amplitude as possible. Also, if the ADC is clocked with a sinusoidal signal, filter the CLK signal to reduce wideband noise and distortion products generated by the source.

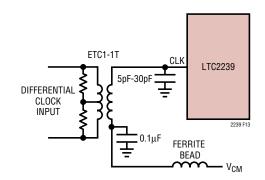

Figure 11. Sinusoidal Single-Ended CLK Drive

Figures 12 and 13 show alternatives for converting a differential clock to the single-ended CLK input. The use of a transformer provides no incremental contribution to phase noise. The LVDS or PECL to CMOS translators provide little degradation below 70MHz, but at 140MHz will degrade the SNR compared to the transformer solution. The nature of the received signals also has a large bearing on how much SNR degradation will be experienced. For high crest factor signals such as WCDMA or OFDM, where the nominal power level must be at least 6dB to 8dB below full scale, the use of these translators will have a lesser impact.

The transformer shown in the example may be terminated with the appropriate termination for the signaling in use. The use of a transformer with a 1:4 impedance ratio may be desirable in cases where lower voltage differential signals are considered. The center tap may be bypassed to ground through a capacitor close to the ADC if the differential signals originate on a different plane. The use of a capacitor at the input may result in peaking, and depending on transmission line length may require a  $10\Omega$  to  $20\Omega$  ohm series resistor to act as both a low pass filter for high frequency noise that may be induced into the clock line by neighboring digital signals, as well as a damping mechanism for reflections.

Figure 12. CLK Drive Using an LVDS or PECL to CMOS Converter

#### Maximum and Minimum Conversion Rates

The maximum conversion rate for the LTC2239 is 80Msps. For the ADC to operate properly, the CLK signal should have a 50% (±5%) duty cycle. Each half cycle must have at least 5.9ns for the ADC internal circuitry to have enough settling time for proper operation.

An optional clock duty cycle stabilizer circuit can be used if the input clock has a non 50% duty cycle. This circuit uses the rising edge of the CLK pin to sample the analog input. The falling edge of CLK is ignored and the internal falling edge is generated by a phase-locked loop. The input clock duty cycle can vary from 40% to 60% and the clock duty cycle stabilizer will maintain a constant 50% internal duty cycle. If the clock is turned off for a long period of time, the duty cycle stabilizer circuit will require a hundred clock cycles for the PLL to lock onto the input clock. To use the clock duty cycle stabilizer, the MODE pin should be connected to  $1/3V_{\rm DD}$  or  $2/3V_{\rm DD}$  using external resistors.

The lower limit of the LTC2239 sample rate is determined by droop of the sample-and-hold circuits. The pipelined architecture of this ADC relies on storing analog signals on small valued capacitors. Junction leakage will discharge the capacitors. The specified minimum operating frequency for the LTC2239 is 1Msps.

Figure 13. LVDS or PECL CLK Drive Using a Transformer

#### **DIGITAL OUTPUTS**

Table 1 shows the relationship between the analog input voltage, the digital data bits, and the overflow bit.

Table 1. Output Codes vs Input Voltage

| A <sub>IN</sub> + – A <sub>IN</sub> <sup>–</sup><br>(2V Range) | 0F | D9 – D0<br>(Offset Binary) | D9 – D0<br>(2's Complement) |

|----------------------------------------------------------------|----|----------------------------|-----------------------------|

| >+1.000000V                                                    | 1  | 11 1111 1111               | 01 1111 1111                |

| +0.998047V                                                     | 0  | 11 1111 1111               | 01 1111 1111                |

| +0.996094V                                                     | 0  | 11 1111 1110               | 01 1111 1110                |

| +0.001953V                                                     | 0  | 10 0000 0001               | 00 0000 0001                |

| 0.00000V                                                       | 0  | 10 0000 0000               | 00 0000 0000                |

| -0.001953V                                                     | 0  | 01 1111 1111               | 11 1111 1111                |

| -0.003906V                                                     | 0  | 01 1111 1110               | 11 1111 1110                |

| -0.998047V                                                     | 0  | 00 0000 0001               | 10 0000 0001                |

| -1.00000V                                                      | 0  | 00 0000 0000               | 10 0000 0000                |

| <-1.000000V                                                    | 1  | 00 0000 0000               | 10 0000 0000                |

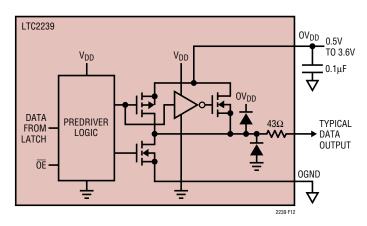

#### **Digital Output Buffers**

Figure 14 shows an equivalent circuit for a single output buffer. Each buffer is powered by  $\mathrm{OV}_{DD}$  and  $\mathrm{OGND}$ , isolated from the ADC power and ground. The additional N-channel transistor in the output driver allows operation down to low voltages. The internal resistor in series with the output makes the output appear as  $50\Omega$  to external circuitry and may eliminate the need for external damping resistors.

Figure 14. Digital Output Buffer

As with all high speed/high resolution converters, the digital output loading can affect the performance. The digital outputs of the LTC2239 should drive a minimal capacitive load to avoid possible interaction between the digital outputs and sensitive input circuitry. The output should be buffered with a device such as an ALVCH16373 CMOS latch. For full speed operation the capacitive load should be kept under 10pF.

Lower  $OV_{DD}$  voltages will also help reduce interference from the digital outputs.

#### **Data Format**

Using the MODE pin, the LTC2239 parallel digital output can be selected for offset binary or 2's complement format. Connecting MODE to GND or  $1/3V_{DD}$  selects offset binary output format. Connecting MODE to  $2/3V_{DD}$  or  $V_{DD}$  selects 2's complement output format. An external resistor divider can be used to set the  $1/3V_{DD}$  or  $2/3V_{DD}$  logic values. Table 2 shows the logic states for the MODE pin.

Table 2. MODE Pin Function

| MODE Pin           | Output Format  | Clock Duty<br>Cycle Stablizer |

|--------------------|----------------|-------------------------------|

| 0                  | Offset Binary  | Off                           |

| 1/3V <sub>DD</sub> | Offset Binary  | On                            |

| 2/3V <sub>DD</sub> | 2's Complement | On                            |

| $V_{DD}$           | 2's Complement | Off                           |

#### **Overflow Bit**

When OF outputs a logic high the converter is either overranged or underranged.

#### **Output Driver Power**

Separate output power and ground pins allow the output drivers to be isolated from the analog circuitry. The power supply for the digital output buffers,  $OV_{DD}$ , should be tied to the same power supply as for the logic being driven. For example if the converter is driving a DSP powered by a 1.8V supply, then  $OV_{DD}$  should be tied to that same 1.8V supply.

${

m OV_{DD}}$  can be powered with any voltage from 500mV up to 3.6V. OGND can be powered with any voltage from GND up to 1V and must be less than  ${

m OV_{DD}}$ . The logic outputs will swing between OGND and  ${

m OV_{DD}}$ .

#### **Output Enable**

The outputs may be disabled with the output enable pin,  $\overline{OE}$ .  $\overline{OE}$  high disables all data outputs including OF. The data access and bus relinquish times are too slow to allow the outputs to be enabled and disabled during full speed operation. The output Hi-Z state is intended for use during long periods of inactivity.

### **Sleep and Nap Modes**

The converter may be placed in shutdown or nap modes to conserve power. Connecting SHDN to GND results in normal operation. Connecting SHDN to  $V_{DD}$  and  $\overline{OE}$  to  $V_{DD}$  results in sleep mode, which powers down all circuitry including the reference and typically dissipates 1mW. When exiting sleep mode it will take milliseconds for the output data to become valid because the reference capacitors have to recharge and stabilize. Connecting SHDN to  $V_{DD}$  and  $\overline{OE}$  to GND results in nap mode, which typically dissipates 15mW. In nap mode, the on-chip reference circuit is kept on, so that recovery from nap mode is faster than that from sleep mode, typically taking 100 clock cycles. In both sleep and nap modes, all digital outputs are disabled and enter the Hi-Z state.

#### **Grounding and Bypassing**

The LTC2239 requires a printed circuit board with a clean, unbroken ground plane. A multilayer board with an internal ground plane is recommended. Layout for the printed circuit board should ensure that digital and analog signal lines are separated as much as possible. In particular, care should be taken not to run any digital track alongside an analog signal track or underneath the ADC.

High quality ceramic bypass capacitors should be used at the  $V_{DD},\, OV_{DD},\, V_{CM},\, REFH,\, and\, REFL\, pins.$  Bypass capacitors must be located as close to the pins as possible. Of particular importance is the  $0.1\mu F$  capacitor between REFH and REFL. This capacitor should be placed as close to the device as possible (1.5mm or less). A size 0402 ceramic capacitor is recommended. The large  $2.2\mu F$  capacitor between REFH and REFL can be somewhat further away. The traces connecting the pins and bypass capacitors must be kept short and should be made as wide as possible.

The LTC2239 differential inputs should run parallel and close to each other. The input traces should be as short as possible to minimize capacitance and to minimize noise pickup.

#### **Heat Transfer**

Most of the heat generated by the LTC2239 is transferred from the die through the bottom-side exposed pad and package leads onto the printed circuit board. For good electrical and thermal performance, the exposed pad should be soldered to a large grounded pad on the PC board. It is critical that all ground pins are connected to a ground plane of sufficient area.

#### **Clock Sources for Undersampling**

Undersampling raises the bar on the clock source and the higher the input frequency, the greater the sensitivity to clock jitter or phase noise. A clock source that degrades SNR of a full-scale signal by 1dB at 70MHz will degrade SNR by 3dB at 140MHz, and 4.5dB at 190MHz.

In cases where absolute clock frequency accuracy is relatively unimportant and only a single ADC is required, a 3V canned oscillator from vendors such as Saronix or Vectron can be placed close to the ADC and simply connected directly to the ADC. If there is any distance to the ADC, some source termination to reduce ringing that may occur even over a fraction of an inch is advisable. You must not allow the clock to overshoot the supplies or performance will suffer. Do not filter the clock signal with a narrow band filter unless you have a sinusoidal clock source, as the rise and fall time artifacts present in typical digital clock signals will be translated into phase noise.

The lowest phase noise oscillators have single-ended sinusoidal outputs, and for these devices the use of a filter close to the ADC may be beneficial. This filter should be close to the ADC to both reduce roundtrip reflection times, as well as reduce the susceptibility of the traces between the filter and the ADC. If you are sensitive to close-in phase noise, the power supply for oscillators and any buffers

must be very stable, or propagation delay variation with supply will translate into phase noise. Even though these clock sources may be regarded as digital devices, do not operate them on a digital supply. If your clock is also used to drive digital devices such as an FPGA, you should locate the oscillator, and any clock fan-out devices close to the ADC, and give the routing to the ADC precedence. The clock signals to the FPGA should have series termination at the source to prevent high frequency noise from the FPGA disturbing the substrate of the clock fan-out device. If you use an FPGA as a programmable divider, you must re-time the signal using the original oscillator, and the retiming flip-flop as well as the oscillator should be close to the ADC, and powered with a very quiet supply.

For cases where there are multiple ADCs, or where the clock source originates some distance away, differential clock distribution is advisable. This is advisable both from the perspective of EMI, but also to avoid receiving noise from digital sources both radiated, as well as propagated in the waveguides that exist between the layers of multilayer PCBs.

The differential pairs must be close together, and distanced from other signals. The differential pair should be guarded on both sides with copper distanced at least 3x the distance between the traces, and grounded with vias no more than 1/4 inch apart.

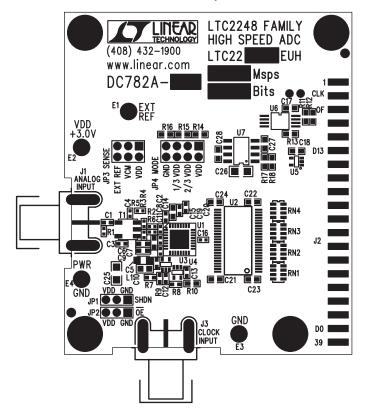

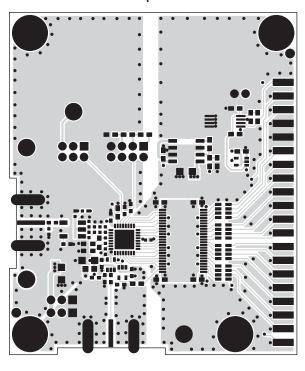

Silkscreen Top

Topside

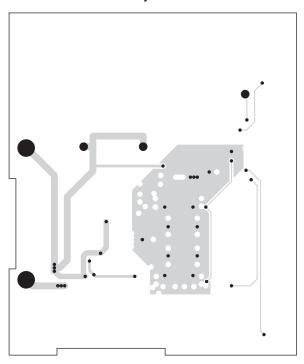

**Inner Layer 2 GND**

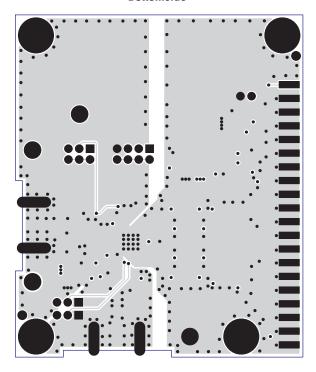

Inner Layer 3 Power

## Bottomside

#### Silkscreen Bottom

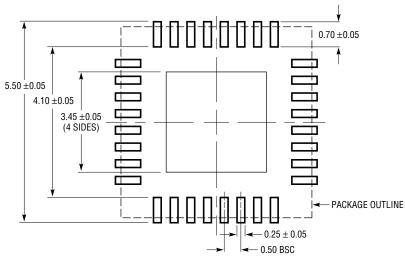

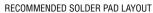

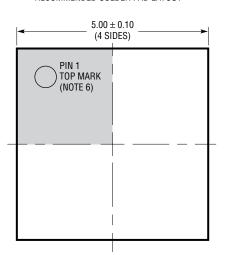

## PACKAGE DESCRIPTION

## $\begin{array}{c} \text{UH Package} \\ \text{32-Lead Plastic QFN (5mm} \times \text{5mm)} \end{array}$

(Reference LTC DWG # 05-08-1693)

#### NOTF.

- 1. DRAWING PROPOSED TO BE A JEDEC PACKAGE OUTLINE M0-220 VARIATION WHHD-(X) (TO BE APPROVED)

- 2. DRAWING NOT TO SCALE

- 3. ALL DIMENSIONS ARE IN MILLIMETERS

- 4. DIMENSIONS OF EXPOSED PAD ON BOTTOM OF PACKAGE DO NOT INCLUDE MOLD FLASH. MOLD FLASH, IF PRESENT, SHALL NOT EXCEED 0.20mm ON ANY SIDE

- 5. EXPOSED PAD SHALL BE SOLDER PLATED

- 6. SHADED AREA IS ONLY A REFERENCE FOR PIN 1 LOCATION ON THE TOP AND BOTTOM OF PACKAGE

## **RELATED PARTS**

| PART NUMBER | DESCRIPTION                                                                | COMMENTS                                                                                         |

|-------------|----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| LTC1748     | 14-Bit, 80Msps, 5V ADC                                                     | 76.3dB SNR, 90dB SFDR, 48-Pin TSSOP Package                                                      |

| TC1750      | 14-Bit, 80Msps, 5V Wideband ADC                                            | Up to 500MHz IF Undersampling, 90dB SFDR                                                         |

| LT1993-2    | High Speed Differential Op Amp                                             | 800MHz BW, 70dBc Distortion at 70MHz, 6dB Gain                                                   |

| _T1994      | Low Noise, Low Distortion Fully Differential Input/Output Amplifier/Driver | Low Distortion: -94dBc at 1MHz                                                                   |

| _TC2202     | 16-Bit, 10Msps, 3.3V ADC, Lowest Noise                                     | 150mW, 81.6dB SNR, 100dB SFDR, 48-Pin QFN                                                        |

| _TC2208     | 16-Bit, 130Msps, 3.3V ADC, LVDS Outputs                                    | 1250mW, 78dB SNR, 100dB SFDR, 64-Pin QFN                                                         |

| _TC2220-1   | 12-Bit, 185Msps, 3.3V ADC, LVDS Outputs                                    | 910mW, 67.7dB SNR, 80dB SFDR, 64-Pin QFN                                                         |

| _TC2224     | 12-Bit, 135Msps, 3.3V ADC, High IF Sampling                                | 630mW, 67.6dB SNR, 84dB SFDR, 48-Pin QFN                                                         |

| LTC2225     | 12-Bit, 10Msps, 3V ADC, Lowest Power                                       | 60mW, 71.3dB SNR, 90dB SFDR, 32-Pin QFN                                                          |

| LTC2226     | 12-Bit, 25Msps, 3V ADC, Lowest Power                                       | 75mW, 71.4dB SNR, 90dB SFDR, 32-Pin QFN                                                          |

| LTC2227     | 12-Bit, 40Msps, 3V ADC, Lowest Power                                       | 120mW, 71.4dB SNR, 90dB SFDR, 32-Pin QFN                                                         |

| LTC2228     | 12-Bit, 65Msps, 3V ADC, Lowest Power                                       | 205mW, 71.3dB SNR, 90dB SFDR, 32-Pin QFN                                                         |

| LTC2229     | 12-Bit, 80Msps, 3V ADC, Lowest Power                                       | 211mW, 70.6dB SNR, 90dB SFDR, 32-Pin QFN                                                         |

| LTC2236     | 10-Bit, 25Msps, 3V ADC, Lowest Power                                       | 75mW, 61.8dB SNR, 85dB SFDR, 32-Pin QFN                                                          |

| LTC2237     | 10-Bit, 40Msps, 3V ADC, Lowest Power                                       | 120mW, 61.8dB SNR, 85dB SFDR, 32-Pin QFN                                                         |

| LTC2238     | 10-Bit, 65Msps, 3V ADC, Lowest Power                                       | 205mW, 61.8dB SNR, 85dB SFDR, 32-Pin QFN                                                         |

| LTC2239     | 10-Bit, 80Msps, 3V ADC, Lowest Power                                       | 211mW, 61.6dB SNR, 85dB SFDR, 32-Pin QFN                                                         |

| LTC2245     | 14-Bit, 10Msps, 3V ADC, Lowest Power                                       | 60mW, 74.4dB SNR, 90dB SFDR, 32-Pin QFN                                                          |

| LTC2246     | 14-Bit, 25Msps, 3V ADC, Lowest Power                                       | 75mW, 74.5dB SNR, 90dB SFDR, 32-Pin QFN                                                          |

| LTC2247     | 14-Bit, 40Msps, 3V ADC, Lowest Power                                       | 120mW, 74.4dB SNR, 90dB SFDR, 32-Pin QFN                                                         |

| LTC2248     | 14-Bit, 65Msps, 3V ADC, Lowest Power                                       | 205mW, 74.3dB SNR, 90dB SFDR, 32-Pin QFN                                                         |

| LTC2249     | 14-Bit, 80Msps, 3V ADC, Lowest Power                                       | 222mW, 73dB SNR, 90dB SFDR, 32-Pin QFN                                                           |

| LTC2250     | 10-Bit, 105Msps, 3V ADC, Lowest Power                                      | 320mW, 61.6dB SNR, 85dB SFDR, 32-Pin QFN                                                         |

| LTC2251     | 10-Bit, 125Msps, 3V ADC, Lowest Power                                      | 395mW, 61.6dB SNR, 85dB SFDR, 32-Pin QFN                                                         |

| LTC2252     | 12-Bit, 105Msps, 3V ADC, Lowest Power                                      | 320mW, 70.2dB SNR, 88dB SFDR, 32-Pin QFN                                                         |

| LTC2253     | 12-Bit, 125Msps, 3V ADC, Lowest Power                                      | 395mW, 70.2dB SNR, 88dB SFDR, 32-Pin QFN                                                         |

| LTC2254     | 14-Bit, 105Msps, 3V ADC, Lowest Power                                      | 320mW, 72.4dB SNR, 88dB SFDR, 32-Pin QFN                                                         |

| LTC2255     | 14-Bit, 125Msps, 3V ADC, Lowest Power                                      | 395mW, 72.5dB SNR, 88dB SFDR, 32-Pin QFN                                                         |

| LTC2284     | 14-Bit, Dual, 105Msps, 3V ADC, Low Crosstalk                               | 540mW, 72.4dB SNR, 88dB SFDR, 64-Pin QFN                                                         |

| LT5512      | DC-3GHz High Signal Level Downconverting Mixer                             | DC to 3GHz, 21dBm IIP3, Integrated LO Buffer                                                     |

| LT5514      | Ultralow Distortion IF Amplifier/ADC Driver with Digitally Controlled Gain | 450MHz to 1dB BW, 47dB OIP3, Digital Gain Control 10.5dB to 33dB in 1.5dB/Step                   |

| LT5515      | 1.5GHz to 2.5GHz Direct Conversion Quadrature Demodulator                  | High IIP3: 20dBm at 1.9GHz,<br>Integrated LO Quadrature Generator                                |

| LT5516      | 800MHz to 1.5GHz Direct Conversion Quadrature Demodulator                  | High IIP3: 21.5dBm at 900MHz,<br>Integrated LO Quadrature Generator                              |

| LT5517      | 40MHz to 900MHz Direct Conversion Quadrature Demodulator                   | High IIP3: 21dBm at 800MHz,<br>Integrated LO Quadrature Generator                                |

| LT5522      | 600MHz to 2.7GHz High Linearity Downconverting Mixer                       | 4.5V to 5.25V Supply, 25dBm IIP3 at 900MHz, NF = 12.5dB, $50\Omega$ Single-Ended RF and LO Ports |