## Dual Micropower, 1.4V/µs Precision Rail-to-Rail Output Amplifier

## FEATURES

Excellent Slew Rate to Power Ratio

Slew Rate: 1.4V/μs

■ Maximum Supply Current: 20µA/Amplifier

■ Maximum Offset Voltage: 30µV

High Dynamic Input Impedance

■ Fast Recovery from Shutdown

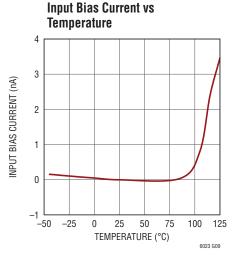

Maximum Input Bias Current: 3nA

No Output Phase Inversion

Gain Bandwidth Product: 40kHz

Wide Specified Supply Range: 3V to 30V

Operating Temperature Range: –40°C to 125°C

Rail-to-Rail Outputs

DFN and MS8 Packages

### **APPLICATIONS**

- Precision Signal Processing

- DAC Amplifier

- Multiplexed ADC Applications

- Low Power Portable Systems

- Low Power Wireless Sensor Networks

## DESCRIPTION

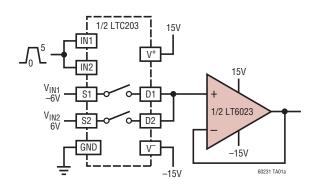

The LT®6023 is a low power, enhanced slew rate, precision operational amplifier. The proprietary circuit topology of this amplifier gives excellent slew rate at low quiescent power dissipation without compromising precision or settling time. In addition, proprietary input stage circuitry allows the input impedance to remain high during input voltage steps as large as 5V. The combination of precision specs along with fast settling makes this part ideal for MUX applications.

The low quiescent current of the LT6023 along with its ability to operate on supplies as low as 3V make it useful in portable systems. The LT6023-1 features a shutdown mode which reduces the typical supply current to 800nA.

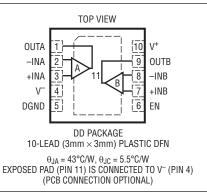

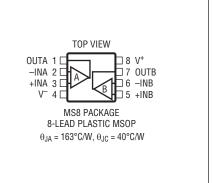

The LT6023 is available in the small 8-lead DFN and 8-lead MSOP packages. The LT6023-1 is available in a 10-lead DFN package.

## TYPICAL APPLICATION

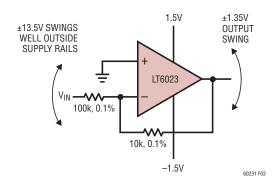

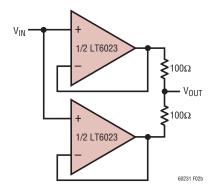

±13.6V Input Range MUX Buffer

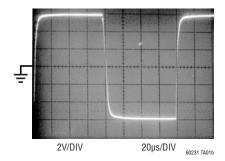

#### MUX Buffer Response, 12V Step

## **ABSOLUTE MAXIMUM RATINGS**

(Note 1)

| Total Supply Voltage (V+ to V-)              | 36V        |

|----------------------------------------------|------------|

| Differential Input Voltage (within Supplies) | 36V        |

| Input Voltage (DGND, EN, +IN, -IN)           |            |

| (Relative to V <sup>-</sup> )                | 36V        |

| Input Current (+IN, -IN, DGND, EN)           | ±10mA      |

| Output Short-Circuit Duration                | Indefinite |

| Operating and Specified Temperature  | Range          |

|--------------------------------------|----------------|

| I-Grade                              | 40°C to 85°C   |

| H-Grade                              | 40°C to 125°C  |

| Junction Temperature                 | 150°C          |

| Storage Temperature Range            | –65°C to 150°C |

| Lead Temperature (Soldering, 10 sec) | )300°C         |

## PIN CONFIGURATION

## ORDER INFORMATION

| LEAD FREE FINISH | TAPE AND REEL     | PART MARKING* | PACKAGE DESCRIPTION             | TEMPERATURE RANGE |

|------------------|-------------------|---------------|---------------------------------|-------------------|

| LT6023IDD#PBF    | LT6023IDD#TRPBF   | LGRS          | 8-Lead (3mm × 3mm) Plastic DFN  | -40°C to 85°C     |

| LT6023HDD#PBF    | LT6023HDD#TRPBF   | LGRS          | 8-Lead (3mm × 3mm) Plastic DFN  | -40°C to 125°C    |

| LT6023IDD-1#PBF  | LT6023IDD-1#TRPBF | LGRV          | 10-Lead (3mm × 3mm) Plastic DFN | -40°C to 85°C     |

| LT6023HDD-1#PBF  | LT6023HDD-1#TRPBF | LGRV          | 10-Lead (3mm × 3mm) Plastic DFN | -40°C to 125°C    |

| LT6023IMS8#PBF   | LT6023IMS8#TRPBF  | LTGRT         | 8-Lead Plastic MSOP             | -40°C to 85°C     |

| LT6023HMS8#PBF   | LT6023HMS8#TRPBF  | LTGRT         | 8-Lead Plastic MSOP             | -40°C to 125°C    |

Consult LTC Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container.

For more information on lead free part marking, go to: http://www.linear.com/leadfree/

For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the specified temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ ,  $V_S = \pm 15V$ ,  $V_{CM} = V_{OUT} = \text{Mid-Supply}$ ,  $V_{DGND} = 0V$ ,  $V_{EN} = 5V$ . DGND and EN specifications only apply to the LT6023-1.

| SYMBOL                               | PARAMETER                                             | CONDITIONS                                                                              |   | MIN                  | TYP        | MAX                  | UNITS             |

|--------------------------------------|-------------------------------------------------------|-----------------------------------------------------------------------------------------|---|----------------------|------------|----------------------|-------------------|

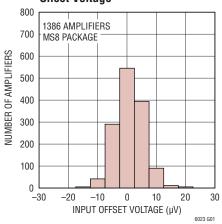

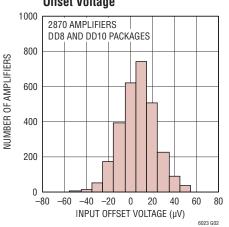

| V <sub>OS</sub>                      | Input Offset Voltage                                  | DD Packages                                                                             | • |                      | 20         | 70<br>160            | μV<br>μV          |

|                                      |                                                       | MS8 Package                                                                             | • |                      | 5          | 30<br>160            | μV<br>μV          |

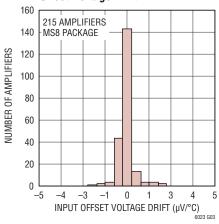

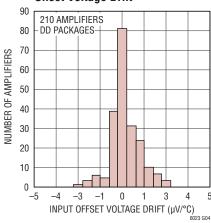

| ΔV <sub>OSI</sub>                    | Input Offset Voltage Drift (Note 2)                   | DD Packages                                                                             | • | -3.5                 | ±0.9       | 3.5                  | μV/°C             |

| ΔTemp                                |                                                       | MS8 Package                                                                             | • | -2.9                 | ±0.5       | 2.9                  | μV/°C             |

| $\frac{\Delta V_{OSI}}{\Delta Time}$ | Long Term Input Offset Voltage Stability              |                                                                                         |   |                      | ±0.2       |                      | μV/Mo             |

| I <sub>B</sub>                       | Input Bias Current                                    | T <sub>A</sub> = -40° to 85°C<br>T <sub>A</sub> = -40° to 125°C                         | • | -3<br>-3<br>-10      | ±0.1       | 3<br>3<br>10         | nA<br>nA<br>nA    |

| I <sub>0S</sub>                      | Input Offset Current                                  | T <sub>A</sub> = -40° to 85°C<br>T <sub>A</sub> = -40° to 125°C                         | • | -1<br>-1<br>-2       | ±0.1       | 1<br>1<br>2          | nA<br>nA<br>nA    |

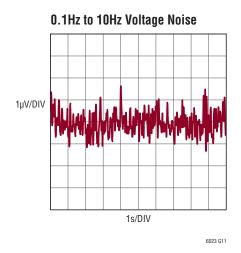

|                                      | Input Noise Voltage                                   | 0.1Hz to 10Hz                                                                           |   |                      | 3          |                      | μV <sub>P-P</sub> |

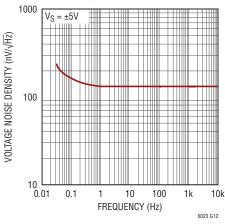

| e <sub>n</sub>                       | Input Noise Voltage Density                           | f = 1Hz<br>f = 1kHz                                                                     |   |                      | 132<br>132 |                      | nV/√Hz<br>nV/√Hz  |

| i <sub>n</sub>                       | Input Noise Current Density                           | f = 1kHz                                                                                |   |                      | 12.1       |                      | fA/√Hz            |

| C <sub>IN</sub>                      | Input Capacitance                                     | Common Mode<br>Differential Mode                                                        |   |                      | 1.5<br>2.5 |                      | pF<br>pF          |

| R <sub>IN</sub>                      | Input Resistance                                      | Common Mode<br>Differential Mode                                                        |   |                      | 140<br>330 |                      | GΩ<br>MΩ          |

| V <sub>ICM</sub>                     | Common Mode Input Range                               |                                                                                         | • | V <sup>-</sup> + 1.2 |            | V <sup>+</sup> – 1.4 | V                 |

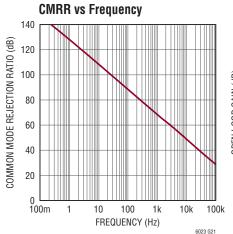

| CMRR                                 | Common Mode Rejection Ratio                           | $V_{CM} = -13.8V \text{ to } 13.6V$                                                     | • | 120<br>116           | 136        |                      | dB<br>dB          |

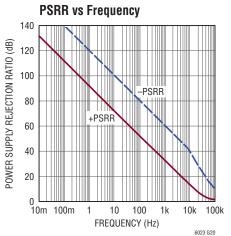

| PSRR                                 | Supply Rejection Ratio                                | V <sub>S</sub> = 3V to 30V                                                              | • | 120<br>110           | 140        |                      | dB<br>dB          |

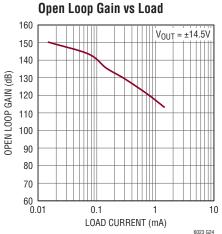

| A <sub>VOL</sub>                     | Large-Signal Voltage Gain                             | $R_L = 10k\Omega$ , $V_{OUT} = \pm 14V$                                                 | • | 110<br>100           | 114        |                      | dB<br>dB          |

|                                      |                                                       | $R_L = 100k\Omega, V_{OUT} = \pm 14.5V$                                                 | • | 126<br>116           | 134        |                      | dB<br>dB          |

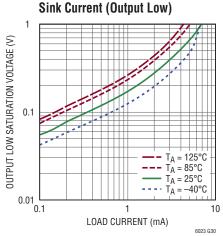

| V <sub>OL</sub>                      | Output Swing Low (V <sub>OUT</sub> – V <sup>-</sup> ) | $R_L = 10k\Omega$<br>$T_A = -40^{\circ}$ to 85°C<br>$T_A = -40^{\circ}$ to 125°C        | • |                      | 180        | 300<br>380<br>430    | mV<br>mV<br>mV    |

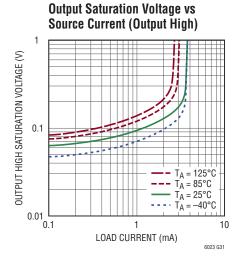

| V <sub>OH</sub>                      | Output Swing High (V* – V <sub>OUT</sub> )            | $R_L = 10k\Omega$<br>$T_A = -40^{\circ}$ to 85°C<br>$T_A = -40^{\circ}$ to 125°C        | • |                      | 115        | 140<br>165<br>190    | mV<br>mV<br>mV    |

| I <sub>SC</sub>                      | Short-Circuit Current                                 | $V_{OUT}$ = 0V, Sourcing<br>$T_A$ = -40° to 85°C<br>$T_A$ = -40° to 125°C               | • | 3<br>2.5<br>2        | 5.25       |                      | mA<br>mA<br>mA    |

|                                      |                                                       | $V_{OUT} = 0V$ , Sinking<br>$T_A = -40^{\circ}$ to 85°C<br>$T_A = -40^{\circ}$ to 125°C | • | 6.5<br>4.5<br>4      | 15         |                      | mA<br>mA<br>mA    |

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the specified temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ , $V_S = \pm 15V$ , $V_{CM} = V_{OUT} = \text{Mid-Supply}$ , $V_{DGND} = 0V$ , $V_{EN} = 5V$ . DGND and EN specifications only apply to the LT6023-1.

| SYMBOL               | PARAMETER                          | CONDITIONS                                                                                                                                   |   | MIN                | TYP                    | MAX                | UNITS                |

|----------------------|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|---|--------------------|------------------------|--------------------|----------------------|

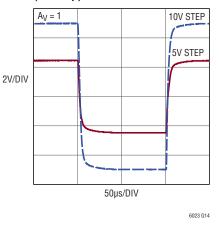

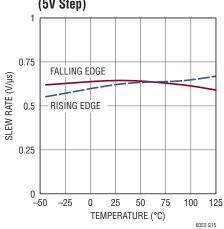

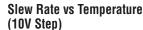

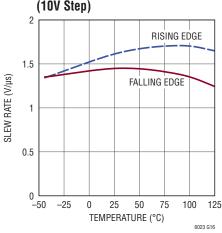

| SR                   | Slew Rate                          | $A_{VCL} = 1, 10V \text{ Step}$<br>$T_A = -40^{\circ} \text{ to } 85^{\circ}\text{C}$<br>$T_A = -40^{\circ} \text{ to } 125^{\circ}\text{C}$ | • | 0.85<br>0.7<br>0.6 | 1.4                    |                    | V/μs<br>V/μs<br>V/μs |

|                      |                                    | $A_{VCL} = 1, 5V \text{ Step}$<br>$T_A = -40^{\circ} \text{ to } 85^{\circ}\text{C}$<br>$T_A = -40^{\circ} \text{ to } 125^{\circ}\text{C}$  | • | 0.3<br>0.25<br>0.2 | 0.65                   |                    | V/μs<br>V/μs<br>V/μs |

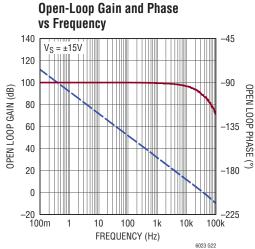

| GBW                  | Gain-Bandwidth Product             | f = 1kHz                                                                                                                                     | • | 29                 | 40                     |                    | kHz                  |

|                      | Minimum Supply Voltage             | Guaranteed by PSRR                                                                                                                           | • | 3                  |                        |                    | V                    |

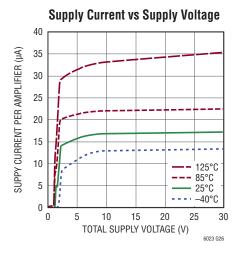

| I <sub>S</sub>       | Supply Current per Amplifier       | T <sub>A</sub> = -40° to 85°C<br>T <sub>A</sub> = -40° to 125°C                                                                              | • |                    | 18                     | 20<br>28<br>40     | μΑ<br>μΑ<br>μΑ       |

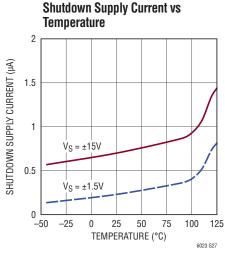

|                      | Supply Current in Shutdown         | V <sub>EN</sub> = 0.8V<br>T <sub>A</sub> = -40° to 85°C<br>T <sub>A</sub> = -40° to 125°C                                                    | • |                    | 0.8                    | 3<br>3.2<br>3.6    | μΑ<br>μΑ<br>μΑ       |

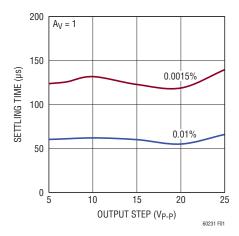

| t <sub>s</sub>       | Settling Time (A <sub>V</sub> = 1) | 0.1% 5V Output Step<br>0.01% 5V Output Step<br>0.0015% 5V Output Step<br>0.0015% 10V Output Step                                             |   |                    | 40<br>60<br>124<br>132 |                    | μs<br>μs<br>μs<br>μs |

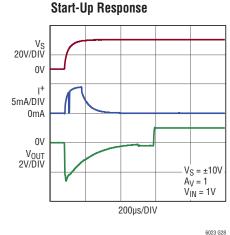

| t <sub>ON</sub>      | Enable Time                        | A <sub>V</sub> = 1                                                                                                                           |   |                    | 480                    |                    | μs                   |

| $V_{DGND}$           | DGND Pin Voltage Range             |                                                                                                                                              | • | V-                 |                        | V <sup>+</sup> – 3 | V                    |

| I <sub>DGND</sub>    | DGND Pin Current                   |                                                                                                                                              | • |                    |                        | -200               | nA                   |

| I <sub>EN</sub>      | EN Pin Current                     |                                                                                                                                              | • |                    |                        | -200               | nA                   |

| $\overline{V_{ENL}}$ | EN Pin Input Low Voltage           | Relative to DGND                                                                                                                             | • |                    |                        | 0.8                | V                    |

| V <sub>ENH</sub>     | EN Pin Input High Voltage          | Relative to DGND                                                                                                                             | • | 1.7                |                        |                    | V                    |

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the specified temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ ,  $V_S = 3V$ ,  $V_{CM} = V_{OUT} = Mid-Supply$ ,  $V_{DGND} = 0V$ ,  $V_{EN} = 3V$ . DGND and EN pin specifications only apply to the LT6023-1.

| SYMBOL                               | PARAMETER                                              | CONDITIONS                                                                                 | T | MIN                  | TYP        | MAX                  | UNITS             |

|--------------------------------------|--------------------------------------------------------|--------------------------------------------------------------------------------------------|---|----------------------|------------|----------------------|-------------------|

| V <sub>OS</sub>                      | Input Offset Voltage                                   | DD Packages                                                                                | • |                      | 20         | 100<br>190           | μV<br>μV          |

|                                      |                                                        | MS8 Package                                                                                | • |                      | 5          | 45<br>175            | μV<br>μV          |

| ΔV <sub>OSI</sub>                    | Input Offset Voltage Drift (Note 2)                    | DD Packages                                                                                | • | -3.5                 | ±0.9       | 3.5                  | μV/°C             |

| ΔTemp                                |                                                        | MS8 Package                                                                                | • | -2.9                 | ±0.5       | 2.9                  | μV/°C             |

| $\frac{\Delta V_{OSI}}{\Delta Time}$ | Long Term Input Offset Voltage Stability               |                                                                                            |   |                      | ±0.2       |                      | μV/Mo             |

| I <sub>B</sub>                       | Input Bias Current                                     |                                                                                            |   |                      | ±1         |                      | nA                |

| I <sub>OS</sub>                      | Input Offset Current                                   |                                                                                            |   |                      | ±0.1       |                      | nA                |

|                                      | Input Noise Voltage                                    | 0.1Hz to 10Hz                                                                              |   |                      | 3          |                      | μV <sub>P-P</sub> |

| en                                   | Input Noise Voltage Density                            | f = 1Hz<br>f = 1kHz                                                                        |   |                      | 132<br>132 |                      | nV/√Hz<br>nV/√Hz  |

| i <sub>n</sub>                       | Input Noise Current Density                            | f = 1kHz                                                                                   |   |                      | 12.1       |                      | fA/√Hz            |

| C <sub>IN</sub>                      | Input Capacitance                                      | Common Mode<br>Differential Mode                                                           |   |                      | 1.5<br>2.5 |                      | pF<br>pF          |

| R <sub>IN</sub>                      | Input Resistance                                       | Common Mode<br>Differential Mode                                                           |   |                      | 140<br>400 |                      | GΩ<br>MΩ          |

| V <sub>ICM</sub>                     | Common Mode Input Range                                |                                                                                            | • | V <sup>-</sup> + 1.2 |            | V <sup>+</sup> – 1.4 | V                 |

| CMRR                                 | Common Mode Rejection Ratio                            | V <sub>CM</sub> = 1.2V to 1.6V                                                             |   |                      | 125        |                      | dB                |

| PSRR                                 | Supply Rejection Ratio                                 | V <sub>S</sub> = 3V to 30V                                                                 | • | 120<br>110           | 140        |                      | dB<br>dB          |

| A <sub>VOL</sub>                     | Large-Signal Voltage Gain                              | $R_L = 10k\Omega$ , $V_{OUT} = 0.5V$ to 2.5V                                               | • | 98<br>95             | 108        |                      | dB<br>dB          |

|                                      |                                                        | $R_L = 100k\Omega$ , $V_{OUT} = 0.5V$ to 2.5V                                              |   |                      | 136        |                      | dB                |

| $V_{OL}$                             | Output Swing Low (V <sub>OUT</sub> – V <sup>-</sup> )  | $R_L = 10k\Omega$<br>$T_A = -40^{\circ}$ to 85°C<br>$T_A = -40^{\circ}$ to 125°C           | • |                      | 60         | 100<br>150<br>170    | mV<br>mV<br>mV    |

| V <sub>OH</sub>                      | Output Swing High (V <sup>+</sup> – V <sub>OUT</sub> ) | $R_L = 10k\Omega$<br>$T_A = -40^{\circ}$ to 85°C<br>$T_A = -40^{\circ}$ to 125°C           | • |                      | 60         | 80<br>90<br>100      | mV<br>mV<br>mV    |

| I <sub>SC</sub>                      | Short-Circuit Current                                  | $V_{OUT} = 1.5V$ , Sourcing<br>$T_A = -40^{\circ}$ to 85°C<br>$T_A = -40^{\circ}$ to 125°C | • | 2.5<br>2.25<br>2     | 3.5        |                      | mA<br>mA<br>mA    |

|                                      |                                                        | $V_{OUT} = 1.5V$ , Sinking<br>$T_A = -40^{\circ}$ to 85°C<br>$T_A = -40^{\circ}$ to 125°C  | • | 3.5<br>2<br>2        | 5          |                      | mA<br>mA<br>mA    |

| SR                                   | Slew Rate (Note 3)                                     | A <sub>VCL</sub> = -1, 2V Step                                                             |   |                      | 0.05       |                      | V/µs              |

| GBW                                  | Gain-Bandwidth Product                                 | f = 1kHz                                                                                   |   |                      | 40         |                      | kHz               |

|                                      | Minimum Supply Voltage                                 | Guaranteed by PSRR                                                                         | • | 3                    |            |                      | V                 |

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the specified temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ ,  $V_S = 3V$ ,  $V_{CM} = V_{OUT} = Mid-Supply$ ,  $V_{DGND} = 0V$ ,  $V_{EN} = 3V$ . DGND and EN pin specifications only apply to the LT6023-1.

| SYMBOL               | PARAMETER                           | CONDITIONS                                                                  |   | MIN            | TYP              | MAX                | UNITS          |

|----------------------|-------------------------------------|-----------------------------------------------------------------------------|---|----------------|------------------|--------------------|----------------|

| Is                   | Supply Current per Amplifier        | T <sub>A</sub> = -40° to 85°C<br>T <sub>A</sub> = -40° to 125°C             | • |                | 15               | 20<br>25<br>35     | μΑ<br>μΑ<br>μΑ |

|                      | Supply Current in Shutdown          | $V_{EN} = 0.8V$ $T_A = -40^{\circ}$ to 85°C $T_A = -40^{\circ}$ to 125°C    | • |                | 0.2              | 1.1<br>1.5<br>3    | μΑ<br>μΑ<br>μΑ |

| t <sub>s</sub>       | Settling Time (A <sub>V</sub> = −1) | 0.1% 2.4V Output Step<br>0.01% 2.4V Output Step<br>0.0015% 2.4V Output Step |   |                | 85<br>100<br>250 |                    | µs<br>µs<br>µs |

| $t_{ON}$             | Enable Time                         | A <sub>V</sub> = 1                                                          |   |                | 580              |                    | μs             |

| $V_{DGND}$           | DGND Pin Voltage Range              |                                                                             | • | V <sup>-</sup> |                  | V <sup>+</sup> – 3 | V              |

| I <sub>DGND</sub>    | DGND Pin Current                    |                                                                             |   |                | -75              |                    | nA             |

| I <sub>EN</sub>      | EN Pin Current                      |                                                                             |   |                | -75              |                    | nA             |

| $\overline{V_{ENL}}$ | EN Pin Input Low Voltage            | Relative to DGND                                                            | • |                |                  | 0.8                | V              |

| V <sub>ENH</sub>     | EN Pin Input High Voltage           | Relative to DGND                                                            | • | 1.7            |                  |                    | V              |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

Note 2: Guaranteed by design.

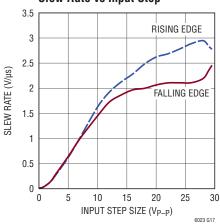

**Note 3:** The slew rate of the LT6023 increases with the size of the input step. At lower supplies, the input step size is limited by the input common mode range. This trend can be seen in the Typical Performance Characteristics.

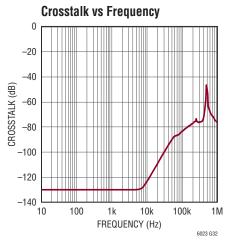

$T_A = 25$ °C,  $V_S = \pm 15$ V,  $R_L = 100$ k $\Omega$ , unless

otherwise specified.

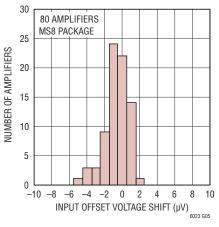

Typical Distribution of Input Offset Voltage

Typical Distribution of Input Offset Voltage

Typical Distribution of Input Offset Voltage Drift

Typical Distribution of Input Offset Voltage Drift

Offset Voltage Shift vs Lead Free IR Reflow

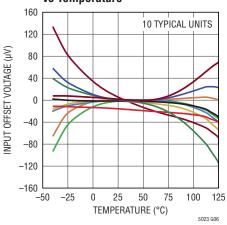

Typical Input Offset Voltage vs Temperature

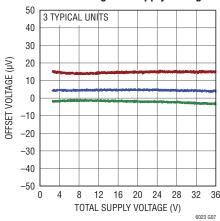

Offset Voltage vs Supply Voltage

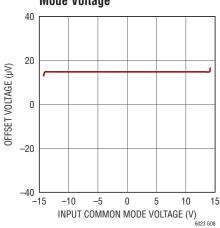

Offset Voltage vs Input Common Mode Voltage

$T_A=25^{\circ}C,~V_S=\pm15V,~R_L=100k\Omega,~unless$

otherwise specified.

Voltage Noise Density vs Frequency

Large-Signal Transient Response (5V Step)

Slew Rate vs Temperature (5V Step)

#### Slew Rate vs Input Step

60231fa

$T_A$  = 25°C,  $V_S$  = ±15V,  $R_L$  = 100k $\Omega$  unless

otherwise specified.

60231fa

$T_A = 25^{\circ}C$ ,  $V_S = \pm 15V$ ,  $R_L = 100k\Omega$  unless

otherwise specified.

**Output Saturation Voltage vs**

**Positive Output Overdrive**

60231fa

## PIN FUNCTIONS

**OUT:** Amplifier Output.

-IN: Inverting Input of the Amplifier.

+IN: Noninverting Input of the Amplifier.

**V**<sup>-</sup>: Negative Power Supply. A bypass capacitor should be used between supply pins and ground. Additional bypass capacitance may be used between the power supply pins.

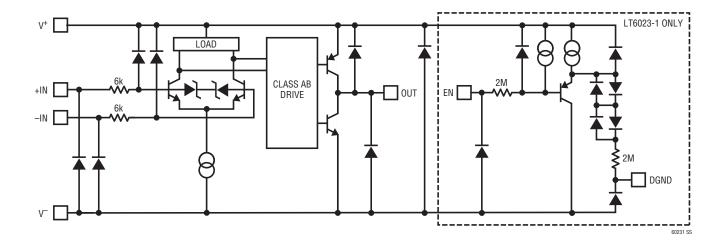

**DGND (LT6023-1 Only):** Reference for EN Pin. It is normally tied to ground. DGND must be in the range from  $V^-$  to  $V^+$  –3V. If grounded,  $V^+$  must be  $\geq$  3V. The EN pin threshold is specified with respect to the DGND pin. DGND cannot be floated.

**EN (LT6023-1 Only):** Enable Input. This pin must be connected high, normally to V<sup>+</sup>, for the amplifiers to be functional. EN is active high with the threshold approximately two diodes above DGND. EN cannot be floated. The shutdown threshold voltage is specified with respect to the voltage on the DGND pin.

**V**<sup>+</sup>: Positive Power Supply. A bypass capacitor should be used between supply pins and ground. Additional bypass capacitance may be used between the power supply pins.

### SIMPLIFIED SCHEMATIC

#### **Preserving Low Power Operation**

The proprietary circuitry used in the LT6023 provides an excellent combination of low power, low offset and enhanced slew rate. Normally an amplifier with higher supply current would be required to achieve this combination of slew rate and precision. Special care must be taken to ensure that the low power operation is preserved.

The choice of feedback resistor values impacts several op-amp parameters as noted in the feedback components section. It should also be noted that the output of the amplifier must drive this network. For example, in a gain of two with a total feedback resistance of  $10k\Omega$  and an output voltage of 14V, the amplifier's output will need to supply 1.4mA of current. This current will ultimately come from a supply.

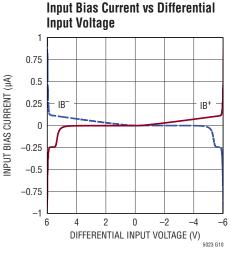

The supply current of the LT6023 increases with large differential input voltages. Normally, this does not impact the low power nature of the LT6023 because the amplifier is forcing the two inputs to be at the same potential. Conditions which cause differential input voltage to appear should be avoided in order to preserve the low power dissipation of the LT6023. This includes but is not limited to: operation as a comparator, excessive loading on the output and overdriving the input.

#### **Enhanced Slew Rate**

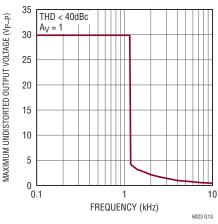

The LT6023 uses a proprietary input stage which provides an enhanced slew rate without sacrificing input precision specs such as input offset voltage, common mode rejection and noise. The unique input stage of the LT6023 allows the output to quickly slew to its final value when large signal input steps are applied. This enhanced slew characteristic allows the LT6023 to quickly settle the output to 0.0015% independent of input step size as shown in Figure 1. Typical micropower amplifiers cannot process large amplitude signals with this speed. As shown in the Typical Performance curves, when the LT6023 is configured in unity gain and a 10V step is applied to the input the output will slew at  $1.4V/\mu$ s. In this same configuration, a 5V input step will slew the output at  $0.65V/\mu$ s. Furthermore, a 0.7V input step

Figure 1. Settling Time Is Essentially Flat

will lower the slew rate to 0.02V/µs. Note that for these smaller inputs the LT6023 slew rate approaches the slew rate more common in traditional micropower amplifiers.

#### **Input Bias Current**

The design of the input stage of the LT6023 is more sophisticated than that shown in the Simplified Schematic. It uses both NPN and PNP input differential amplifiers to sense the input differential voltage. As a result the specified input bias current may flow in or out of the input pins.

## Multiplexer Applications/High Dynamic Input Impedance

The LT6023 has features which make it desirable for multiplexer applications, such as the application featured on the front page of this data sheet. When the channels of the multiplexer are cycled, the output of the multiplexer can produce large voltage transitions. Normally, bipolar amplifiers have back-to-back diodes between the inputs, which will turn on when the input transient voltage exceeds 0.7V, causing a large transient current to be conducted from the amplifier output stage back into the input driving circuitry. The driving circuitry then needs to absorb this current and settle before the amplifier can settle. The LT6023 uses 5.5V Zener diodes to protect its inputs which dramatically increases its input impedance with input steps as large as 5V.

LINEAR TECHNOLOGY

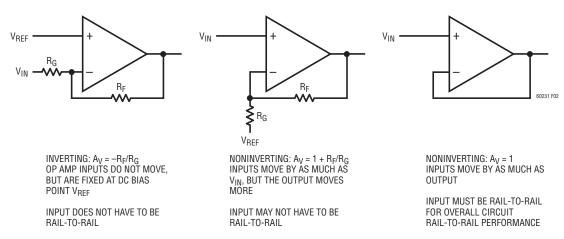

Figure 2. Some Op Amp Configurations Do Not Require Rail-to-Rail Inputs to Achieve Rail-to-Rail Outputs

## Achieving Rail-to-Rail Operation without Rail-to-Rail Inputs

The LT6023 output is able to swing close to each power supply rail, but the input stage is limited to operating between  $V^- + 1.2V$  and  $V^+ - 1.4V$ . For many inverting applications and noninverting gain applications, this is largely inconsequential. Figure 2 shows the basic op amp configurations, what happens to the op amp inputs and whether or not the op amp must have rail-to-rail inputs.

The circuit of Figure 3 shows an extreme example of the inverting case. The input voltage at the 100k resistor can swing ±13.5V and the LT6023 will output an inverted, divided-by-ten version of the input voltage. The output

Figure 3. Extreme Inverting Case: Circuit Operates Properly with Input Voltage Swing Well Outside Op Amp Supply Rails

accuracy is limited by the resistors shown to 0.2%. Output referred, this error becomes 2.7mV. The  $30\mu V$  input offset voltage contribution, plus the additional error due to input bias current times the ~10k effective source impedance, contribute only negligibly to error.

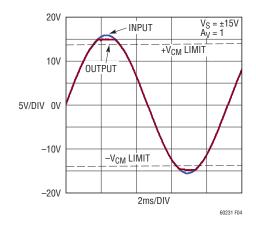

#### Phase Inversion

The LT6023 input stage is limited to operating between  $V^-+1.2V$  and  $V^+-1.4V$ . Exceeding this common mode range will cause the open loop gain to drop significantly. For a unity gain amplifier, the output roughly tracks the input well beyond the specified input voltage range as shown in Figure 4.

Figure 4. No Phase Inversion

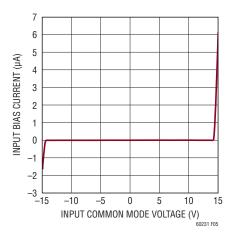

Figure 5. Increased Ib Beyond VICM

However the open loop gain is significantly reduced. While the output roughly tracks the input, the reduction in open loop gain degrades the accuracy of the LT6023 in this region. Exceeding the input common mode range also causes a significant increase in input bias current as shown in Figure 5. The output of the LT6023 is guaranteed over the specified temperature range not to phase invert as long as the input voltage does not exceed the supply voltage.

#### **Preserving Input Precision**

Preserving the input accuracy of the LT6023 requires that the application circuit and PC board layout do not introduce errors comparable to or greater than the offset of the amplifiers. Temperature differentials across the input connections can generate thermocouple voltages of tens of microvolts so the connections of the input leads should be short, close together and away from heat dissipating components. Air currents across the board can also generate temperature differentials.

As is the case with all amplifiers, a change in load current changes the finite open loop gain. Increased load current reduces the open loop gain as seen in the Typical Performance Characteristics section. This results in a

change in input offset voltage. Under large signal conditions with load currents of  $\pm 1$  mA the effective change in input error is just tens of microvolts. In precision applications it is important to consider amplifier loading when selecting feedback resistor values as well as the loads on the device.

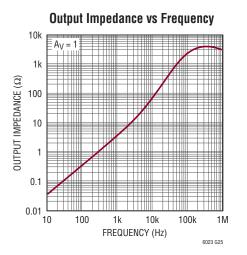

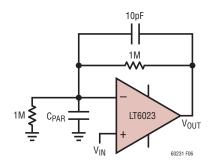

#### **Feedback Components**

Care must be taken to ensure that the phase shift formed by the feedback resistors and the parasitic capacitance at the inverting input does not degrade stability. For example, in a gain of +2 configuration, with 1M feedback resistors and a poorly designed circuit board layout with parasitic capacitance of 10pF (amplifier + PC board) at the amplifier's inverting input will cause the amplifier to have poor phase margin due to a pole formed at 32kHz. An additional capacitor of 10pF across the feedback resistor as shown in Figure 6 will eliminate any ringing or oscillation.

Figure 6. Stability with Parasitic Input Capacitance

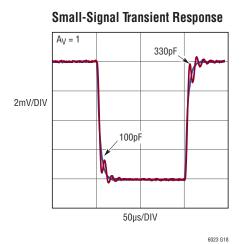

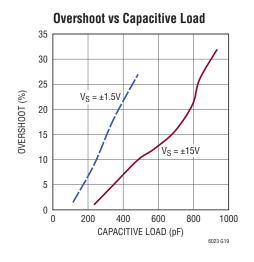

#### **Capacitive Loads**

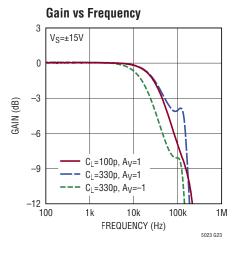

The LT6023 can drive capacitive loads up to 100pF in unity gain. The capacitive load driving capability increases as the amplifier is used in higher gain configurations. A small series resistance between the output and the load will further increase the amount of capacitance that the amplifier can drive.

LINEAR

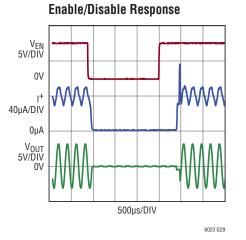

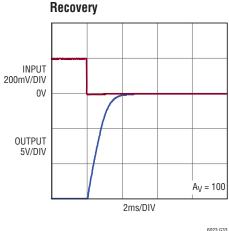

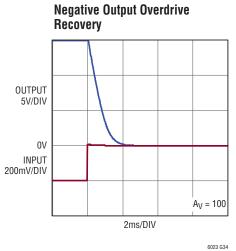

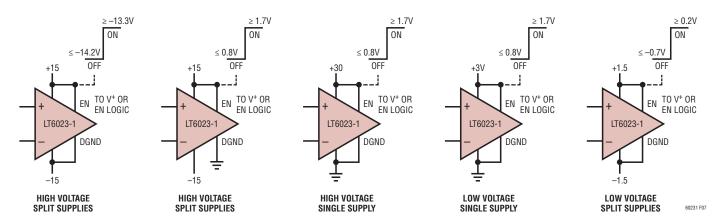

#### Shutdown Operation (LT6023-1)

The LT6023-1 shutdown function has been designed to be easily controlled from single supply logic or microcontollers. To enable the LT6023-1 when  $V_{DGND} = 0V$  the enable pin must be driven above 1.7V. Conversely, to enter the low power shutdown mode the enable pin must be driven below 0.8V. In a  $\pm 15V$  dual supply application where  $V_{DGND} = -15V$ , the enable pin must be driven above  $\sim -13.3V$  to enable the LT6023-1. If the enable pin is driven below -14.2V the LT6023-1 enters the low power shutdown mode. Note that to enable the LT6023-1 the enable pin voltage can range from -13.3V to 15V whereas

to disable the LT6023-1 the enable pin can range from -15V to -14.2V. Figure 7 shows examples of enable pin control. While in shutdown, the outputs of the LT6023-1 are high impedance.

The LT6023-1 is typically capable of coming out of shutdown within 480 $\mu$ s. This is useful in power sensitive applications where duty cycled operation is employed such as wireless mesh networks. In these applications the system is in low power mode the majority of the time, but then needs to wake up quickly and settle for an acquisition before being powered back down to save power.

Figure 7. LT6023-1 Enable Pin Control Examples

## TYPICAL APPLICATIONS

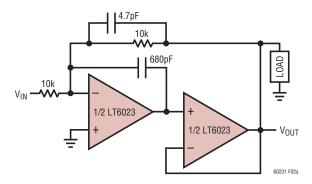

High Open-Loop Gain Composite Amplifier

Parallel Amplifiers Achieves 93nV/√Hz Noise, Doubles Output Drive and Lowers Offset

## TYPICAL APPLICATIONS

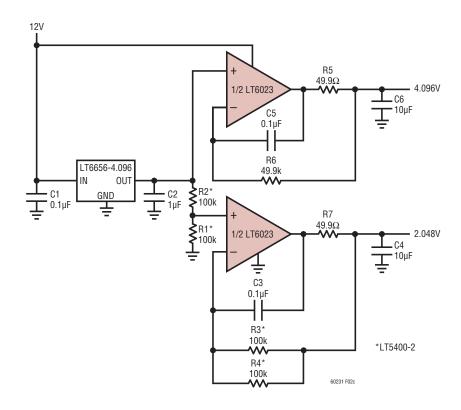

#### Micropower Reference Divider/Buffer

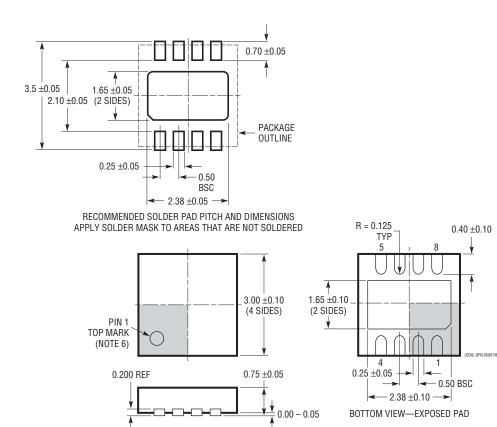

## PACKAGE DESCRIPTION

Please refer to http://www.linear.com/designtools/packaging/ for the most recent package drawings.

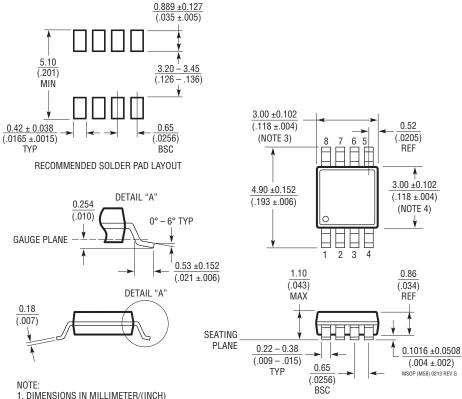

## $\begin{array}{c} \text{DD Package} \\ \text{8-Lead Plastic DFN (3mm} \times \text{3mm)} \end{array}$

(Reference LTC DWG # 05-08-1698 Rev C)

- NOTE:

- 1. DRAWING TO BE MADE A JEDEC PACKAGE OUTLINE MO-229 VARIATION OF (WEED-1)

- 2. DRAWING NOT TO SCALE

- 3. ALL DIMENSIONS ARE IN MILLIMETERS

- 4. DIMENSIONS OF EXPOSED PAD ON BOTTOM OF PACKAGE DO NOT INCLUDE MOLD FLASH. MOLD FLASH, IF PRESENT, SHALL NOT EXCEED 0.15mm ON ANY SIDE

- 5. EXPOSED PAD SHALL BE SOLDER PLATED

- 6. SHADED AREA IS ONLY A REFERENCE FOR PIN 1 LOCATION ON TOP AND BOTTOM OF PACKAGE

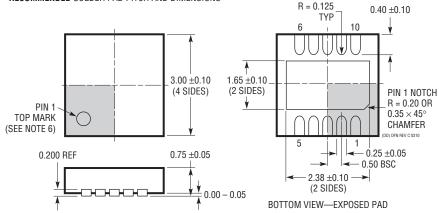

## PACKAGE DESCRIPTION

Please refer to http://www.linear.com/designtools/packaging/ for the most recent package drawings.

## DD Package 10-Lead Plastic DFN (3mm $\times$ 3mm) (Reference LTC DWG # 05-08-1699 Rev C)

(2 SIDES)

RECOMMENDED SOLDER PAD PITCH AND DIMENSIONS

2.38 ±0.05 -

BSC

#### NOTE:

- 1. DRAWING TO BE MADE A JEDEC PACKAGE OUTLINE M0-229 VARIATION OF (WEED-2). CHECK THE LTC WEBSITE DATA SHEET FOR CURRENT STATUS OF VARIATION ASSIGNMENT

- 2. DRAWING NOT TO SCALE

- 3. ALL DIMENSIONS ARE IN MILLIMETERS

- 4. DIMENSIONS OF EXPOSED PAD ON BOTTOM OF PACKAGE DO NOT INCLUDE MOLD FLASH. MOLD FLASH, IF PRESENT, SHALL NOT EXCEED 0.15mm ON ANY SIDE

- 5. EXPOSED PAD SHALL BE SOLDER PLATED

- 6. SHADED AREA IS ONLY A REFERENCE FOR PIN 1 LOCATION ON THE TOP AND BOTTOM OF PACKAGE

## PACKAGE DESCRIPTION

Please refer to http://www.linear.com/designtools/packaging/ for the most recent package drawings.

#### **MS8 Package** 8-Lead Plastic MSOP

(Reference LTC DWG # 05-08-1660 Rev G)

- 1. DIMENSIONS IN MILLIMETER/(INCH)

- 2. DRAWING NOT TO SCALE

- 3. DIMENSION DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS. MOLD FLASH, PROTRUSIONS OR GATE BURRS SHALL NOT EXCEED 0.152mm (.006") PER SIDE

- 4. DIMENSION DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS. INTERLEAD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.152mm (.006") PER SIDE

- 5. LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.102mm (.004") MAX

## **REVISION HISTORY**

| REV | DATE  | DESCRIPTION                                                          | PAGE NUMBER |

|-----|-------|----------------------------------------------------------------------|-------------|

| Α   | 04/15 | Updated typical slew rate to be consistent throughout the data sheet | 1, 4        |

|     |       | Corrected negative supply voltage on front page circuit              | 1           |

|     |       | Corrected Input Bias Current vs. Differential Input Voltage graph    | 8           |

## TYPICAL APPLICATION

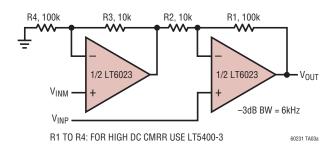

#### **Gain of 11 Instrumentation Amplifier**

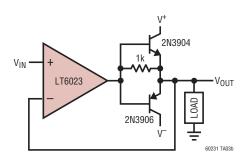

#### **Improved Load Drive Capability**

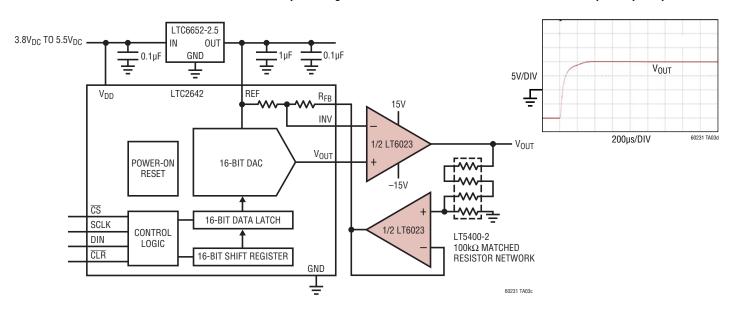

#### 16-Bit DAC with ±10V Output Swing

#### 20V Output Step Response

## **RELATED PARTS**

| PART NUMBER | DESCRIPTION                                       | COMMENTS                                                                                             |

|-------------|---------------------------------------------------|------------------------------------------------------------------------------------------------------|

| LT6004      | 2kHz, 1µA RRIO Op Amp                             | $V_{OS}$ : 500μV, GBW: 2kHz, SR: 0.8V/ms, $e_n$ : 325nV/ $\sqrt{Hz}$ , $I_s$ : 1μA                   |

| LT1490A     | 200kHz, 50μA RRIO Op Amp                          | V <sub>OS</sub> : 500μV, GBW: 200kHz, SR: 0.06V/μs, e <sub>n</sub> : 50nV/√Hz, I <sub>s</sub> : 50μA |

| LTC6256     | 6.5MHz, 65µA RRIO Op Amp                          | V <sub>OS</sub> : 350µV, GBW: 6.5MHz, SR: 1.8V/µs, e <sub>n</sub> : 20nV/√Hz, I <sub>s</sub> : 65µA  |

| LT6020      | 400kHz, 100μA, 5V/μs Op Amp                       | V <sub>OS</sub> : 30μV, GBW: 400kHz, SR: 5V/μs, e <sub>n</sub> : 46nV/√Hz, I <sub>s</sub> : 100μA    |

| LTC2055     | 500kHz, 150μA Zero-Drift Op Amp                   | V <sub>OS</sub> : 3μV, GBW: 500kHz, SR: 0.5V/μs, I <sub>s</sub> : 150μA                              |

| LT1783      | 1.2MHz, 230µA Over-The-Top RRIO Op Amp            | V <sub>OS</sub> : 600μV, GBW: 1.2MHz, SR: 0.4V/μs, e <sub>n</sub> : 20nV/√Hz, I <sub>s</sub> : 230μA |

| LT1352      | 3MHz. 200V/μs Op Amp                              | V <sub>OS</sub> : 600μV, GBW: 3MHz, SR: 200V/μs, e <sub>n</sub> : 14nV/√Hz, I <sub>s</sub> : 330μA   |

| LT1492      | 5MHz, 3V/μs Op Amp                                | V <sub>OS</sub> : 180μV, GBW: 5MHz, SR: 3V/μs, e <sub>n</sub> : 16.5nV/√Hz, I <sub>s</sub> : 550μA   |

| LTC5800     | SmartMesh® Wireless Sensor Network I <sub>C</sub> | Wireless Mesh Networks                                                                               |

| LT5400      | Quad Matched Resistor Network                     | 0.01% Matching                                                                                       |

LT 0415 REV A • PRINTED IN USA

TECHNOLOGY

© LINEAR TECHNOLOGY CORPORATION 2015