September 1999

# **LP339**

# **Ultra-Low Power Quad Comparator**

# **General Description**

The LP339 consists of four independent voltage comparators designed specifically to operate from a single power supply and draw typically 60  $\mu\text{A}$  of power supply drain current over a wide range of power supply voltages. Operation from split supplies is also possible and the ultra-low power supply drain current is independent of the power supply voltage. These comparators also feature a common-mode range which includes ground, even when operated from a single supply.

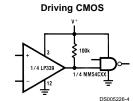

Applications include limit comparators, simple analog-to-digital converters, pulse, square and time delay generators; VCO's; multivibrators; high voltage logic gates. The LP339 was specifically designed to interface with the CMOS logic family. The ultra-low supply current makes the LP339 valuable in battery powered applications.

- Single supply operation

- Sensing at ground

- Compatible with CMOS logic family

- Pin-out identical to LM339

### **Features**

- Ultra-low power supply current drain (60 µA) independent of the supply voltage (75 µW/comparator at +5 V<sub>DC</sub>)

- Low input biasing current: 3 nA

- Low input offset current: ±0.5 nA

- Low input offset voltage: ±2 mV

- Input common-mode voltage includes ground

- Output voltage compatible with MOS and CMOS logic

- High output sink current capability (30 mA at V<sub>O</sub>=2 V<sub>DC</sub>)

- Supply Input protected against reverse voltages

# Advantages

Ultra-low power supply drain suitable for battery applications

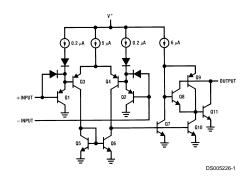

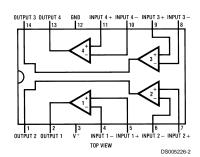

# **Schematic and Connection Diagrams**

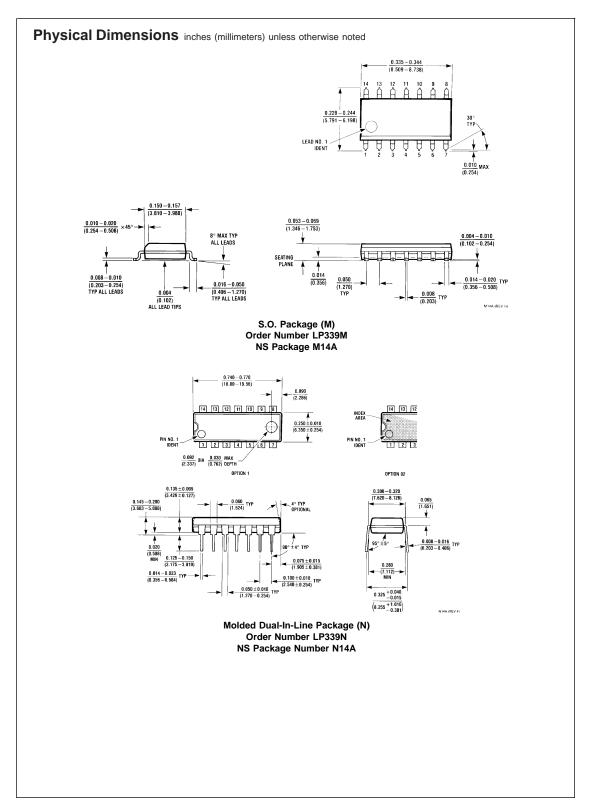

Order Number LP339M for S.O. Package See NS Package Number M14A Order Number LP339N for Dual-In-Line Package See NS Package Number N14A

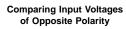

# Typical Applications (V+= 5.0 V<sub>DC</sub>)

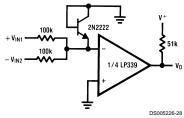

# Basic Comparator

### **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

$\begin{array}{lll} \text{Supply Voltage} & 36 \ \text{V}_{\text{DC}} \ \text{or} \ \pm 18 \ \text{V}_{\text{DC}} \\ \text{Differential Input Voltage} & \pm 36 \ \text{V}_{\text{DC}} \\ \text{Input Voltage} & -0.3 \ \text{V}_{\text{DC}} \ \text{to} \ 36 \ \text{V}_{\text{DC}} \\ \end{array}$

Power Dissipation (Note 2)

Molded DIP 570 mW

Output Short Circuit to GND (Note 3) Continuous

Input Current  $V_{IN}$ <-0.3  $V_{DC}$  (Note 4) 50 mA

Operating Temperature Range  $0^{\circ}\text{C}$  to  $+70^{\circ}\text{C}$  Storage Temperature Range  $-65^{\circ}$  to  $+150^{\circ}\text{C}$

Soldering Information:

Dual-In-Line Package (10 sec.) +260°C

S.O. Package:

Vapor Phase (60 sec.) +215°C Infrared (15 sec.) +220°C

See AN-450 "Surface Mounting Methods and Their Effect on Product Reliability" for other methods of soldering surface mount devices.

### **Electrical Characteristics**

(V+=5 V<sub>DC</sub>) (Note 5)

| Parameter                  | Conditions                                                                              | Min  | Тур  | Max    | Units            |

|----------------------------|-----------------------------------------------------------------------------------------|------|------|--------|------------------|

| Input Offset Voltage       | T <sub>A</sub> =25°C (Note 10)                                                          |      | ±2   | ±5     | mV <sub>DC</sub> |

| Input Bias Current         | I <sub>IN</sub> (+) or I <sub>IN</sub> (-) with the                                     |      | 2.5  | 25     | nA <sub>DC</sub> |

|                            | Output in the Linear Range, T <sub>A</sub> =25°C (Note 6)                               |      |      |        |                  |

| Input Offset Current       | $I_{IN}(+)-I_{IN}(-), T_A=25^{\circ}C$                                                  |      | ±0.5 | ±5     | nA <sub>DC</sub> |

| Input Common               | T <sub>A</sub> =25°C (Note 7)                                                           | 0    |      | V+-1.5 | V <sub>DC</sub>  |

| Mode Voltage Range         |                                                                                         |      |      |        |                  |

| Supply Current             | R <sub>L</sub> =Infinite on all Comparators, T <sub>A</sub> =25°C                       |      | 60   | 100    | μA <sub>DC</sub> |

| Voltage Gain               | $V_O = 1 V_{DC}$ to 11 $V_{DC}$ ,                                                       |      | 500  |        | V/mV             |

|                            | $R_L = 15 \text{ k}\Omega, V^+ = 15 V_{DC}, T_A = 25^{\circ}C$                          |      |      |        |                  |

| Large Signal               | V <sub>IN</sub> =TTL Logic Swing, V <sub>REF</sub> =1.4 V <sub>DC</sub> ,               |      | 1.3  |        | μSec             |

| Response Time              | $V_{RL}$ =5 $V_{DC}$ , $R_L$ =5.1 $k\Omega$ , $T_A$ =25°C                               |      |      |        |                  |

| Response Time              | $V_{RL}$ =5 $V_{DC}$ , $R_L$ =5.1 $k\Omega$ , $T_A$ =25°C (Note 8)                      |      | 8    |        | μSec             |

| Output Sink Current        | $V_{IN}(-)=1 V_{DC}, V_{IN}(+)=0, V_{O}=2 V_{DC},$                                      | 15   | 30   |        | mA <sub>DC</sub> |

|                            | T <sub>A</sub> =25°C (Note 12)                                                          |      |      |        |                  |

|                            | $V_O=0.4 V_{DC}$                                                                        | 0.20 | 0.70 |        | mA <sub>DC</sub> |

| Output Leakage Current     | $V_{IN}(+)=1 V_{DC}, V_{IN}(-)=0, V_{O}=5 V_{DC}, T_{A}=25^{\circ}C$                    |      | 0.1  |        | nA <sub>DC</sub> |

| Input Offset Voltage       | (Note 10)                                                                               |      |      | ±9     | $mV_{DC}$        |

| Input Offset Current       | $I_{IN}(+)-I_{IN}(-)$                                                                   |      | ±1   | ±15    | nA <sub>DC</sub> |

| Input Bias Current         | I <sub>IN</sub> (+) or I <sub>IN</sub> (-) with Output in Linear Range                  |      | 4    | 40     | nA <sub>DC</sub> |

| Input Common               | Single Supply                                                                           | 0    |      | V+-2.0 | V <sub>DC</sub>  |

| Mode Voltage Range         |                                                                                         |      |      |        |                  |

| Output Sink Current        | $V_{IN}(-)=1 \ V_{DC}, \ V_{IN}(+)=0, \ V_{O}=2 \ V_{DC}$                               | 10   |      |        | mA <sub>DC</sub> |

| Output Leakage Current     | $V_{IN}(+)=1 V_{DC}, V_{IN}(-)=0, V_{O}=30 V_{DC}$                                      |      |      | 1.0    | μA <sub>DC</sub> |

| Differential Input Voltage | All V <sub>IN's</sub> ≥0 V <sub>DC</sub> (or V <sup>-</sup> on split supplies) (Note 9) |      |      | 36     | V <sub>DC</sub>  |

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional, but do not guarantee specific performance limits.

Note 2: For elevated temperature operation,  $T_j$  max is 125°C for the LP339.  $\theta_{ja}$  (junction to ambient) is 175°C/W for the LP339N and 120°C/W for the LP339M when either device is soldered in a printed circuit board in a still air environment. The low bias dissipation and the "ON-OFF" characteristic of the outputs keeps the chip dissipation very small ( $P_D \le 100$  mW), provided the output transistors are allowed to saturate.

Note 3: Short circuits from the output to V<sup>+</sup> can cause excessive heating and eventual destruction. The maximum output current is approximately 50 mA.

Note 4: This input current will only exist when the voltage at any of the input leads is driven negative. It is due to the collector-base junction of the input PNP transistors becoming forward biased and thereby acting as input clamp diodes. In addition to this diode action, there is also lateral NPN parasitic transistor action on the IC chip. This transistor action can cause the output voltage of the comparators to go to the V+ voltage level (or to ground for a large input overdrive) for the time duration that an input is driven negative. This is not destructive and normal output states will re-establish when the input voltage, which is negative, again returns to a value greater than -0.3 V<sub>DC</sub> (T<sub>A</sub>=25°C).

Note 5: These specifications apply for V<sup>+</sup>=5V<sub>DC</sub> and 0°C $\leq$ T<sub>A</sub> $\leq$ 70° C, unless otherwise stated. The temperature extremes are guaranteed but not 100% production tested. These parameters are not used to calculate outgoing AQL.

Note 6: The direction of the input current is out of the IC due to the PNP input stage. This current is essentially constant, independent of the state of the output, so no loading change exists on the reference or the input lines as long as the common-mode range is not exceeded.

Note 7: The input common-mode voltage or either input voltage should not be allowed to go negative by more than 0.3V. The upper end of the common-mode voltage range is  $V^+$ -1.5V ( $T_A$ =25°C), but either or both inputs can go to 30  $V_{DC}$  without damage.

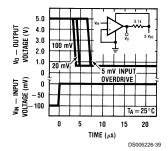

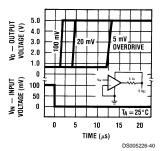

Note 8: The response time specified is for a 100 mV input step with 5 mV overdrive. For larger overdrive signals 1.3 µs can be obtained. See Typical Performance Characteristics section.

### **Electrical Characteristics** (Continued)

Note 9: Positive excursions of input voltage may exceed the power supply level. As long as the other voltage remains within the common-mode range, the comparator will provide a proper output state. The low input voltage state must not be less than -0.3 V<sub>DC</sub> (or 0.3 V<sub>DC</sub> below the magnitude of the negative power supply, if used) at T<sub>A</sub>=25°C.

Note 10: At output switch point,  $V_O$ =1.4V,  $R_S$ =0 $\Omega$  with  $V^+$  from 5  $V_{DC}$ ; and over the full input common-mode range (0  $V_{DC}$  to  $V^+$ -1.5  $V_{DC}$ ).

Note 11: For input signals that exceed V<sup>+</sup>, only the overdriven comparator is affected. With a 5V supply, V<sub>IN</sub> should be limited to 25V maximum, and a limiting resistor should be used on all inputs that might exceed the positive supply.

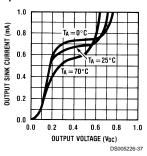

Note 12: The output sink current is a function of the output voltage. The LP339 has a bi-modal output section which allows it to sink large currents via a Darlington connection at output voltages greater than approximately 1.5 V<sub>DC</sub> and sink lower currents below this point. (See typical characteristics section and applications section)

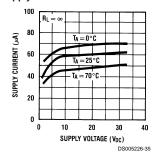

# **Typical Performance Characteristics**

### **Supply Current**

### Input Current

### **Output Sink Current**

### **Output Sink Current**

Response Times for Various Input Overdrives — Negative Transition

Response Times for Various Input Overdrives — Positive Transition

## **Application Hints**

All pins of any unused comparators should be tied to the negative supply.

The bias network of the LP339 establishes a drain current which is independent of the magnitude of the power supply voltage over the range of from 2  $\rm V_{DC}$  to 30  $\rm V_{DC}$ .

It is usually unnecessary to use a bypass capacitor across the power supply line.

The differential input voltage may be larger than V+ without damaging the device. Protection should be provided to prevent the input voltages from going negative more than -0.3 V $_{DC}$  (at  $25\,^{\circ}C$ ). An input clamp diode can be used as shown in the application section.

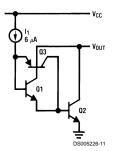

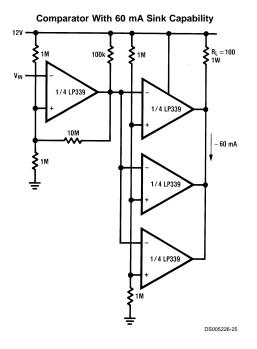

The output section of the LP339 has two distinct modes of operation-a Darlington mode and a grounded emitter mode. This unique drive circuit permits the LP339 to sink 30 mA at  $\rm V_O{=}2~\rm V_{DC}$  (Darlington mode) and 700  $\rm \mu A$  at  $\rm V_O{=}0.4~\rm V_{DC}$  (grounded emitter mode). Figure 1 is a simplified schematic diagram of the LP339 output section.

FIGURE 1.

Notice that the output section is configured in a Darlington connection (ignoring Q3). Therefore, if the output voltage is held high enough (V\_o≥1 V\_{DC}), Q1 is not saturated and the output current is limited only by the product of the betas of Q1, Q2 and I1 (and the  $60\Omega$   $R_{SAT}$  of Q2). The LP339 is thus capable of driving LED's, relays, etc. in this mode while maintaining an ultra-low power supply current of typically  $60~\mu\text{A}.$

If transistor Q3 were omitted, and the output voltage allowed to drop below about 0.8  $V_{\rm DC},$  transistor Q1 would saturate and the output current would drop to zero. The circuit would, therefore, be unable to "pull" low current loads down to ground (or the negative supply, if used). Transistor Q3 has been included to bypass transistor Q1 under these conditions and apply the current I1 directly to the base of Q2. The output sink current is now approximately I1 times the beta of Q2 (700  $\mu A$  at  $V_{\rm O}$ =0.4  $V_{\rm DC}$ ). The output of the LP339 exhibits a bi-modal characteristic with a smooth transition between modes. (See Output Sink Current graphs in Typical Performance Characteristics section.)

It is also important to note that in both cases the output is an uncommitted collector. Therefore, many collectors can be tied together to provide an output OR'ing function. An output pull-up resistor can be connected to any available power supply voltage within the permitted power supply voltage range and there is no restriction on this voltage due to the magnitude of the voltage which is applied to the V+ terminal of the LP339 package.

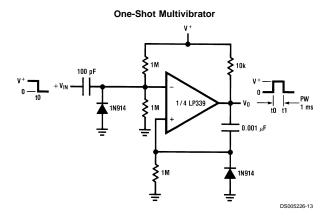

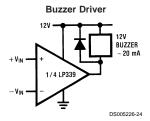

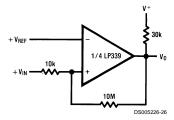

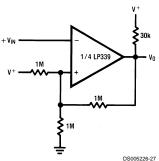

### Typical Applications (V+=15 V<sub>DC</sub>)

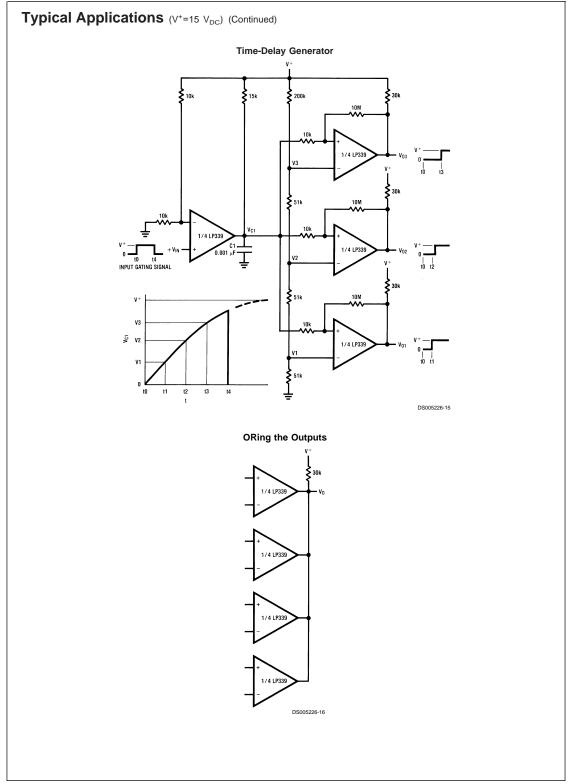

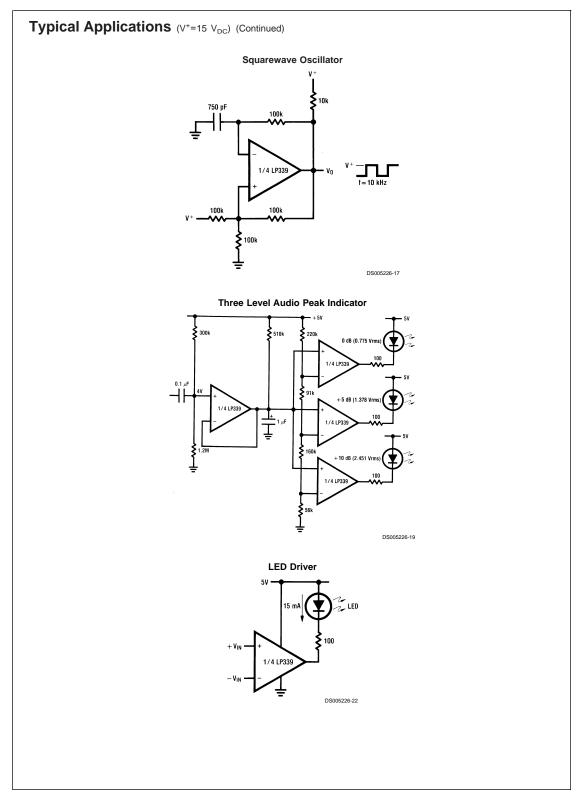

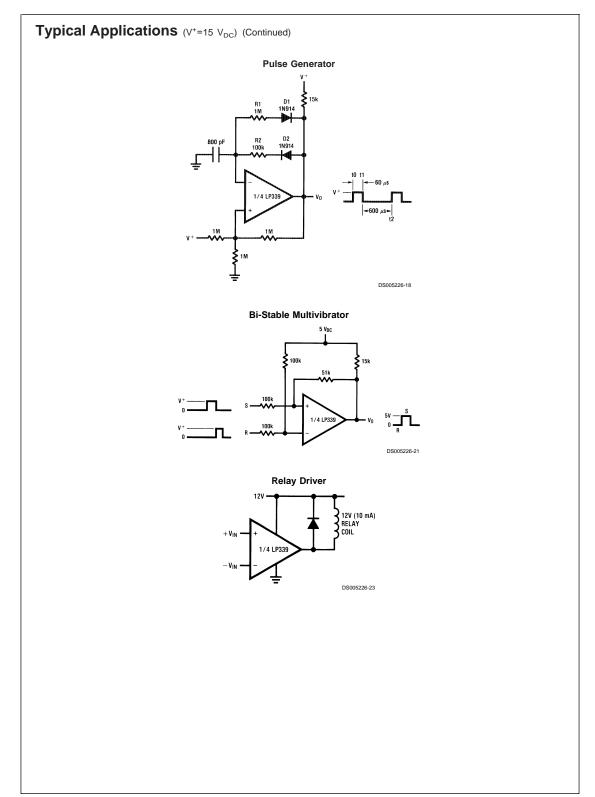

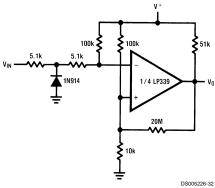

# Typical Applications (V<sup>+</sup>=15 $V_{DC}$ ) (Continued)

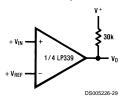

### Non-Inverting Comparator with Hysteresis

### **Inverting Comparator with Hysteresis**

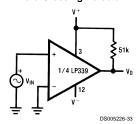

### **Basic Comparator**

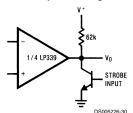

### **Output Strobing**

# Typical Applications (V+=15 V<sub>DC</sub>) (Continued)

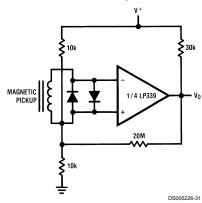

### Transducer Amplifier

# Zero Crossing Detector (Single Power Supply)

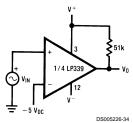

## Split-Supply Applications Zero Crossing Detector

### Comparator With a Negative Reference

# LP339 Ultra-Low Power Quad Comparator

# Notes

### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Corporation Americas

Tel: 1-800-272-9959 Fax: 1-800-737-7018 Email: support@nsc.com

www.national.com

National Semiconductor

Europe Fax: +49 (0) 1 80-530 85 86 Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 1 80-530 85 85 English Tel: +49 (0) 1 80-532 78 32 Français Tel: +49 (0) 1 80-532 93 88 Italiano Tel: +49 (0) 1 80-534 16 80

National Semiconductor Asia Pacific Customer Response Group Tel: 65-2544466 Fax: 65-2504466 Email: sea.support@nsc.com National Semiconductor Japan Ltd. Tel: 81-3-5639-7560 Fax: 81-3-5639-7507