September 2017

# FXWA9306 Dual Bi-Directional I<sup>2</sup>C-Bus<sup>®</sup> and SMBus Voltage-Level Translator

## **Features**

- 2-Bit Bi-Directional Translator for SDA and SCL Lines in Mixed-Mode I<sup>2</sup>C-Bus Applications

- Standard-Mode, Fast-Mode, and Fast-Mode-Plus I<sup>2</sup>C-Bus and SMBus Compatible

- Less than 1.5ns Maximum Propagation Delay to Accommodate Standard-Mode and Fast-Mode I<sup>2</sup>C-Bus Devices and Multiple Masters

- Allows Voltage Level Translation Between:

- V<sub>CCA</sub> = 1.0 to 3.6V and V<sub>CCB</sub> = 1.8-5.0V

- Supports I<sup>2</sup>C Clock Stretching and Multi-Master

- Provides Bi-directional Voltage Translation without Direction Pin

- Low 3.5Ω On-State Connection Between Input and Output Ports; Provides Less Signal Distortion

- Open-Drain I<sup>2</sup>C-Bus I/O Ports (A0, A1, B0, and B1)

- 5V-Tolerant I<sup>2</sup>C-Bus I/O Ports to Support Mixed-Mode Signal Operation

- Lock-Up-Free Operation

- Flow-Through Pinout for Simpler Printed-Circuit Board Trace Routing

- Packaged in 8-Terminal Leadless MicroPak™ (1.6mm x 1.6mm) and MSOP8 (TSSOP8)

## **Description**

The FXWA9306 is a dual, bi-directional,  $I^2C$ -bus and SMBus, voltage-level translator with an enable (OE) input that is operational from 1.0V to 3.6V ( $V_{\rm CCA}$ ) and 1.8V to 5.5V ( $V_{\rm CCB}$ ) without requiring a direction pin.

As with standard  $I^2C$ -bus systems, pull-up resistors are required to provide the logic HIGH levels on the translator's bus. The FXWA9306 has a standard opendrain configuration of the  $I^2C$ -bus. The size of these pull-up resistors depends on the system, but each side of the translator must have a pull-up resistor. The device is designed to work with Standard-Mode, Fast-Mode, and Fast Mode Plus  $I^2C$ -bus devices in addition to SMBus devices. The maximum frequency is dependent on the RC time constant, but generally supports > 2MHz.

All channels have the same electrical characteristics and there is a minimum deviation from one output to another in voltage or propagation delay. This is a benefit over discrete transistor voltage translation solutions, since the fabrication of the switch is symmetrical. The translator provides excellent ESD protection to lower voltage devices and at the same time protects less-ESD resistant devices.

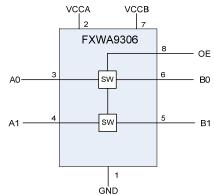

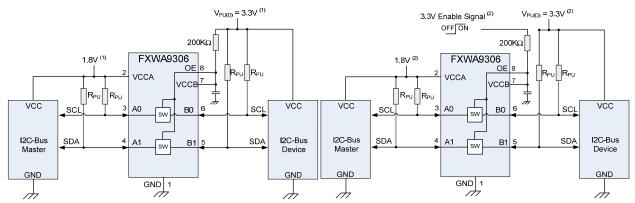

Figure 1. Block Diagram

# **Ordering Information**

| Part Number | Operating<br>Temperature Range | Top Mark | Package                        | Packing Method                 |

|-------------|--------------------------------|----------|--------------------------------|--------------------------------|

| FXWA9306L8X | -40 to +85°C                   | LT       | 8-Lead, MicroPak™, 1.6mm Wide  | 5000 Units on<br>Tape and Reel |

| FXWA9306MUX | -40 to +85°C                   | 9306     | 8-Lead, MSOP Package, 3mm Wide | 4000 Units on<br>Tape and Reel |

# **Pin Configuration**

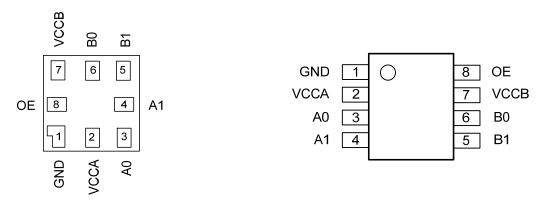

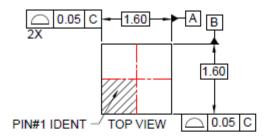

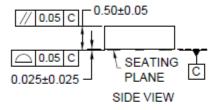

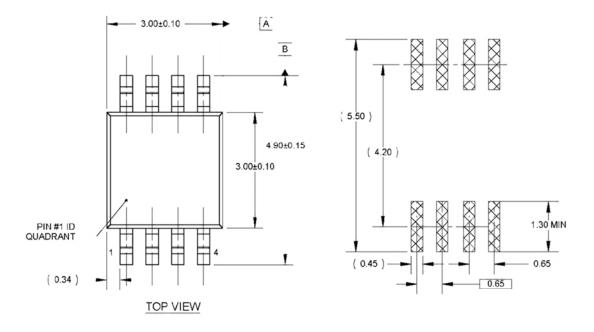

Figure 2. MicroPak™ (Top-Through View)

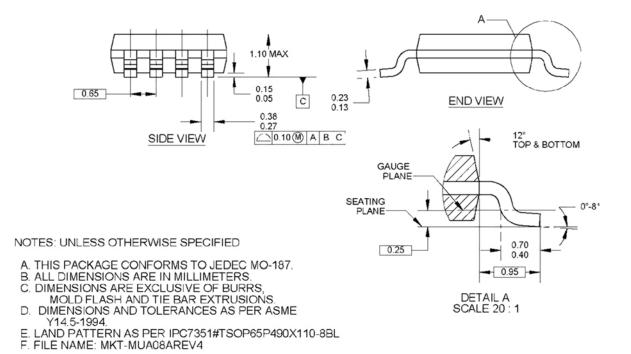

Figure 3. MSOP (Top-Through View)

## **Pin Definitions**

| Pin # | Name                  | Description                                                                             |

|-------|-----------------------|-----------------------------------------------------------------------------------------|

| 1     | GND                   | Ground                                                                                  |

| 2     | Vcca                  | Low Voltage A-Side Power Supply                                                         |

| 3     | <b>A</b> <sub>0</sub> | A-Side Input or 3-State Output. Connect to V <sub>CCA</sub> through a pull-up resistor. |

| 4     | A <sub>1</sub>        | A-Side Input or 3-State Output. Connect to V <sub>CCA</sub> through a pull-up resistor. |

| 5     | B <sub>1</sub>        | B-Side Input or 3-State Output. Connect to V <sub>CCB</sub> through a pull-up resistor. |

| 6     | B <sub>0</sub>        | B-Side Input or 3-State Output. Connect to V <sub>CCB</sub> through a pull-up resistor. |

| 7     | V <sub>CCB</sub>      | High Voltage B-Side Power Supply                                                        |

| 8     | OE                    | Output Enable Input; connect to V <sub>CCB</sub> and pull-up through a high resistor.   |

## **Truth Table**

| Control          | Outputs                            |  |  |

|------------------|------------------------------------|--|--|

| OE               |                                    |  |  |

| LOW Logic Level  | 3-State                            |  |  |

| HIGH Logic Level | Normal Operation; A0 = B0, A1 = B1 |  |  |

## Note:

- 1. If the OE pin is driven LOW, the FXWA9306 is disabled and the A<sub>0</sub>, A<sub>1</sub>, B<sub>0</sub>, and B<sub>1</sub> pins are forced into 3-state.

- 2. OE references V<sub>CCB</sub> and the OE logic levels should be at least 1V higher than V<sub>CCA</sub>, for best translator operation.

# **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol                            | Parameter                          |                                          | Min. | Max.                    | Units |  |

|-----------------------------------|------------------------------------|------------------------------------------|------|-------------------------|-------|--|

| VCCA, VCCB                        | Supply Voltage                     |                                          | -0.5 | 7.0                     |       |  |

|                                   |                                    | A Port                                   | -0.5 | 7.0                     | V     |  |

| $V_{IN}$                          | DC Input Voltage                   | B Port                                   | -0.5 | 7.0                     |       |  |

|                                   |                                    | Control Input (OE)                       | -0.5 | 7.0                     |       |  |

|                                   |                                    | An Outputs 3-State                       | -0.5 | 7.0                     |       |  |

| \/ <sub>-</sub>                   | Output Voltage(3)                  | B <sub>n</sub> Outputs 3-State           | -0.5 | 7.0                     | V     |  |

| Vo                                | Output Voltage <sup>(3)</sup>      | An Outputs Active                        | -0.5 | V <sub>CCA</sub> + 0.5V | V     |  |

|                                   |                                    | B <sub>n</sub> Outputs Active            | -0.5 | V <sub>CCB</sub> + 0.5V |       |  |

| Існ                               | DC Channel Current                 |                                          |      | 90                      | mA    |  |

| lıĸ                               | DC Input Diode Current             | At V <sub>IN</sub> < 0V                  |      | -50                     | mA    |  |

| 1                                 | DC Output Diode Current            | At Vo < 0V                               |      | -50                     | mA    |  |

| Іок                               |                                    | At Vo > Vcc                              |      | +50                     |       |  |

| I <sub>OH</sub> / I <sub>OL</sub> | DC Output Source/Sink Curi         | rent                                     | -50  | +50                     | mA    |  |

| Icc                               | DC Vcc or Ground Current p         | er Supply Pin                            |      | ±100                    | mA    |  |

| Tstg                              | Storage Temperature Range          | •                                        | -65  | +150                    | °C    |  |

| ILATCHUP                          | Latch-up Performance Abov          | e V <sub>CC</sub> and below GND at 125°C |      | <u>+</u> 100            | mA    |  |

|                                   |                                    | Human Body Model, JESD22-A114-A          |      | > 4000                  |       |  |

| ESD                               | Electrostatic Discharge Capability | Human Body Model, Pin to Pin, B Port(4)  |      | > 8000                  | V     |  |

|                                   | Capability                         | Charged Device Model, JESD22-A115-A      |      | > 1000                  |       |  |

#### Notes:

- 3. Io absolute maximum rating must be observed.

- 4. Test conditions: B0 and B1 vs. VccB, B0 and B1 vs. GND, VccB vs. GND

# **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. ON Semiconductor does not recommend exceeding them or designing to Absolute Maximum Ratings.

| Symbol                |                                         | Parameter              |   |     |     | Units |

|-----------------------|-----------------------------------------|------------------------|---|-----|-----|-------|

| V <sub>CCA</sub>      | Power Supply Operat                     | ing                    |   | 1.0 | 5.5 | V     |

| Vccb                  | Power Supply Operat                     | Power Supply Operating |   |     | 5.5 | V     |

|                       |                                         | A Port                 |   | 0   | 5.5 |       |

| $V_{IN}$              | Input Voltage                           | B Port                 |   | 0   | 5.5 | V     |

|                       |                                         | Control Input (OE)     |   | 0   | 5.5 |       |

| ΘЈА                   | Thermal Resistance, Junction to Ambient |                        |   |     | 470 | C°/W  |

| I <sub>SW(pass)</sub> | Pass Switch Current                     |                        | 0 | 64  | mA  |       |

| T <sub>A</sub>        | Free Air Operating Te                   | emperature             |   | -40 | +85 | °C    |

#### Notes:

- 5. All unused inputs and I/O pins must be held at V<sub>CCI</sub> or GND.

- V<sub>CCA</sub> ≤ V<sub>CCB</sub> -1V for best results in level-shifting applications.

## **DC Electrical Characteristics**

Unless otherwise noted, values are at  $T_A = -40$ °C to +85°C; all typical values are at  $T_A = 25$ °C.

| Symbol             | Parameter                                      | (                                                  | Conditions                        | Min. | Тур. | Max. | Unit |

|--------------------|------------------------------------------------|----------------------------------------------------|-----------------------------------|------|------|------|------|

| Vıĸ                | Input Clamping Voltage                         | I <sub>I</sub> = -18mA; V                          | <sub>I(OE)</sub> = 0V             |      |      | -1.2 | V    |

| Іін                | High-Level Input Current                       | V <sub>I</sub> = 5V; V <sub>I(OE</sub>             | E) = 0V                           |      |      | 5    | μA   |

| C <sub>i(OE)</sub> | OE Pin Input Capacitance                       | V <sub>I</sub> = 3V or 0V                          | 1                                 |      | 7.1  |      | pF   |

| Ci/O(off)          | Off-State I/O Pin Capacitance A0, A1, B0, B1   | V <sub>O</sub> = 3V or 0V; V <sub>I(OE)</sub> = 0V |                                   |      | 4    | 6    | pF   |

| Ci/O(on)           | On-State I/O Pin Capacitance<br>A0, A1, B0, B1 | V <sub>O</sub> = 3V or 0V; V <sub>I(OE)</sub> = 3V |                                   |      | 9.3  | 12.5 | pF   |

|                    |                                                | V <sub>I</sub> = 0V;<br>I <sub>O</sub> = 64mA      | V <sub>I(OE)</sub> = 4.5V         |      | 2.4  | 5.0  |      |

| D (7)              | On-State Resistance A0/B0,                     |                                                    | $V_{I(OE)} = 3V$                  |      | 3.0  | 6.0  | Ω    |

| Ron <sup>(7)</sup> | A1/B1                                          |                                                    | $V_{I(OE)} = 2.3V$                |      | 3.8  | 8.0  | 12   |

|                    |                                                |                                                    | V <sub>I(OE)</sub> = 1.5V         |      | 9.0  | 20.0 |      |

|                    |                                                | V <sub>CCA</sub> = 1V,                             | V <sub>IN</sub> (B0 or B1) = 0.1V |      |      | 0.15 |      |

| Vol                | Voltage Output Low                             | $V_{PUD} = 5V$ , $I_{OL} = 3mA$                    | $V_{IN}$ (B0 or B1) = 0.2V        |      |      | 0.25 | V    |

| VOL                |                                                |                                                    | $V_{IN}$ (B0 or B1) = 0.3V        |      |      | 0.35 | V    |

|                    |                                                | (B->A Dir)                                         | $V_{IN}$ (B0 or B1) = 0.4V        |      |      | 0.45 |      |

#### Notes:

<sup>7.</sup> Measured by the voltage drop between the A0 and B0 or A1 and B1 terminals at the indicated current through the switch. On-state resistance is determined by the lowest voltage of the two terminals.

# **AC Electrical Characteristics**

$T_A = -40$ °C to +85°C. Direction is from B port to A port (translating down). Values guaranteed by design.

| Symbol           | Parameter                                                        | Conditions                                                                                          | Load<br>Condition:    | Min: | Max. | Units |

|------------------|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-----------------------|------|------|-------|

|                  | Low-to-High Propagation Delay,                                   |                                                                                                     | C <sub>L</sub> = 15pF | 0    | 0.60 | ns    |

| t <sub>PLH</sub> | from (Input) B0 or B1 to (Output)                                |                                                                                                     | C <sub>L</sub> = 30pF | 0    | 1.20 |       |

|                  | A0 or A1                                                         | $V_{I(OE)} = 3.3V$ ; $V_{IH} = 3.3V$ ;                                                              | C <sub>L</sub> = 50pF | 0    | 2.00 |       |

|                  | High-to-Low Propagation Delay,                                   | $V_{IL} = 0V; V_{M} = 1.15V;$<br>$V_{CCA} = 2.3V$                                                   | C <sub>L</sub> = 15pF | 0    | 0.75 |       |

| $t_{PHL}$        | from (Input) B0 or B1 to (Output)                                |                                                                                                     | C <sub>L</sub> = 30pF | 0    | 1.50 | ns    |

|                  | A0 or A1                                                         |                                                                                                     | C <sub>L</sub> = 50pF | 0    | 2.00 |       |

|                  | Low-to-High Propagation Delay,                                   |                                                                                                     | C <sub>L</sub> = 15pF | 0    | 0.60 |       |

| $t_{PLH}$        |                                                                  |                                                                                                     | C <sub>L</sub> = 30pF | 0    | 1.20 | ns    |

|                  |                                                                  | $V_{I(OE)} = 2.5V$ ; $V_{IH} = 2.5V$ ; $V_{IL} = 0V$ ; $V_{M} = 0.75V$ ;                            | C <sub>L</sub> = 50pF | 0    | 2.00 |       |

|                  | High-to-Low Propagation Delay, from (Input) B0 or B1 to (Output) | $V_{CCA} = 1.5V$                                                                                    | C <sub>L</sub> = 15pF | 0    | 0.75 | ns    |

| t <sub>PHL</sub> |                                                                  |                                                                                                     | C <sub>L</sub> = 30pF | 0    | 1.50 |       |

|                  | A0 or A1                                                         |                                                                                                     | C <sub>L</sub> = 50pF | 0    | 2.00 |       |

|                  | Low-to-High Propagation Delay,                                   | V <sub>I(OE)</sub> = 3.3V; V <sub>IH</sub> = 2.3V;<br>V <sub>IL</sub> = 0V; V <sub>TT</sub> = 3.3V; | C <sub>L</sub> = 15pF | 0    | 0.50 | ns    |

| t <sub>PLH</sub> | from (Input) A0 or A1 to (Output)                                |                                                                                                     | C <sub>L</sub> = 30pF | 0    | 1.00 |       |

|                  | B0 or B1                                                         |                                                                                                     | C <sub>L</sub> = 50pF | 0    | 1.75 |       |

|                  | High-to-Low Propagation Delay,                                   | $V_M = 1.15V$ ; $V_{CCA} = 2.3V$ ;                                                                  | C <sub>L</sub> = 15pF | 0    | 0.80 |       |

| t <sub>PHL</sub> | from (Input) A0 or A1 to (Output)                                |                                                                                                     | C <sub>L</sub> = 30pF | 0    | 1.65 | ns    |

|                  | B0 or B1                                                         |                                                                                                     | C <sub>L</sub> = 50pF | 0    | 2.75 |       |

|                  | Low-to-High Propagation Delay,                                   |                                                                                                     | C <sub>L</sub> = 15pF | 0    | 0.50 |       |

| $t_{PLH}$        | from (Input) A0 or A1 to (Output)                                | $V_{I(OE)} = 2.5V; V_{IH} = 1.5V;$                                                                  | C <sub>L</sub> = 30pF | 0    | 1.00 | ns    |

|                  | B0 or B1                                                         | $V_{I(OE)} = 2.5V$ , $V_{IH} = 1.5V$ ,<br>$V_{IL} = 0V$ ; $V_{TT} = 2.5V$ ;                         | C <sub>L</sub> = 50pF | 0    | 1.75 |       |

|                  | High-to-Low Propagation Delay,                                   | $V_M = 0.75V$ ; $V_{CCA} = 1.5V$ ;                                                                  | C <sub>L</sub> = 15pF | 0    | 1.00 |       |

| <b>t</b> PHL     | from (Input) A0 or A1 to (Output)                                | $R_L = 300\Omega$                                                                                   | C <sub>L</sub> = 30pF | 0    | 2.00 | ns    |

|                  | B0 or B1                                                         |                                                                                                     | C <sub>L</sub> = 50pF | 0    | 3.30 |       |

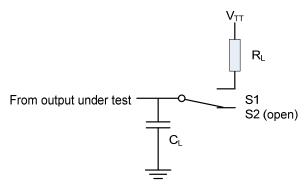

Load Circuit

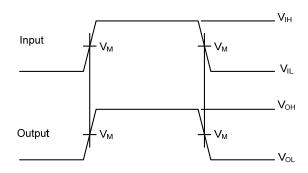

**Timing Diagram**

Figure 4. Load Circuit

#### Notes:

- 8. S1 = translating up (A-to-B direction), S2 = translating down (B-to-A direction).

- 9. C<sub>L</sub> includes probe and jig capacitance.

- 10. All input pulses are supplied by generators having the following characteristics: PRR  $\leq$  10MHz;  $Z_0$  = 50 $\Omega$ ;  $t_r \leq$  2ns;  $t_f \leq$  2ns.

- 11. The outputs are measured one at a time, with one transmission per measurement.

# **Application Information**

Figure 5. Application (Switch Always Enabled)

Figure 6. Application (Switch Enable Control)

#### Note:

12. The applied voltages at V<sub>CCA</sub> and V<sub>PU(D)</sub> should be such that V<sub>CCB</sub> is at least 1V higher than V<sub>CCA</sub> for best translator operation.

## **Bi-directional Translation**

For the bi-directional clamping configuration (higher voltage to lower voltage or lower voltage to higher voltage), the OE input must be connected to  $V_{\rm CCB}$  and both pins pulled to HIGH side  $V_{\rm PU(D)}$  through a pull-up resistor (typically  $200 k\Omega$ ). This allows  $V_{\rm CCB}$  to regulate the OE input. A filter capacitor on  $V_{\rm CCB}$  is recommended. The I²C-bus master output can be totem-pole or opendrain (pull-up resistors may be required) and the I²C-bus device output can be totem-pole or open-drain (pull-up resistors are required to pull the B0 and B1 outputs to  $V_{\rm PU(D)}$ ). However, if either output is totem-pole, data must be uni-directional or the outputs must be 3-

stateable and be controlled by some direction-controlled mechanism to prevent HIGH-to-LOW contentions in either direction. If both outputs are open-drain, no direction control is needed.

The reference supply voltage ( $V_{\rm CCA}$ ) is connected to the processor core power supply voltage. When  $V_{\rm CCB}$  is connected through a  $200 k\Omega$  resistor to a  $3.3 V - 5.5 V V_{\rm PU(D)}$  power supply, and  $V_{\rm CCA}$  is set between 1.0V and ( $V_{\rm PU(D)} - 1V$ ), the output of each A0 and A1 has a maximum output voltage equal to  $V_{\rm CCA}$  and the output of each B0 and B1 has a maximum output voltage equal to  $V_{\rm PU(D)}$ .

**Table 1. Application Operating Conditions** (refer to Figure 6)

All typical values are at  $T_A = 25$ °C.

| Symbol                                | Parameter              | Conditions            | Min.                   | Тур. | Max. | Unit |

|---------------------------------------|------------------------|-----------------------|------------------------|------|------|------|

| V <sub>BIAS</sub> (V <sub>CCB</sub> ) | Reference Bias Voltage |                       | V <sub>CCA</sub> + 0.6 | 2.1  | 5.0  | ٧    |

| V <sub>I(OE)</sub>                    | OE Pin Input Voltage   |                       | V <sub>CCA</sub> + 0.6 | 2.1  | 5.0  | ٧    |

| Vcca                                  | Reference Voltage      |                       | 0                      | 1.5  | 4.4  | ٧    |

| I <sub>SW(pass)</sub>                 | Pass Switch Current    |                       |                        | 14   |      | mA   |

| I <sub>REF</sub>                      | Reference Current      | Transistor            |                        | 5    |      | μA   |

| TA                                    | Ambient Temperature    | Operating in Free Air | -40                    |      | +85  | °C   |

## Sizing Pull-Up Resistor

The pull-up resistor value needs to limit the current through the pass transistor when it is in the on state to about 15mA. This ensures a pass voltage of 260mV to 350mV. If the current through the pass transistor is higher than 15mA, the pass voltage is higher in the on state. To set the current through each pass transistor at 15mA, the pull-up resistor value is calculated as:

$$R_{PU} = \frac{V_{PU}(D) - 0.35V}{0.015A} \tag{1}$$

Table 2 summarizes the resistor reference voltages and currents at 15mA, 10mA, and 3mA. The resistor values shown in the +10% column or a larger value should be used to ensure that the pass voltage of the transistor would be 350mV or less. The external driver must be able to sink the total current from the resistors on both sides of the of the FXWA9306 device at 0.175V, although the 15mA only applies to the current flowing through the FXWA9306 device.

## **Table 2. Application Operating Conditions**

Calculated for  $V_{OL}$  = 0.35V; assumes output driver  $V_{OL}$  = 0.175V at stated current.

|             | Pull-Up Resistor Value (Ω) |                      |         |                              |      |                             |  |

|-------------|----------------------------|----------------------|---------|------------------------------|------|-----------------------------|--|

| $V_{PU(D)}$ | 15mA                       |                      | 10mA    |                              | 3mA  |                             |  |

|             | Nominal                    | +10% <sup>(13)</sup> | Nominal | Nominal +10% <sup>(13)</sup> |      | <b>+10%</b> <sup>(13)</sup> |  |

| 5.0V        | 310                        | 341                  | 465     | 512                          | 1550 | 1705                        |  |

| 3.3V        | 197                        | 217                  | 295     | 325                          | 983  | 1082                        |  |

| 2.5V        | 143                        | 158                  | 215     | 237                          | 717  | 788                         |  |

| 1.8V        | 97                         | 106                  | 145     | 160                          | 483  | 532                         |  |

| 1.5V        | 77                         | 85                   | 115     | 127                          | 383  | 422                         |  |

| 1.2V        | 57                         | 63                   | 85      | 94                           | 283  | 312                         |  |

#### Note:

13. +10% to compensate for V<sub>CC</sub> range and resistor tolerance.

# **Maximum Frequency Calculation**

The maximum frequency is totally dependent upon the specifics of the application. The FXWA9306 behaves like a wire with the additional characteristics of transistor device physics and should be capable of performing at higher frequencies if used correctly.

Here are some guidelines to follow that help maximize the performance of the device:

- Keep trace lengths to a minimum by placing the FXWA9306 close to the processor.

- The trace length should be less than half the time of flight to reduce ringing and reflections.

- The faster the edge of the signal, the higher the chance of ringing.

- The greater the drive strength (up to 15mA), the higher the frequency the device can use.

In a 3.3V to 1.8V direction level shift, if the 3.3V side is being driven by a totem-pole type driver; no pull-up resistor is needed on the 3V side. The capacitance and

line length of concern is on the 1.8V side because it is driven through the on resistance of the FXWA9306. If the line length on the 1.8V side is long enough, there can be a reflection at the chip / terminating end of the wire when the transition time is shorter than the time of flight of the wire. This is because the FXWA9306 looks like a high-impedance path compared to the wire. If the wire is too long and the lumped capacitance is not excessive, the signal is only slightly degraded by the series resistance added by passing through the FXWA9306. If the lumped capacitance is large, the rise time deteriorates. The fall time is much less affected and if the rise time is slowed down too much, the duty cycle of the clock is degraded and, at some point, the clock is no longer useful. So, the principle design consideration is to minimize the wire length and the capacitance on the 1.8V side for the clock path. A pullup resistor on the 1.8V side can be used to trade a slower fall time for a faster rise time and can also reduce overshoot in some cases.

#### **Additional Note**

The FXWA9306 is not a bus buffer that provides both level translation and physical capacitance isolation to either side of the bus when both sides are connected. The FXWA9306 only isolates the sides when the device is disabled and provides level translation when active.

The FXWA9306 can be used to run two buses: one at 400kHz operating frequency and the other at 100kHz operating frequency. If the two buses are operating at different frequencies, the 100kHz bus must be isolated when the 400kHz operation of the bus is required. If the master is running at 400kHz, the maximum system operating frequency may be less than 400kHz because of the delays added to the translator.

When the A1 or B1 port is LOW, the clamp is in the ON-state and a low-resistance connection exists between the A1 and B1 ports. Assuming the higher voltage is on the B1 port, when the B1 port is HIGH, the voltage on the A1 port is limited by the voltage set by  $V_{\text{CCA}}$ . When the A1 port is HIGH, the B1 port is pulled to the drain pull-up supply voltage ( $V_{\text{PU(D)}}$ ) by the pull-up resistors. This functionality allows a seamless translation between higher and lower voltages selected by the user without the need for directional control. The A0/B0 channel also functions as the A1/B1 channel-

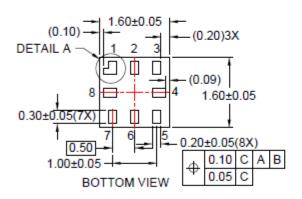

# **Physical Dimensions**

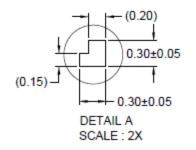

## NOTES:

- A. PACKAGE CONFORMS TO JEDEC MO-255 VARIATION UAAD.

- B. DIMENSIONS ARE IN MILLIMETERS.

- C. DIMENSIONS AND TOLERANCES PER ASME Y14.5M, 2009.

- D. LAND PATTERN RECOMMENDATION IS EXISTING INDUSTRY LAND PATTERN.

- E. DRAWING FILENAME: MKT-MAC08Arev5.

Figure 7. 8-Lead MicroPak™, 1.6mm Wide

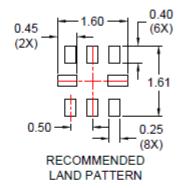

# **Physical Dimensions**

Figure 8. 8-Lead MSOP, 3.0mm Wide

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that ON Semiconductor was negligent regarding the design or manufacture of the part. ON Semiconductor is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA

Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada

Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free

USA/Canada.

Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910

Japan Customer Focus Center

Phone: 81-3-5817-1050

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative