# FSUSB242 Type-C USB Port Protection Switch

#### **Features**

- Fully USB Data Port Protection

- V<sub>DD</sub> 0 V 5.5 V (12 V DC tolerant)

- −18 V to +20 V DC Tolerance on HSD± Port

- ±25 V IEC 64000-4-5 Surge Protection w/o External TVS

- V<sub>DD</sub> Operating Range, 2.7 V–5.5 V

- HSD RON: 5 Ω Typical

- C<sub>ON</sub> = 5 pF Typical

- Wide –3 dB Bandwidth: > 720 MHz

- Low Power Operation: I<sub>CC</sub> < 10 μA (Typical)

- Over Voltage Protection: 3.6 V & 4.5 V

# **Typical Applications**

- Smartphones

- Tablets

- Laptops

# Safety Mechanisms Highlight

- 3.6 V & 4.5 V OVP Trip Point

- ±25 V Surge Protection without Need for External TVS

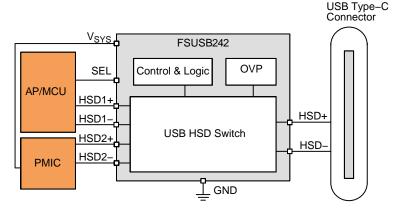

Figure 1. Application Schematic

# ON Semiconductor®

www.onsemi.com

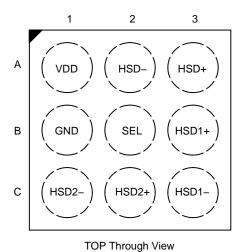

WLCSP9 1.20 × 1.20 CASE 567UL

#### **MARKING DIAGRAM**

MT = Specific Device Code&K = 2 Digit Lot Run Code

X = Year

Y = 2 Week Data CodeZ = Plant Code

#### **PIN CONNECTION**

# ORDERING INFORMATION

See detailed ordering and shipping information on page 11 of this data sheet.

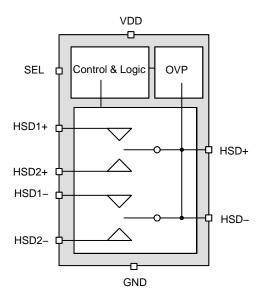

Figure 2. Simplified Block Diagram

**Table 1. PIN FUNCTION DESCRIPTION**

| CSP Bump | Name  | Туре   | Description                        |

|----------|-------|--------|------------------------------------|

| A1       | VDD   | Power  | Supply Power                       |

| B1       | GND   | Ground | Ground                             |

| A3       | HSD+  | Data   | Common High Speed Data Bus         |

| A2       | HSD-  | Data   | Common High Speed Data Bus         |

| B3       | HSD1+ | Data   | Multiplexed High Speed Data Port 1 |

| C3       | HSD1- | Data   | Multiplexed High Speed Data Port 1 |

| C2       | HSD2+ | Data   | Multiplexed High Speed Data Port 2 |

| C1       | HSD2- | Data   | Multiplexed High Speed Data Port 2 |

| B2       | SEL   | I/O    | Tri-Input HSD Switch Select & /OE  |

**Table 2. SWITCH TRUTH TABLE CONFIGURATION**

| VDD   | SEL                         | Switch Configuration          |

|-------|-----------------------------|-------------------------------|

| UVLO  | X Switch off High impedance |                               |

| Valid | 0                           | HSD+ = HSD1+, HSD- = HSD1-    |

| Valid | 1                           | HSD+ = HSD2+, HSD- = HSD2-    |

| Valid | Float/High–Z                | Switch Disable High impedance |

#### **APPLICATION INFORMATION**

# **Over Voltage Protection**

Over voltage protection turns the switch off if the inputs HSD+/HSD- rise above the over voltage trip threshold.

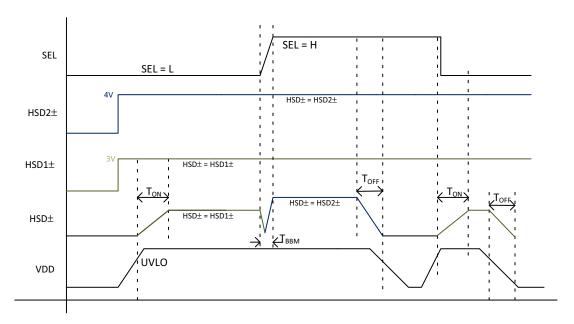

# **Under Voltage Lockout**

The under-voltage lockout on  $V_{DD}$  pin turns the switch off if the  $V_{DD}$  voltage drops below the lockout threshold. With the SELpin active, the input voltage rising above the UVLO threshold releases the lockout and enables the switch.

# Tri-State Input Control Pin (SEL)

The SEL pin can be tri-stated to disable the switch to save power, there are a few ways to achieve this. If the SEL pin is controlled by GPIO in the system, if the GPIO pin has a High-Z state where the impedance of the High-Z state is

larger then 2 M $\Omega$  the switch will recognize the High–Z state and disable the switch. If the system does not have GPIO that supports High–Z state, the user can utilize 2 MOSFETs or a Logic Device to achieve the same result.

#### For GPIO

The SEL pin function below:

- If the input is pulled up with less than 50 k $\Omega$  it will be considered as Logic High

- If the input is pulled down with less than 50 k $\Omega$  it will be consider as Logic Low

- If the input is pulled up or down with more 4 M $\Omega$  it will be consider as float/High–Z

#### **System Timing Diagram**

Figure 3. System Timing Plot

# **System Block Diagrams**

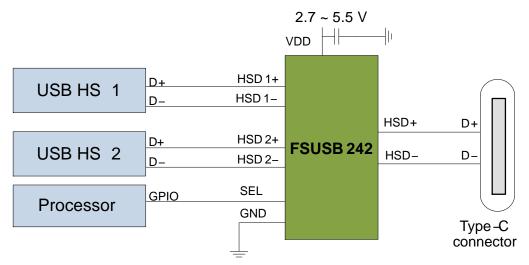

Figure 4. Application of 2x USB HS interface

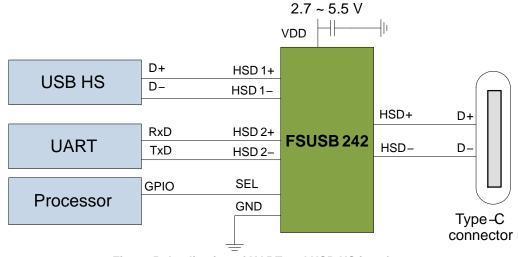

Figure 5. Application of UART and USB HS interface

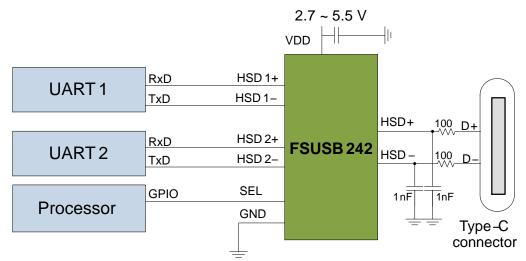

Figure 6. Application of 2x UART interface

When 2x UART signals are switched over FSUSB242, both 100 ohm series resistor and 1 nF bypass capacitors are recommended in the common switch path as above. If FSUSB242 is used to switch USB and UART signals, connect UART signals to HSD1.

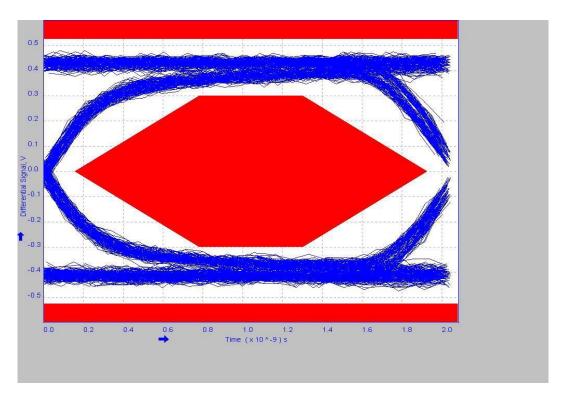

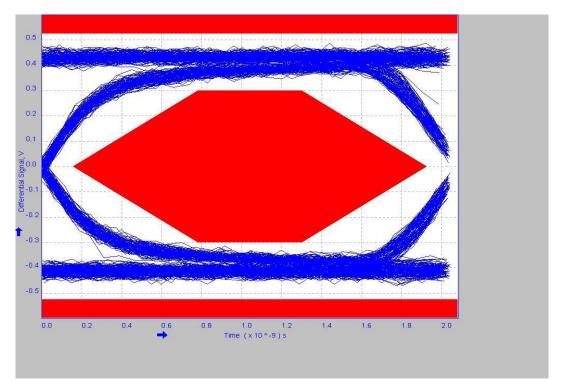

# **USB High Speed Eye Diagram**

$V_{DD} = 5.5 V HSD to HSD1 Path$

Figure 7. HS USB Eye @  $V_{DD} = 5 V$

$V_{DD} = 2.7 V HSD$  to HSD2 Path

Figure 8. HS USB Eye @  $V_{DD}$  = 2.7 V

**Table 3. ABSOLUTE MAXIMUM RATINGS**

| Symbol               | Parameter                                  |                                      |         |      | Max  | Unit |

|----------------------|--------------------------------------------|--------------------------------------|---------|------|------|------|

| $V_{DD}$             | Supply Voltage from V <sub>DD</sub>        |                                      | -0.5    | 12.0 | V    |      |

| $V_{SW}$             | DC Input voltage tolerance for HSD±, to    | GND                                  |         | -18  | 20   | V    |

|                      | DC Input voltage tolerance for HSD1±, H    | HSD2± to GND                         |         | -1.2 | 6    | V    |

| V <sub>CONTROL</sub> | DC Input Voltage (SEL)                     |                                      |         | -0.5 | 6    | V    |

| I <sub>SW</sub>      | DC HSD Switch Current                      |                                      |         |      | 100  | mA   |

| I <sub>IK</sub>      | DC Input Diode Current                     |                                      |         | -50  |      | mA   |

| T <sub>STORAGE</sub> | Storage Temperature Range                  |                                      |         | -65  | +150 | °C   |

| TJ                   | Maximum Junction Temperature               | Maximum Junction Temperature         |         |      | +150 | °C   |

| TL                   | Lead Temperature (Soldering, 10 second     | ds)                                  |         |      | +260 | °C   |

| ESD                  | IEC 61000-4-2 System ESD                   |                                      | Air Gap | 15   |      | kV   |

|                      |                                            |                                      | Contact | 8    |      |      |

|                      | Human Body Model, JEDEC                    | Power to GND                         |         | 2    |      | kV   |

|                      | JESD22-A114                                | Internal Pin to GND (HSD1±, HSD2±)   |         | 2    |      |      |

|                      |                                            | External Pin to GND (HSD±)  All Pins |         | 14   |      |      |

|                      | Charged Device Model, JEDEC<br>LESD22-C101 |                                      |         | 1    |      |      |

|                      | IEC 61000–4–5 Surge Protection             | HSD±, to GND                         |         | ±25  |      | ٧    |

|                      |                                            | V <sub>DD</sub> to GND               |         | +12  |      | V    |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

**Table 4. RECOMMENDED OPERATING CONDITIONS**

| Symbol             | Parameter                                     | Min  | Тур | Max             | Unit |

|--------------------|-----------------------------------------------|------|-----|-----------------|------|

| $V_{DD}$           | Supply Voltage                                | 2.7  | 4.2 | 5.5             | V    |

| V <sub>SW1</sub>   | HSD1 Switch I/O Signal Swing Voltage (Note 1) | -0.5 |     | 3.6             | V    |

| V <sub>SW2</sub>   | HSD2 Switch I/O Signal Swing Voltage (Note 1) | -0.5 |     | 4.5             | V    |

| I <sub>CCSW</sub>  | Maximum HSD Switch Continuous Current         |      |     | 75              | mA   |

| V <sub>CNTRL</sub> | Control Input Voltage (SEL)                   | -0.5 |     | V <sub>DD</sub> | V    |

| T <sub>A</sub>     | Operating Temperature                         | -40  |     | +85             | °C   |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

# Table 5. DC ELECTRICAL CHARACTERISTICS

(Unless otherwise specified: Recommended  $T_A$  and  $T_J$  temperature ranges. All typical values are at  $T_A = 25$ °C and  $V_{DD} = 4.2$  V unless otherwise specified.)

|                  |                           |                     |                                                                           | $T_A = -40 \text{ to } +85^{\circ}\text{C}$<br>$T_J = -40 \text{ to } +125^{\circ}\text{C}$ |     |     |      |

|------------------|---------------------------|---------------------|---------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-----|-----|------|

| Symbol           | Characteristic            | V <sub>DD</sub> (V) | Conditions                                                                | Min                                                                                         | Тур | Max | Unit |

| BASIC OPE        | BASIC OPERATION DEVICE    |                     |                                                                           |                                                                                             |     |     |      |

| I <sub>CC</sub>  | Quiescent Supply Current  | 2.7 to 5.5          | WLCSP: /OE = H & L, I <sub>OUT</sub> = 0                                  |                                                                                             | 10  |     | μΑ   |

| I <sub>OFF</sub> | Power-Off Leakage Current | 0                   | V <sub>SWHSD1</sub> = 0 V to 3.6 V,<br>V <sub>SWHSD2</sub> = 0 V to 4.5 V | -3                                                                                          |     | 3   | μΑ   |

| I <sub>IN</sub>  | Control Input Leakage     | 2.7 to 5.5          | V <sub>CNTRL</sub> = 0 V to V <sub>DD</sub>                               | -2                                                                                          |     | 4   | μΑ   |

<sup>1.</sup> The switch swing voltage is based on the OVP trip level, and when OVP triggers the switch will be disabled to protect the host and no longer in the standard operating condition, once over voltage is removed the device will automatically recover back to normal condition.

# Table 5. DC ELECTRICAL CHARACTERISTICS (continued)

(Unless otherwise specified: Recommended  $T_A$  and  $T_J$  temperature ranges. All typical values are at  $T_A$  = 25°C and  $V_{DD}$  = 4.2 V unless otherwise specified.)

|                          |                                                                    |                     |                                                                  |     | = -40 to +8<br>= -40 to +1 |     |      |

|--------------------------|--------------------------------------------------------------------|---------------------|------------------------------------------------------------------|-----|----------------------------|-----|------|

| Symbol                   | Characteristic                                                     | V <sub>DD</sub> (V) | Conditions                                                       | Min | Тур                        | Max | Unit |

| BASIC OPI                | ERATION DEVICE                                                     |                     |                                                                  |     |                            |     |      |

| I <sub>OZ</sub>          | Off State Leakage                                                  | 2.7 to 5.5          | HSD±≥0 V, HSD1±,<br>HSD2±≤3.6 V                                  | -3  |                            | 5   | μΑ   |

| BASIC OPI                | ERATION HSD SWITCH                                                 |                     |                                                                  |     |                            |     | •    |

| $R_{ON}$                 | HSD Path On Resistance                                             | 2.7 to 5.5          | $I_{OUT} = 8 \text{ mA}, V_{SW} = 0 \text{ V to } 0.4 \text{ V}$ |     | 5                          |     | Ω    |

| $\Delta R_{ON}$          | HSD Path Delta R <sub>ON</sub>                                     | 2.7 to 5.5          | I <sub>OUT</sub> = 8 mA, V <sub>SW</sub> = 0 V to 0.4 V          |     | 0.15                       |     | Ω    |

| V <sub>IH</sub>          | SEL Input Voltage High                                             | 2.7 to 5.5          |                                                                  | 1.3 |                            |     | V    |

| $V_{IM}$                 | SEL Input Voltage Middle<br>(Note 2)                               | 2.7 to 5.5          |                                                                  | 0.8 |                            | 1.0 | V    |

| $V_{IL}$                 | SEL Input Voltage Low                                              | 2.7 to 5.5          |                                                                  |     |                            | 0.5 | V    |

| Zfloat                   | Impedance to VDD or GND detected as a Float including $V_{DD} = 0$ | 2.7 to 5.5          |                                                                  | 2.5 |                            |     | МΩ   |

| V <sub>OV_TRIP1</sub>    | _TRIP1 Input OVP Lockout for HSD1                                  | 2.7 to 5.5          | V <sub>HSD±</sub> Rising, SEL = 0                                | 3.6 | 3.8                        | 4   | V    |

|                          |                                                                    |                     | V <sub>HSD±</sub> Falling, SEL = 0                               | 3.3 | 3.5                        |     |      |

| V <sub>OV_TRIP2</sub>    | Input OVP Lockout for HSD2                                         | 2.7 to 5.5          | V <sub>HSD±</sub> Rising, SEL = 1                                | 4.5 | 4.7                        | 4.9 | ٧    |

|                          |                                                                    |                     | V <sub>HSD±</sub> Falling, SEL = 1                               | 4.2 | 4.4                        |     |      |

| V <sub>OV_HYS</sub>      | Input OVP Hysteresis                                               | 2.7 to 5.5          |                                                                  |     | 0.3                        |     | V    |

| V <sub>NV_TRIP</sub>     | Input Negative Voltage Lockout                                     | 2.7 to 5.5          | V <sub>HSD±</sub> Falling                                        |     | -1.0                       |     | ٧    |

|                          |                                                                    |                     | V <sub>HSD±</sub> Rising                                         |     | -0.7                       |     |      |

| V <sub>NV_HYS</sub>      | Input OVP Hysteresis                                               | 2.7 to 5.5          |                                                                  |     | 0.3                        |     | V    |

| $V_{CL}$                 | Clamping Voltage                                                   | 2.7 to 5.5          | $V_{HSD\pm} \ge V_{OV\_TRIP}$                                    |     | 4.5                        |     | V    |

| V <sub>UVLO</sub> Under- | Under-Voltage Lockout                                              |                     | V <sub>DD</sub> Rising                                           |     | 2.4                        | 2.7 | ٧    |

|                          |                                                                    |                     | V <sub>DD</sub> Falling                                          |     | 2.3                        |     |      |

| TSD                      | Thermal Shutdown (Note 2)                                          |                     | Shutdown Threshold                                               |     | 150                        |     | °C   |

|                          |                                                                    |                     | Return from Shutdown                                             |     | 130                        |     |      |

|                          |                                                                    |                     | Hysteresis                                                       |     | 20                         |     | 1    |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

2. Guaranteed by characterization or Design, not production tested.

# **Table 6. AC ELECTRICAL CHARACTERISTICS**

(Unless otherwise specified: Recommended  $T_A$  and  $T_J$  temperature ranges. All typical values are at  $T_A = 25$ °C and  $V_{DD} = 4.2$  V unless otherwise specified.)

|                    |                                                          |                     |                                                                                                                                                               | $T_A = -40 \text{ to } +85^{\circ}\text{C}$<br>$T_J = -40 \text{ to } +125^{\circ}\text{C}$ |      |     |      |

|--------------------|----------------------------------------------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|------|-----|------|

| Symbol             | Characteristic                                           | V <sub>DD</sub> (V) | Conditions                                                                                                                                                    | Min                                                                                         | Тур  | Max | Unit |

| HSD SWIT           | CH TIMING PARAMETER                                      |                     |                                                                                                                                                               | •                                                                                           |      |     | •    |

| t <sub>OVP</sub>   | OVP Response Time (Note 33)                              | 2.7 to 5.5          | $I_{OUT}$ = 8 mA, $C_L$ = 5 pF, $R_L$ = 50 $\Omega$ , $V_{HSD\pm}$ = 3.3 V to 4.9 V                                                                           |                                                                                             | 0.35 |     | μs   |

| t <sub>ON</sub>    | Turn-On Time, SEL to Output                              | 2.7 to 5.5          | $R_L = 50 \Omega, C_L = 5 pF$                                                                                                                                 |                                                                                             | 0.1  |     | ms   |

| t <sub>OFF</sub>   | Turn-Off Time, SEL to Output                             | 2.7 to 5.5          | $R_L = 50 \Omega, C_L = 5 pF,$<br>$V_{SW} = 0.8 V$                                                                                                            |                                                                                             | 0.2  |     | μs   |

| t <sub>PD</sub>    | Propagation Delay (Note 3)                               | 2.7 to 5.5          | $R_L = 50 \Omega, C_L = 5 pF, V_{SW} = 0.8 V$                                                                                                                 |                                                                                             | 1.3  |     | ns   |

| t <sub>BBM</sub>   | Break-Before-Make (Note 3)                               | 2.7 to 5.5          | $R_L = 50 \Omega, C_L = 5 pF,$<br>$V_{SW1} = V_{SW2} = 0.8 V$                                                                                                 |                                                                                             | 50   |     | μs   |

| t <sub>SK(P)</sub> | Skew of Opposite Transitions of the Same Output (Note 3) | 2.7 to 5.5          | $V_{SW} = 0.2 \text{ Vdiff}_{PP}, R_L = 50 \Omega,$<br>$C_L = 5 \text{ pF}$                                                                                   |                                                                                             | 35   |     | ps   |

| tı                 | Total Jitter (Note 3)                                    | 2.7 to 5.5          | $V_{SW} = 0.2 \text{ Vdiff}_{PP}, R_L = 50 \ \Omega,$ $C_L = 5 \text{ pF}, t_R = t_F = 500 \text{ ps}$ $(10-90\%) \ @ 480 \text{ Mbps}$ $(PRBS = 2^{15} - 1)$ |                                                                                             | 250  |     | ps   |

| HSD± SWI           | TCH CAPACITANCE                                          | •                   |                                                                                                                                                               | •                                                                                           | •    |     |      |

| C <sub>IN</sub>    | Control Pin Input Capacitance (Note 3)                   | 0                   |                                                                                                                                                               |                                                                                             | 1.5  |     | pF   |

| C <sub>ON</sub>    | HSD± On Capacitance (Note 3)                             | 2.7 to 5.5          | SEL = L/H, f = 240 MHz                                                                                                                                        |                                                                                             | 4    |     | 1    |

| C <sub>OFF</sub>   | HSD± Off Capacitance (Note 3)                            | 2.7 to 5.5          | SEL = Float, f = 240 MHz                                                                                                                                      |                                                                                             | 3    |     |      |

| HSD SWIT           | CH BANDWIDTH                                             |                     |                                                                                                                                                               |                                                                                             |      |     |      |

| BW                 | -3dB SDD21 Bandwidth                                     | 2.7 to 5.5          | $R_L = 50 \Omega$ , $C_L = 0 pF$                                                                                                                              |                                                                                             | 1000 |     | MHz  |

|                    | (Note 3)                                                 |                     | $R_L = 50 \Omega$ , $C_L = 5 pF$                                                                                                                              |                                                                                             | 550  |     | MHz  |

| HSD SWIT           | CH AC PARAMETER                                          |                     |                                                                                                                                                               |                                                                                             |      |     |      |

| O <sub>IRR</sub>   | Off Isolation (Note 3)                                   | 2.7 to 5.5          | R <sub>L</sub> = 50 Ω, f = 240 MHz                                                                                                                            |                                                                                             | -35  |     | dB   |

| Xtalk              | Non-Adjacent Channel<br>Crosstalk (Note 3)               | 2.7 to 5.5          | $R_L = 50 \Omega$ , $f = 240 MHz$                                                                                                                             |                                                                                             | -40  |     | dB   |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

3. Guaranteed by characterization or Design, not production tested.

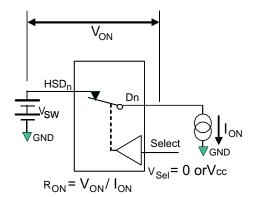

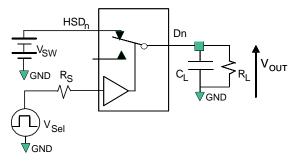

# **TEST DIAGRAMS**

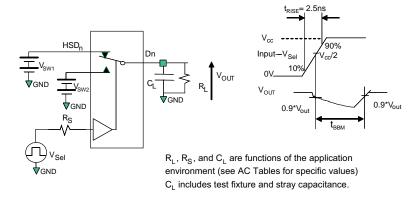

Figure 9. On Resistance

$R_L$ ,  $R_S$ , and  $C_L$  are functions of the application environment (see AC Tables for specific values)  $C_L$  includes test fixture and stray capacitance.

Figure 11. AC Test Circuit Load

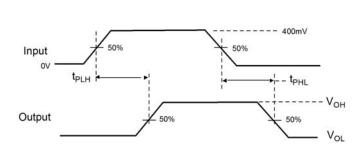

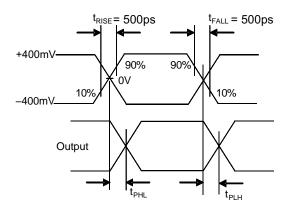

Figure 13. Propagation Delay (t<sub>R</sub>t<sub>F</sub> - 500 ps)

\*\*Each switch port is tested separately

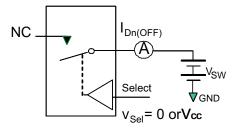

Figure 10. Off Leakage

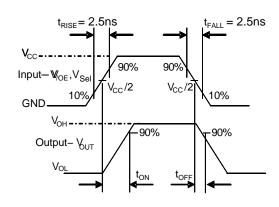

Figure 12. Turn-On / Turn-Off Waveforms

Figure 14. Intra-Pair Skew Test t<sub>SK(P)</sub>

# **TEST DIAGRAMS** (Continued)

Figure 15. Break-Before-Make Interval Timing

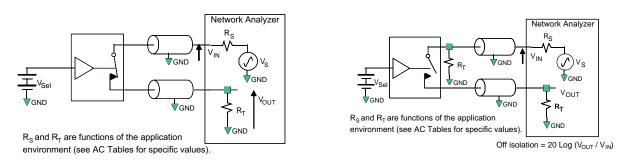

Figure 16. Bandwidth

Figure 17. Channel Off Isolation

Figure 18. Non-Adjacent Channel-to-Channel Crosstalk

# TEST DIAGRAMS (Continued)

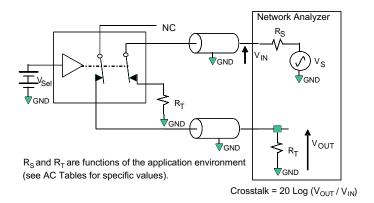

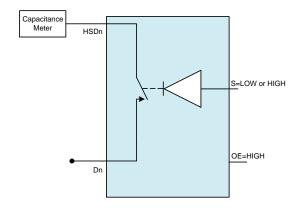

Figure 19. Channel Off Capacitance

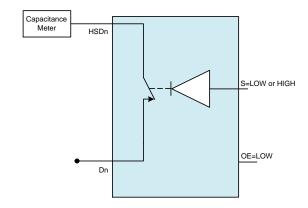

Figure 20. Channel On Capacitance

# **ORDERING INFORMATION**

**Table 7. AVAILABLE PART NUMBERS**

| Part Number | Device Code | Operating Temperature Range | Package                          | Packing Method† |

|-------------|-------------|-----------------------------|----------------------------------|-----------------|

| FSUSB242UCX | MT          | −40 to 85°C                 | 9-Ball WLCSP<br>(1.20 x 1.20 mm) | Tape and Reel   |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

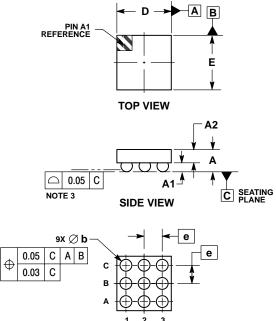

#### PACKAGE DIMENSIONS

# WLCSP9, 1.2x1.2x0.48 CASE 567UL **ISSUE A**

**BOTTOM VIEW**

- NOTES:

1. DIMENSIONING AND TOLERANCING PER

- ASME Y14.5M, 2009. CONTROLLING DIMENSION: MILLIMETERS. COPLANARITY APPLIES TO THE SPHERICAL CROWNS OF THE SOLDER BALLS.

|     | MILLIMETERS |             |       |  |  |  |  |

|-----|-------------|-------------|-------|--|--|--|--|

| DIM | MIN         | MIN NOM MAX |       |  |  |  |  |

| Α   | 0.450       | 0.488       | 0.526 |  |  |  |  |

| A1  | 0.176       | 0.196       | 0.216 |  |  |  |  |

| A2  | 0.274       | 0.292       | 0.310 |  |  |  |  |

| b   | 0.24        | 0.26        | 0.28  |  |  |  |  |

| D   | 1.14        | 1.20        | 1.26  |  |  |  |  |

| Е   | 1.14        | 1.20        | 1.26  |  |  |  |  |

| е   | 0.40 BSC    |             |       |  |  |  |  |

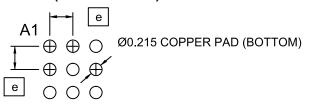

# RECOMMENDED SOLDERING FOOTPRINT\* (NSMD PAD TYPE)

DIMENSIONS: MILLIMETERS

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

ON Semiconductor and III) are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="https://www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.

Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that ON Semiconductor was negligent regarding the design or manufacture of the part. ON Semiconductor is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

# **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910

Japan Customer Focus Center

Phone: 81–3–5817–1050

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative