# Thermoelectric Cooler (TEC) Controller

Data Sheet ADN8831

#### **FEATURES**

Two integrated zero drift, rail-to-rail, chop amplifiers

TEC voltage and current operation monitoring

Programmable TEC maximum voltage and current

Programmable TEC current heating and cooling limits

Configurable PWM switching frequency up to 1 MHz

Power efficiency: > 90%

Temperature lock indication

Optional internal or external clock source

Clock phase adjustment for multiple drop operation

Supports negative temperature coefficient (NTC) thermistors

or positive temperature coefficient (PTC) resistance

thermal detectors (RTDs)

5 V typical and optional 3 V supplies

Standby and shutdown mode availability

Adjustable soft start feature

#### **APPLICATIONS**

5 mm × 5 mm 32-lead LFCSP

Thermoelectric cooler (TEC) temperature control DWDM optical transceiver modules Optical fiber amplifiers Optical networking systems Instruments requiring TEC temperature control

#### **GENERAL DESCRIPTION**

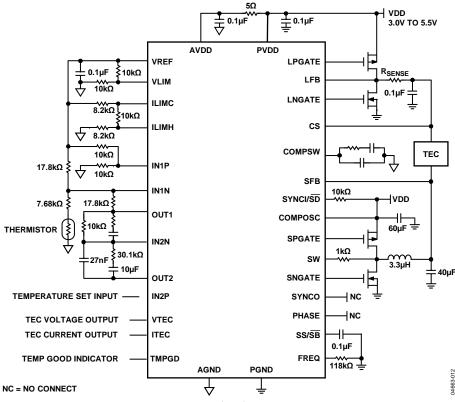

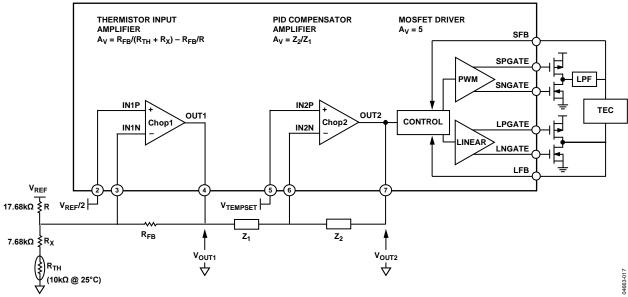

The ADN8831 is a monolithic TEC controller. It has two integrated, zero drift, rail-to-rail comparators, and a PWM driver. A unique PWM driver works with an analog driver to control external selected MOSFETs in an H-bridge. By sensing the thermal detector feedback from the TEC, the ADN8831 can drive a TEC to settle the programmable temperature of a laser diode or a passive component attached to the TEC module.

The ADN8831 supports NTC thermistors or positive temperature coefficient (PTC) RTDs. The target temperature is set as an analog voltage input either from a DAC or from an external resistor divider driven by a reference voltage source.

A proportional integral differential (PID) compensation network helps to quickly and accurately stabilize the ADN8831 thermal control loop. An adjustable PID compensation network example is described in the AN-695 Application Note, *Using the* ADN8831 *TEC Controller Evaluation Board*. A typical reference voltage of 2.5 V is available from the ADN8831 for thermistor temperature sensing or for TEC voltage/current measuring and limiting in both cooling and heating modes.

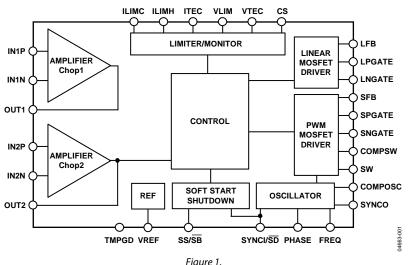

#### **FUNCTIONAL BLOCK DIAGRAM**

# **TABLE OF CONTENTS**

| i catures                                   |

|---------------------------------------------|

| Applications1                               |

| General Description1                        |

| Functional Block Diagram1                   |

| Revision History2                           |

| Detailed Block Diagram3                     |

| Specifications4                             |

| Electrical Characteristics4                 |

| Absolute Maximum Ratings6                   |

| Thermal Characteristics6                    |

| ESD Caution6                                |

| Pin Configuration and Function Descriptions |

| Typical Performance Characteristics9        |

| Theory of Operation11                       |

| Oscillator Clock Frequency                  |

| Oscillator Clock Phase                      |

|                                             |

|   | Temperature Lock Indicator         | 13 |

|---|------------------------------------|----|

|   | Soft Start on Power-Up             | 13 |

|   | Shutdown Mode                      | 13 |

|   | Standby Mode                       | 13 |

|   | TEC Voltage/Current Monitor        | 13 |

|   | Maximum TEC Voltage Limit          | 13 |

|   | Maximum TEC Current Limit          | 14 |

| A | pplications Information            | 15 |

|   | Signal Flow                        | 15 |

|   | Thermistor Setup                   | 15 |

|   | Thermistor Amplifier (Chop1)       | 15 |

|   | PID Compensation Amplifier (Chop2) | 16 |

|   | MOSFET Driver Amplifier            | 17 |

| С | Outline Dimensions                 | 18 |

|   | Ordering Guide                     | 18 |

#### **REVISION HISTORY**

#### 8/12—Rev. 0 to Rev. A

| Changes to Features and General Description Sections         |

|--------------------------------------------------------------|

| Moved Figure 2                                               |

| Changes to Figure 2                                          |

| Changes to Table 14                                          |

| Changes to Table 2 and Table 36                              |

| Changes to Figure 3 and Table 4                              |

| Changes to Theory of Operation Section and Figure 12         |

| Changes to Figure 14 and Figure 1511                         |

| Changes to Oscillator Clock Frequency Section and Oscillator |

| Clock Phase Section                                          |

| Changes to Soft Start on Power-Up Section, Shutdown Mode     |

| Section, Standby Mode Section, and TEC Voltage/Current       |

| Monitor Section                                              |

| Changes to Figure 17                                         |

| Changes to PID Compensation Amplifier (Chop2) Section 16     |

| Changes to MOSFET Driver Amplifier Section and Figure 21 17  |

| Updated Outline Dimensions                                   |

| Changes to Ordering Guide                                    |

| 9/05—Revision 0: Initial Version                             |

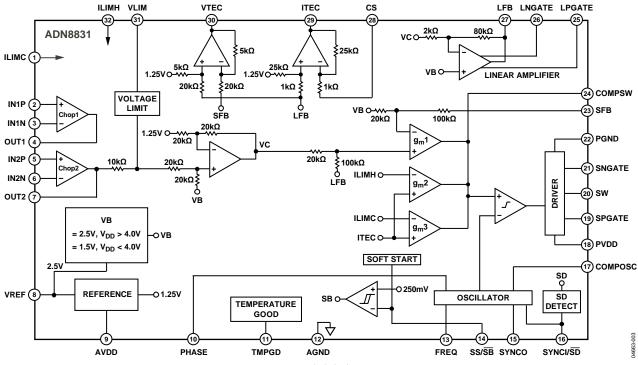

## **DETAILED BLOCK DIAGRAM**

# **SPECIFICATIONS**

## **ELECTRICAL CHARACTERISTICS**

$V_{\rm DD}$  = 3.0 V to 5.0 V,  $T_{\rm A}$  = 25°C, unless otherwise noted.

Table 1.

| Parameter <sup>1</sup>              | Symbol                                | Test Conditions/Comments                                              | Min             | Тур  | Max                         | Unit    |

|-------------------------------------|---------------------------------------|-----------------------------------------------------------------------|-----------------|------|-----------------------------|---------|

| PWM OUTPUT DRIVER                   |                                       |                                                                       |                 |      |                             |         |

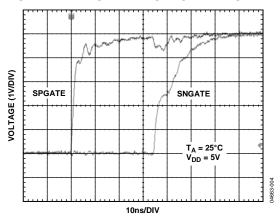

| Output Transition Time              | t <sub>R</sub> , t <sub>F</sub>       | $C_{L} = 3300 \text{ pF}$                                             |                 | 20   |                             | ns      |

| Nonoverlapping Clock Delay          |                                       |                                                                       | 40              | 80   |                             | ns      |

| Output Resistance                   | R <sub>O (SNGATE, SPGATE)</sub>       | $I_L = 10 \text{ mA}, V_{DD} = 3.0 \text{ V}$                         |                 | 6    |                             | Ω       |

| Output Voltage Swing <sup>2</sup>   | SFB                                   | V <sub>LIM</sub> = VREF                                               | 0               |      | $V_{\scriptscriptstyle DD}$ | V       |

| LINEAR OUTPUT AMPLIFIER             |                                       |                                                                       |                 |      |                             |         |

| Output Resistance                   | R <sub>O, LNGATE</sub>                | $I_{OUT} = 2 \text{ mA}, V_{DD} = 3.0 \text{ V}$                      |                 | 200  |                             | Ω       |

|                                     | R <sub>O, LPGATE</sub>                | $I_{OUT} = 2 \text{ mA}, V_{DD} = 3.0 \text{ V}$                      |                 | 100  |                             | Ω       |

| Output Voltage Swing <sup>2</sup>   | LFB                                   |                                                                       | 0               |      | $V_{\scriptscriptstyle DD}$ | V       |

| POWER SUPPLY                        |                                       |                                                                       |                 |      |                             |         |

| Power Supply Voltage                | $V_{DD}$                              |                                                                       | 3.0             |      | 5.5                         | V       |

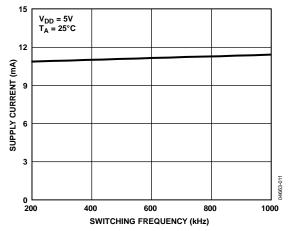

| Supply Current                      | I <sub>SY</sub>                       | PWM not switching                                                     |                 | 8    | 12                          | mA      |

|                                     |                                       | $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +85^{\circ}\text{C}$ |                 |      | 15                          | mA      |

| Shutdown Current                    | I <sub>SD</sub>                       | $SYNCI/\overline{SD} = 0 V$                                           |                 | 8    |                             | μΑ      |

| Soft Start Charging Current         | I <sub>ss</sub>                       | $V_{SS} = 0 V$                                                        |                 | 8    |                             | μΑ      |

| Undervoltage Lockout <sup>3</sup>   | UVLO                                  | Low to high threshold                                                 |                 | 2.2  | 2.6                         | V       |

| Standby Current                     | I <sub>SB</sub>                       | $SYNCI/\overline{SD} = V_{DD}$ , $SS/\overline{SB} = 0 V$             |                 | 2    |                             | mA      |

| Standby Threshold                   | $V_{SB}$                              | $SYNCI/\overline{SD} = V_{DD}$                                        |                 | 150  | 200                         | mV      |

| ERROR/COMPENSATION AMPLIFIERS       |                                       |                                                                       |                 |      |                             |         |

| Input Offset Voltage                | V <sub>OS1</sub>                      | $V_{CM1} = 1.5 \text{ V}, V_{IN1P} - V_{IN1M}$                        |                 | 10   | 100                         | μV      |

|                                     | V <sub>OS2</sub>                      | $V_{CM2} = 1.5 \text{ V}, V_{IN2P} - V_{IN2M}$                        |                 | 10   | 100                         | μV      |

| Input Voltage Range                 | $V_{CM1}, V_{CM2}$                    | CIVIZ IIVZIV                                                          | 0               |      | $V_{\scriptscriptstyle DD}$ | V       |

| Common-Mode Rejection Ratio         | CMRR <sub>1</sub> , CMRR <sub>2</sub> | $V_{CM1}$ , $V_{CM2} = 0.2 \text{ V to } V_{DD} - 0.2 \text{ V}$      |                 | 120  |                             | dB      |

| Output Voltage High                 | V <sub>OH1</sub> , V <sub>OH2</sub>   |                                                                       | $V_{DD} - 0.03$ |      |                             | V       |

| Output Voltage Low                  | $V_{OL1}, V_{OL2}$                    |                                                                       |                 |      | 25                          | mV      |

| Power Supply Rejection Ratio        | PSRR <sub>1</sub> , PSRR <sub>2</sub> | $3.0 \text{ V} \le \text{V}_{DD} \le 5.0 \text{ V}$                   |                 | 110  |                             | dB      |

| Output Current                      | I <sub>OUT1</sub> , I <sub>OUT2</sub> | Sourcing and sinking                                                  | 5               |      |                             | mA      |

| Gain Bandwidth Product              | GBW <sub>1</sub> , GBW <sub>2</sub>   | $V_{OUT} = 0.5 \text{ V to } (V_{DD} - 1 \text{ V})$                  |                 | 2    |                             | MHz     |

| OSCILLATOR                          |                                       |                                                                       |                 |      |                             |         |

| Sync Range                          | f <sub>CLK</sub>                      | SYNCI/SD connected to external                                        | 300             |      | 1000                        | kHz     |

|                                     |                                       | clock                                                                 |                 |      |                             |         |

| Oscillator Frequency                | f <sub>CLK</sub>                      | $COMPOSC = V_{DD}$ , $R_{FREQ} = 118 \text{ k}\Omega$ ,               | 800             | 1000 | 1250                        | kHz     |

|                                     |                                       | $SYNCI/\overline{SD} = V_{DD}, V_{DD} = 5.0 V$                        |                 |      |                             |         |

| Nominal Free-Run Oscillation        | f <sub>CLK-NOMINAL</sub>              | $COMPOSC = V_{DD}, SYNCI/\overline{SD} = V_{DD}$                      | 200             |      | 1000                        | kHz     |

| Frequency                           |                                       |                                                                       |                 |      |                             |         |

| Phase Adjustment Range <sup>2</sup> | $\Phi_{CLK}$                          | $V_{PHASE} = 0.13 \text{ V, } f_{SYNCI/SD} = 1 \text{ MHz}$           |                 |      | 50                          | Degrees |

|                                     |                                       | $V_{PHASE} = 2.3 \text{ V, } f_{SYNCI/SD} = 1 \text{ MHz}$            | 330             |      |                             | Degrees |

| Phase Adjustment Default            | $\Phi_{CLK}$                          | PHASE = open                                                          |                 | 180  |                             | Degrees |

| REFERENCE VOLTAGE                   |                                       |                                                                       |                 |      |                             |         |

| Reference Voltage                   | $V_{REF}$                             | $I_{REF} = 2 \text{ mA}$                                              |                 | 2.35 |                             | V       |

|                                     |                                       | $I_{REF} = 0 \text{ mA}$                                              | 2.37            | 2.47 | 2.57                        | V       |

| Parameter <sup>1</sup>               | Symbol                             | Test Conditions/Comments                             | Min                 | Тур        | Max                 | Unit |

|--------------------------------------|------------------------------------|------------------------------------------------------|---------------------|------------|---------------------|------|

| LOGIC Controls                       |                                    |                                                      |                     |            |                     |      |

| Logic Low Output Voltage             | V <sub>OL</sub>                    | TMPGD, SYNCO, I <sub>OUT</sub> = 0 A                 |                     |            | 0.2                 | V    |

| Logic High Output Voltage            | V <sub>OH</sub>                    | TMPGD, SYNCO, I <sub>OUT</sub> = 0 A                 | $V_{DD} - 0.2$      |            |                     | V    |

| Logic Low Input Voltage              | V <sub>IL</sub>                    |                                                      |                     |            | 0.2                 | V    |

| Logic High Input Voltage             | V <sub>IH</sub>                    |                                                      | 3                   |            |                     | V    |

| Output High Impedance                |                                    | $V_{DD} = 5.0 \text{ V}$                             |                     | 35         |                     | Ω    |

| Output Low Impedance                 |                                    | $V_{DD} = 5.0 \text{ V}$                             |                     | 20         |                     | Ω    |

| Output High Impedance                |                                    | $V_{DD} = 3.0 \text{ V}$                             |                     | 50         |                     | Ω    |

| Output Low Impedance                 |                                    | $V_{DD} = 3.0 \text{ V}$                             |                     | 25         |                     | Ω    |

| TEC CURRENT MEASUREMENT              |                                    |                                                      |                     |            |                     |      |

| ITEC Gain                            | A <sub>V, ITEC</sub>               | $(V_{ITEC} - V_{REE}/2) / (V_{LER} - V_{CS})$        |                     | 25         |                     | V/V  |

| ITEC Output Range High               | V <sub>ITEC, HIGH</sub>            | No load                                              | $V_{DD} - 0.05$     |            |                     | V    |

| ITEC Output Range Low                | V <sub>ITEC, LOW</sub>             |                                                      |                     |            | 0.05                | V    |

| ITEC Input Range <sup>2</sup>        | V <sub>CS</sub> , V <sub>LFB</sub> |                                                      | 0                   |            | $V_{DD}$            | V    |

| ITEC Bias Voltage                    | V <sub>ITEC, B</sub>               | $V_{LFB} = V_{CS} = 0$                               | 1.10                | 1.20       | 1.30                | V    |

| Maximum ITEC Driving Current         | I <sub>OUT, TEC</sub>              |                                                      |                     | ±1.5       |                     | mA   |

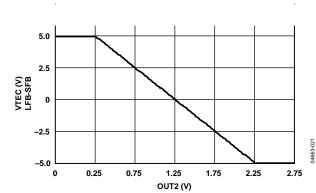

| TEC VOLTAGE MEASUREMENT              | 001,120                            |                                                      |                     |            |                     |      |

| VTEC Gain                            | A <sub>V, VTEC</sub>               | $(V_{VTEC} - V_{REF}/2)/(V_{LFB} - V_{SFB})$         | 0.23                | 0.25       | 0.28                | V/V  |

| VTEC Output Range <sup>2</sup>       | V <sub>VTEC</sub>                  | $V_{DD} = 5.0 \text{ V}$                             | 0.05                |            | 2.5                 | V    |

| VTEC Bias Voltage <sup>2</sup>       | V <sub>VTEC, B</sub>               | $V_{LFB} = V_{SFB} = 0 \text{ V}$                    | 1.20                | 1.25       | 1.35                | V    |

| VTEC Output Load Resistance          | R <sub>VTEC</sub>                  | $I_{VTEC} = 300  \mu A$                              |                     | 35         |                     | Ω    |

| VOLTAGE LIMIT                        |                                    |                                                      |                     |            |                     |      |

| VLIM Gain                            | A <sub>V, LIM</sub>                | $(V_{LFB} - V_{SFB})/V_{VLIM}$                       |                     | 5          |                     | V/V  |

| VLIM Input Range <sup>2</sup>        | V <sub>VLIM</sub>                  |                                                      | 0                   |            | $V_{DD}$            | V    |

| VLIM Input Current, Cooling          | I <sub>VLIM, COOL</sub>            | $V_{OLIT2} < V_{REF}/2$                              |                     |            | 100                 | nA   |

| VLIM Input Current, Heating          | I <sub>VLIM, HEAT</sub>            | $V_{OUT2} > V_{REF}/2$                               |                     | $I_{FREQ}$ |                     | mA   |

| VLIM Input Current Accuracy, Heating | I <sub>VLIM, HEAT</sub>            | I <sub>VLIM</sub> /I <sub>FREQ</sub>                 | 0.8                 | 1.0        | 1.18                | A/A  |

| CURRENT LIMIT                        | VEINY NEXT                         | The They                                             |                     |            |                     |      |

| ILIMC Input Voltage Range            | V <sub>ILIMC</sub>                 |                                                      | V <sub>REF</sub> /2 |            | $V_{DD} - 1$        | V    |

| ILIMH Input Voltage Range            | V <sub>ILIMH</sub>                 |                                                      | 0.1                 |            | V <sub>REF</sub> /2 | V    |

| ILIMC Limit Threshold                | V <sub>TH, ILIMC</sub>             | $V_{ITEC} = 2.0 \text{ V}, R_s = 20 \text{ m}\Omega$ | 1.98                | 2.0        | 2.02                | V    |

| ILIMH Limit Threshold                | V <sub>TH, ILIMH</sub>             | V <sub>ITEC</sub> = 0.5 V                            | 0.48                | 0.5        | 0.52                | V    |

| TEMPERATURE GOOD                     | ,                                  |                                                      |                     |            |                     |      |

| High Threshold                       | V <sub>OUT1,TH1</sub>              | IN2M tied to OUT2, $V_{IN2P} = 1.5 \text{ V}$        |                     | 1.55       | 1.60                | V    |

| Low Threshold                        | V <sub>OUT1,TH2</sub>              | IN2M tied to OUT2, $V_{IN2P} = 1.5 \text{ V}$        | 1.40                | 1.45       |                     | V    |

$<sup>^1</sup>$  Logic inputs meet typical CMOS I/O conditions for source/sink current (~1  $\mu$ A).  $^2$  Guaranteed by design or indirect test methods.  $^3$  The ADN8831 does not work when the supply voltage is less than UVLO.

## **ABSOLUTE MAXIMUM RATINGS**

Absolute maximum ratings at 25°C, unless otherwise noted.

Table 2.

| Parameter                            | Rating               |

|--------------------------------------|----------------------|

| Supply Voltage                       | 6 V                  |

| Input Voltage                        | GND to $V_S + 0.3 V$ |

| Storage Temperature Range            | −65°C to +150°C      |

| Junction Temperature                 | 125°C                |

| Lead Temperature (Soldering, 60 sec) | 300°C                |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### THERMAL CHARACTERISTICS

$\theta_{JA}$  is specified for the worst-case conditions, that is, a device soldered in a circuit board for surface-mount packages.

**Table 3. Thermal Resistance**

| Package Type         | θ <sub>JA</sub> | <b>Ө</b> лс | Unit |

|----------------------|-----------------|-------------|------|

| 32-lead LFCSP (ACPZ) | 33.4            | 1.02        | °C/W |

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

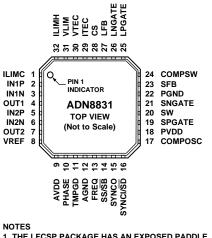

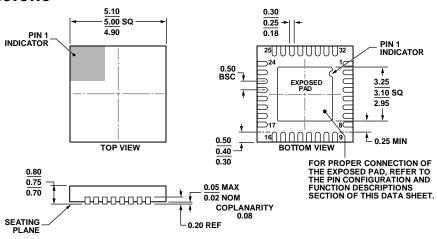

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

<sup>1.</sup> THE LFCSP PACKAGE HAS AN EXPOSED PADDLE

THAT SHOULD BE CONNECTED TO AGND (PIN 12)

AND THE ASSOCIATED PCB GROUND PLANE.

Figure 3. Pin Configuration

**Table 4. Pin Function Descriptions**

| Pin No. | Mnemonic | Туре           | Description                                                                                                                                                    |

|---------|----------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | ILIMC    | Analog Input   | Sets TEC Cooling Current Limit.                                                                                                                                |

| 2       | IN1P     | Analog Input   | Noninverting Input to Error Amplifier.                                                                                                                         |

| 3       | IN1N     | Analog Input   | Inverting Input to Error Amplifier.                                                                                                                            |

| 4       | OUT1     | Analog Output  | Output of Error Amplifier.                                                                                                                                     |

| 5       | IN2P     | Analog Input   | Noninverting Input to Compensation Amplifier.                                                                                                                  |

| 6       | IN2N     | Analog Input   | Inverting Input to Compensation Amplifier.                                                                                                                     |

| 7       | OUT2     | Analog Output  | Output of Compensation Amplifier.                                                                                                                              |

| 8       | VREF     | Analog Output  | 2.5 V Voltage Reference Output.                                                                                                                                |

| 9       | AVDD     | Power          | Power for Nondriver Sections. 3.0 V minimum; 5.5 V maximum.                                                                                                    |

| 10      | PHASE    | Analog Input   | Sets SYNCO Clock Phase Relative to SYNCI/SD Clock.                                                                                                             |

| 11      | TMPGD    | Digital Output | Logic Output. Active high. Indicates when the OUT1 voltage is within ±100 mV of IN2P voltage.                                                                  |

| 12      | AGND     | Ground         | Analog Ground. Connect to low noise ground.                                                                                                                    |

| 13      | FREQ     | Analog Input   | Sets Switching Frequency with an External Resistor.                                                                                                            |

| 14      | SS/SB    | Analog Input   | Sets Soft Start Time for Output Voltage. Pull low (VTEC = 0 V) to put the ADN8831 into standby mode.                                                           |

| 15      | SYNCO    | Digital Output | Phase Adjustment Clock Output. Phase set from PHASE pin. Used to drive SYNCI/SD of other ADN8831 devices.                                                      |

| 16      | SYNCI/SD | Digital Input  | Optional Clock Input. If not connected, clock frequency is set by FREQ pin. Pull low to put the ADN8831 into shutdown mode. Pull high to negate shutdown mode. |

| 17      | COMPOSC  | Analog Output  | Compensation for Oscillator. Connect to PVDD when in free-run mode, connect to R-C network when in external clock mode.                                        |

| 18      | PVDD     | Power          | Power for Output Driver Sections. 3.0 V minimum; 5.5 V maximum.                                                                                                |

| 19      | SPGATE   | Analog Output  | PWM Output Drives External PMOS Gate.                                                                                                                          |

| 20      | SW       | Analog Input   | Connects to PWM FET Drains.                                                                                                                                    |

| 21      | SNGATE   | Analog Output  | PWM Output Drives External NMOS Gate.                                                                                                                          |

| 22      | PGND     | Ground         | Power Ground. External NMOS devices connect to PGND. Connect to digital ground.                                                                                |

| 23      | SFB      | Analog Input   | PWM Feedback. Connect to the TEC module negative (–) terminal.                                                                                                 |

| 24      | COMPSW   | Analog Input   | Compensation Pin for Switching Amplifier.                                                                                                                      |

| 25      | LPGATE   | Analog Output  | Linear Output Drives External PMOS Gate.                                                                                                                       |

| 26      | LNGATE   | Analog Output  | Linear Output Drives External NMOS Gate.                                                                                                                       |

| 27      | LFB      | Analog Input   | Linear Feedback. Connect to H-Bridge transistor output and current sense resistor.                                                                             |

| 28      | CS       | Analog Input   | Linear Feedback. Connect to the TEC module positive (+) terminal.                                                                                              |

| 29      | ITEC     | Analog Output  | Indicates TEC Current.                                                                                                                                         |

| Pin No. | Mnemonic | Туре                | Description                                                                        |

|---------|----------|---------------------|------------------------------------------------------------------------------------|

| 30      | VTEC     | Analog Output       | Indicates TEC Voltage.                                                             |

| 31      | VLIM     | Analog Input        | Sets Maximum Voltage Across TEC Module.                                            |

| 32      | ILIMH    | Analog Input        | Sets TEC Heating Current Limit.                                                    |

| 33      | EP       | Metal paddle at the | Exposed Pad. The LFCSP package has an exposed pad that should be connected to AGND |

|         |          | back of package     | (Pin 12) and the associated PCB ground plate.                                      |

# TYPICAL PERFORMANCE CHARACTERISTICS

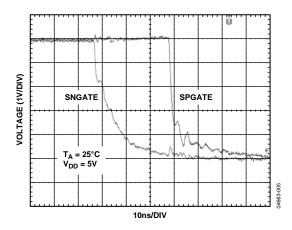

Figure 4. SPGATE and SNGATE Rise Time Using Circuit Shown Figure 12

Figure 5. SNGATE and SPGATE Fall Time Using Circuit Shown in Figure 12

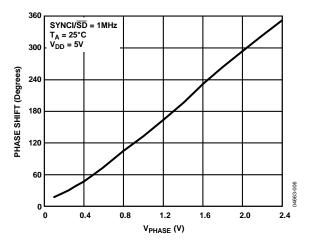

Figure 6. Clock Phase Shift vs. Phase Voltage

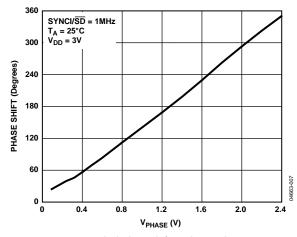

Figure 7. Clock Phase Shift vs. Phase Voltage

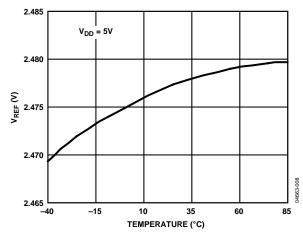

Figure 8. V<sub>REF</sub> vs. Temperature

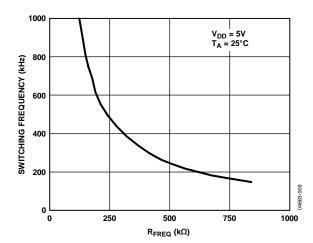

Figure 9. Switching Frequency vs.  $R_{FREQ}$

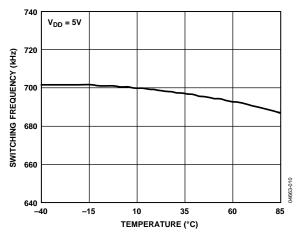

Figure 10. Switching Frequency vs. Temperature

Figure 11. Supply Current vs. Switching Frequency

### THEORY OF OPERATION

The ADN8831 is a single chip TEC controller that sets and stabilizes a TEC temperature. A voltage applied to the input of the ADN8831 corresponds to a target TEC temperature setpoint (TEMPSET). By controlling an external FET H-bridge, the appropriate current is then applied to the TEC to pump heat either to or away from an object attached to the TEC. The objective temperature is measured with a thermal sensor attached to the TEC and the sensed temperature (voltage) is fed back to the ADN8831 to complete a closed thermal control loop of the TEC. For best stability, the thermal sensor is to be closed to the object. In most laser diode modules, a TEC and a NTC thermistor are already mounted in the same package to regulate the laser diode temperature.

The ADN8831 integrates two self-correcting, auto-zero amplifiers (Chop1 and Chop2). The Chop1 amplifier usually takes a thermal sensor input and converts or regulates the input to a linear voltage output. The OUT1 (Pin 4) voltage is proportional to the object temperature. The OUT1 (Pin 4) voltage is fed into the compensation amplifier (Chop2) and compared with a temperature setpoint voltage, creating an error voltage that is proportional to the difference. When using the Chop2 amplifier, a PID network is recommended, as shown in Figure 12.

Adjusting the PID network optimizes the step response of the TEC control loop. A compromised settling time and the maximum current ringing become available when this is done. Details of how to adjust the compensation network are in the PID Compensation Amplifier (CHOP2) section. The TEC is differentially driven in an H-bridge configuration. The ADN8831 drives external MOSFET transistors to provide the TEC current. To further improve the power efficiency of the system, one side of the H-bridge uses a PWM driver. Only one inductor and one capacitor are required to filter out the switching frequency. The other side of the H-bridge uses linear output without requiring any additional circuitry. This proprietary configuration allows the ADN8831 to provide efficiency of >90%. For most applications, a 4.7 µH inductor, a 22 µF capacitor, and a switching frequency of 1 MHz, maintain less than 0.5% worst-case output voltage ripple across a TEC.

The maximum voltage across the TEC and current flowing through the TEC is to be set using the VLIM (Pin 31) and ILIMC (Pin 1)/ILIMH (Pin 32). Additional details are in the Maximum TEC Voltage Limit section and the Maximum TEC Current Limit section.

Figure 12. Typical Application Circuit 1

#### **OSCILLATOR CLOCK FREQUENCY**

The ADN8831 has an internal oscillator to generate the switching frequency for the output stage. This oscillator can be set in either free-run mode or synchronized to an external clock signal.

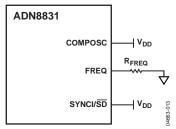

#### Free-Run Operation

The switching frequency is set by a single resistor connected from FREQ (Pin 13) to ground. Table 5 shows  $R_{FREQ}$  for some common switching frequencies. For free-run operation, connect SYNCI/ $\overline{SD}$  (Pin 16) and COMPOSC (Pin 17) to PVDD (Pin 18).

Table 5. Switching Frequencies vs.  $R_{FREO}$

| <b>f</b> <sub>switch</sub> | R <sub>FREQ</sub> |

|----------------------------|-------------------|

| 250 kHz                    | 484 kΩ            |

| 500 kHz                    | 249 kΩ            |

| 750 kHz                    | 168 kΩ            |

| 1 MHz                      | 118 kΩ            |

Higher switching frequencies reduce the voltage ripple across the TEC. However, high switching frequencies create more power dissipation in the external transistors due to the more frequent charging and discharging of the transistor gate capacitances.

Figure 13. Free-Run Mode

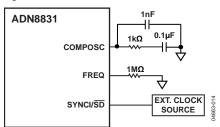

#### **External Clock Operation**

The switching frequency of the ADN8831 can be synchronized with an external clock. Connect the clock signal to SYNCI/SD (Pin 16) and connect COMPOSC (Pin 17) to an R-C network. This network compensates a PLL to lock on to the external clock.

Figure 14. Synchronize to an External Clock

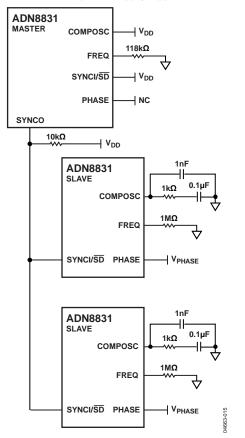

#### **Connecting Multiple ADN8831 Devices**

Connecting SYNCO (Pin 15) to the SYNCI/SD pin of another ADN8831 allows for multiple ADN8831 devices to work together using a single clock. Multiple ADN8831 devices can be driven from a single master ADN8831 device, by connecting the SYNCO pin of the master device to each slave SYNCI/SD pin, or by daisy-chaining by connecting the SYNCO pin of each device to the SYNCI/SD pin of the next device. When multiple ADN8831 devices are clocked at the same frequency, the phase is to be adjusted to reduce power supply ripple.

Figure 15. Multiple ADN8831 Devices Driven from a Master Clock

#### **OSCILLATOR CLOCK PHASE**

Adjust the oscillator clock phase using a simple resistor divider at PHASE (Pin 10). Phase adjustment allows two or more ADN8831 devices to operate from the same clock frequency and not have all outputs switched simultaneously. This avoids the potential of an excessive power supply ripple.

To ensure the correct operation of the oscillator,  $V_{PHASE}$  is to remain in the range of 100 mV to 2.4 V. PHASE (Pin 10) is internally biased at 1.2 V. If PHASE (Pin 10) remains open, the clock phase is set at 180° as the default.

#### TEMPERATURE LOCK INDICATOR

The TMPGD (Pin 11) outputs a logic high when the OUT1 (Pin 4) voltage reaches the IN2P (Pin 5) temperature setpoint (TEMPSET) voltage. The TMPGD has a detection range of  $\pm 25$  mV and a 10 mV typical hysteresis. This allows direct interfacing either to the microcontrollers or to the supervisory circuitry.

#### **SOFT START ON POWER-UP**

The ADN8831 can be programmed to ramp up for a specified time after the power supply is turned on or after the  $\overline{SD}$  pin is deasserted. This feature, called soft start, is useful for gradually increasing the duty cycle of the PWM amplifier. The soft start time is set with a single capacitor connected from SS (Pin 14) to ground. The capacitor value is calculated by the following equation:

$$\tau_{SS} = 150 \times C_{SS}$$

where:

$C_{SS}$  is the value of the capacitor in microfarads.  $\tau_{SS}$  is the soft start time in milliseconds.

To set a soft start time of 15 ms,  $C_{ss}$  is to equal 0.1  $\mu F$ .

#### **SHUTDOWN MODE**

The shutdown mode sets the ADN8831 into an ultralow current state. The current draw in shutdown mode is typically 8  $\mu A$ . The shutdown input,  $\overline{SD}$  (Pin 16), is active low. To shut down the device, drive  $\overline{SD}$  to logic low. Once a logic high is applied, the ADN8331 is reactivated after the time delay set by the soft start circuitry. Refer to the Soft Start on Power-Up section for more details.

#### **STANDBY MODE**

The ADN8831 has a standby mode that deactivates a MOSFET driver stage. The current draw for the ADN8831 in standby mode is less than 2 mA. The standby input SS/SB (Pin 14) is active low. After applying a logic high, the ADN8331 reactivates following the delay. In standby mode, only SYNCO (Pin 15) has a clock output. All the other function blocks are powered off.

#### **TEC VOLTAGE/CURRENT MONITOR**

The TEC real time voltage and current are detectable at VTEC (Pin 30) and ITEC (Pin 29), respectively.

#### **Voltage Monitor**

VTEC (Pin 30) is an analog voltage output pin with a voltage proportional to the actual voltage across the TEC. A center VTEC voltage of 1.25 V corresponds to 0 V across a TEC. The output voltage is calculated using the following equation:

$$V_{VTEC} = 1.25 \text{ V} + 0.25 \times (V_{LFB} - V_{SEB})$$

#### **Current Monitor**

ITEC (Pin 29) is an analog voltage output pin with a voltage proportional to the actual current through the TEC. A center ITEC voltage of 1.25 V corresponds to 0 A through the TEC. The output voltage is calculated using the following equation:

$$V_{ITEC} = 1.25 \text{ V} + 25 \times (V_{LFB} - V_{CS})$$

The equivalent TEC current is calculated using the following equation:

$$I_{TEC} = \frac{V_{ITEC} - 1.25 \text{ V}}{25 \times R_{SENISE}}$$

#### **MAXIMUM TEC VOLTAGE LIMIT**

The maximum TEC voltage is set by applying a voltage at VLIM (Pin 31) to protect the TEC. This voltage can be set with a resistor divider or a DAC. The voltage limiter operates in bidirectional TEC voltage, and cooling and heating voltage.

#### **Using a DAC**

Both the cooling and heating voltage limits are set at the same levels when a voltage source directly drives VLIM (Pin 31). The maximum TEC voltage is calculated using the following equation:

$$V_{TEC(MAX)} = 5 \times V_{VLIM}$$

where

$V_{\it TEC\,(MAX)}$  is the maximum TEC voltage.  $V_{\it VLIM}$  is the voltage applied at VLIM (Pin 31).

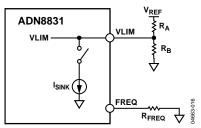

#### **Using a Resistor Divider**

Separate voltage limits are set using a resistor divider. The internal current sink circuitry connected to VLIM (Pin 31) draws a current when the ADN8831 drives the TEC in a heating direction, which lowers the voltage at VLIM (Pin 31). The current sink is not active when the TEC is driven in a cooling direction; therefore, the TEC heating voltage limit is always lower than the cooling voltage limit.

Figure 16. Using a Resistor Divider

The sink current is set by the resistor connected from FREQ (Pin 13) to ground. The sink current is calculated using the following equation:

$$I_{SINK} = \frac{1.25 \text{ V}}{R_{FREO}}$$

where:

$I_{SINC}$  is the sink current at VLIM (Pin 31).

$R_{FREQ}$  is the resistor connected at FREQ (Pin 13).

The cooling and heating limits are calculated using the following equations:

$$V_{VLIM,COOL} = \frac{V_{REF} \times R_B}{R_A + R_B}$$

$$V_{VLIM,HEAT} = V_{VLIM,COOL} - I_{SINK} \times R_A \left\| R_B \right\|$$

#### **MAXIMUM TEC CURRENT LIMIT**

To protect the TEC, separate maximum TEC current limits in cooling and heating directions are set by applying a voltage at ILIMC (Pin 1) and ILIMH (Pin 32). Maximum TEC currents are calculated using the following equations:

$$I_{TEC,MAX,COOL} = \frac{V_{ILIMC} - 1.25 \text{ V}}{25 \times R_{SENSE}}$$

$$I_{TEC,MAX,HEAT} = \frac{1.25 \text{ V} - V_{ILIMH}}{25 \times R_{SENSE}}$$

## APPLICATIONS INFORMATION

Figure 17. Signal Flow Block Diagram

#### **SIGNAL FLOW**

The ADN8831 integrates two auto-zero amplifiers defined as the Chop1 amplifier and the Chop2 amplifier. Both of the amplifiers can be used as standalone amplifiers, therefore, the implementation of temperature control can vary. Figure 17 shows the signal flow through the ADN8831, and a typical implementation of the temperature control loop using the Chop1 amplifier and the Chop2 amplifier.

In Figure 17, the Chop1 amplifier and the Chop2 amplifier are configured as the thermistor input amplifier and the PID compensation amplifier, respectively. The thermistor input amplifier gains the thermistor voltage then outputs to the PID compensation amplifier. The PID compensation amplifier then compensates a loop response over the frequency domain.

The output from the compensation loop at OUT2 is fed to the linear MOSFET gate driver. The voltage at LFB is fed with OUT2 into the PWM MOSFET gate driver. Including the external transistors, the gain of the differential output section is fixed at 5. For details on the output drivers, see the MOSFET Driver Amplifier section.

#### THERMISTOR SETUP

The thermistor has a nonlinear relationship to temperature; near optimal linearity over a specified temperature range can be achieved with the proper value of  $R_{\rm x}$  placed in series with the thermistor. First, the resistance of the thermistor must be known, where

$$\begin{split} R_{LOW} &= R_{TH} @ T_{LOW} \\ R_{MID} &= R_{TH} @ T_{MID} \\ R_{HIGH} &= R_{TH} @ T_{HIGH} \end{split}$$

$T_{LOW}$  and  $T_{HIGH}$  are the endpoints of the temperature range and  $T_{MID}$  is the average. In some cases, with only B constant available, R<sub>TH</sub> is calculated using the following equation:

$$R_{TH} = R_R \exp \left\{ B \left( \frac{1}{T} - \frac{1}{T_R} \right) \right\}$$

where:

$R_{TH}$  is a resistance at T[K].

$R_R$  is a resistance at  $T_R[K]$ .

R<sub>v</sub> is calculated using the following equation:

$$R_{X} = \left(\frac{R_{LOW}R_{MID} + R_{MID}R_{HIGH} - 2R_{LOW}R_{HIGH}}{R_{LOW} + R_{HIGH} - 2R_{MID}}\right)$$

#### THERMISTOR AMPLIFIER (Chop1)

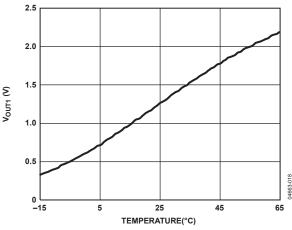

The Chop1 amplifier can be used as a thermistor input amplifier. In Figure 17, the output voltage is a function of the thermistor temperature. The voltage at OUT1 is expressed as

$$V_{OUT1} = \left(\frac{R_{FB}}{R_{TH} + R_{Y}} - \frac{R_{FB}}{R} + 1\right) \times \frac{V_{REF}}{2}$$

where

$R_{TH}$  is a thermistor.

$R_X$  is a compensation resistor.

R is calculated using the following equation:

$$R = R_X + R_{TH @ 25^{\circ}C}$$

$V_{\rm OUT1}$  is centered around  $V_{\rm REF}/2$  at 25°C. With the typical values shown in Figure 17, an average temperature-to-voltage coefficient is  $-25~{\rm mV/^\circ C}$  at a range of  $+5^{\circ}{\rm C}$  to  $+45^{\circ}{\rm C}$ .

Figure 18. V<sub>OUT1</sub> vs. Temperature

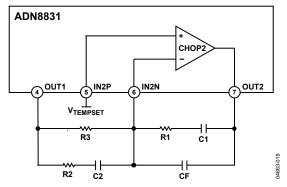

#### PID COMPENSATION AMPLIFIER (Chop2)

Use the Chop2 amplifier as the PID compensation amplifier. The voltage at OUT1 feeds into the PID compensation amplifier. The frequency response of the PID compensation amplifier is dictated by the compensation network. Apply the temperature set voltage at IN2P. In Figure 17, the voltage at OUT2 is calculated using the following equation:

$$V_{OUT2} = V_{TEMPSET} - \frac{Z2}{Z1}(V_{OUT1} - V_{TEMPSET})$$

The user sets the exact compensation network. This network varies from a simple integrator to PI, PID, or any other type of network. The user also determines the type of compensation and component values because they are dependent on the thermal response of the object and the TEC. One method for empirically determining these values is to input a step function to IN2P, therefore changing the target temperature, and adjusting the compensation network to minimize the settling time of the TEC temperature.

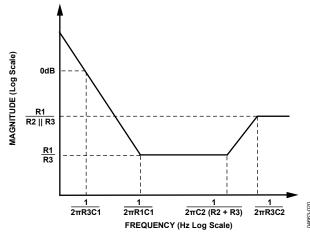

A typical compensation network for temperature control of a laser module is a PID loop consisting of a very low frequency pole and two separate zeros at higher frequencies. Figure 19 shows a simple network for implementing PID compensation. To reduce the noise sensitivity of the control loop, an additional pole is added at a higher frequency than the zeros. The bode plot of the magnitude is shown in Figure 20. The unity-gain crossover frequency of the feedforward amplifier is calculated using the following equation:

$$f_{0\,\text{dB}} = \frac{1}{2\pi R3C1} \times 80 \times TECGAIN$$

To ensure stability, the unity-gain crossover frequency is to be lower than the thermal time constant of the TEC and thermistor. However, this thermal time constant is sometimes unspecified making it difficult to characterize. There are many texts written on loop stabilization, and it is beyond the scope of this data sheet to discuss all methods and trade offs in optimizing compensation networks.

Figure 19. Implementing a PID Compensation Loop

Figure 20. Bode Plot for PID Compensation

With an ADN8831-EVALZ board, AN-695, an application note shows how to determine the PID network components for a stable TEC subsystem performance.

#### **MOSFET DRIVER AMPLIFIER**

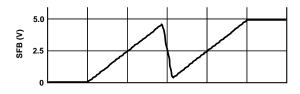

The ADN8831 has two separate MOSFET drivers: a switched output or pulse-width modulated (PWM) amplifier, and a high gain linear amplifier. Each amplifier has a pair of outputs that drive the gates of external MOSFETs which, in turn, drive the TEC as shown in Figure 17. A voltage across the TEC is monitored via SFB (Pin 23) and LFB (Pin 27). Although both MOSFET drivers achieve the same result, to provide constant voltage and high current, their operation is different. The exact equations for the two outputs are

$$V_{LFB} = V_B - 40(V_{OUT2} - 1.25)$$

$$V_{SFB} = V_{LFB} + 5(V_{OUT2} - 1.25)$$

where:

$V_{{\rm OUT2}}$  is the voltage at OUT2 (Pin 7).

$V_{\rm \it B}$  is determined by  $V_{\rm \tiny DD}$  as

$$V_B = 1.5 \text{ V}[V_{DD} < 4.0 \text{ V}]$$

$$V_B = 2.5 \text{ V}[V_{DD} > 4.0 \text{ V}]$$

The voltage at OUT2 (Pin 7) is determined by the compensation network that receives temperature set voltage and thermistor voltage fed by the input amplifier.  $V_{\rm LFB}$  has a low limit of 0 V and an upper limit of  $V_{\rm DD}$ . Figure 21 shows the graphs of these equations.

Figure 21. OUT2 Voltage vs. TEC Voltage

## **OUTLINE DIMENSIONS**

COMPLIANT TO JEDEC STANDARDS MO-220-WHHD.

Figure 22. 32-Lead Lead Frame Chip Scale Package [LFCSP\_VQ] 5 mm× 5 mm Body, Very Thin Quad (CP-32-7) Dimensions Shown in Millimeters

#### **ORDERING GUIDE**

| Model <sup>1</sup> | Temperature Range | Package Description                              | Package Option |

|--------------------|-------------------|--------------------------------------------------|----------------|

| ADN8831ACPZ-R2     | −40°C to +85°C    | 32-Lead Lead Frame Chip Scale Package [LFCSP_VQ] | CP-32-7        |

| ADN8831ACPZ-REEL7  | −40°C to +85°C    | 32-Lead Lead Frame Chip Scale Package [LFCSP_VQ] | CP-32-7        |

| ADN8831-EVALZ      | −40°C to +85°C    | Evaluation Board                                 |                |

$<sup>^{1}</sup>$  Z = RoHS Compliant Part.

# **NOTES**

**NOTES**