# SigmaDSP 28-/56-Bit Audio Processor with Two ADCs and Four DACs

**ADAU1401**

#### **FEATURES**

28-/56-bit, 50 MIPS digital audio processor

2 ADCs: SNR of 100 dB, THD + N of −83 dB

4 DACs: SNR of 104 dB, THD + N of −90 dB

Complete standalone operation

Self-boot from serial EEPROM

Auxiliary ADC with 4-input mux for analog control

GPIOs for digital controls and outputs

Fully programmable with SigmaStudio graphical tool

28-bit × 28-bit multiplier with 56-bit accumulator for full

double-precision processing

Clock oscillator for generating master clock from crystal

PLL for generating master clock from 64 × f₅, 256 × f₅,

384 × f₅, or 512 × f₅ clocks

Flexible serial data input/output ports with I<sup>2</sup>S-compatible, left-justified, right-justified, and TDM modes

Sampling rates of up to 192 kHz supported

On-chip voltage regulator for compatibility with 3.3 V systems

48-lead, plastic LQFP

#### **APPLICATIONS**

Multimedia speaker systems

MP3 player speaker docks

Automotive head units

Minicomponent stereos

Digital televisions

Studio monitors

Speaker crossovers

Musical instrument effects processors

In-seat sound systems (aircraft/motor coaches)

#### **GENERAL DESCRIPTION**

The ADAU1401 is a complete single-chip audio system with a 28-/56-bit audio DSP, ADCs, DACs, and microcontroller-like control interfaces. Signal processing includes equalization, crossover, bass enhancement, multiband dynamics processing, delay compensation, speaker compensation, and stereo image widening. This processing can be used to compensate for real-world limitations of speakers, amplifiers, and listening environments, providing dramatic improvements in perceived audio quality.

Its signal processing is comparable to that found in high end studio equipment. Most processing is done in full 56-bit, double-precision mode, resulting in very good low level signal performance. The ADAU1401 is a fully programmable DSP. The easy to use SigmaStudio™ software allows the user to graphically configure a custom signal processing flow using blocks such as biquad filters, dynamics processors, level controls, and GPIO interface controls.

ADAU1401 programs can be loaded on power-up either from a serial EEPROM through its own self-boot mechanism or from an external microcontroller. On power-down, the current state of the parameters can be written back to the EEPROM from the ADAU1401 to be recalled the next time the program is run.

Two  $\Sigma$ - $\Delta$  ADCs and four  $\Sigma$ - $\Delta$  DACs provide a 98.5 dB analog input to analog output dynamic. Each ADC has a THD + N of –83 dB, and each DAC has a THD + N of –90 dB. Digital input and output ports allow a glueless connection to additional ADCs and DACs. The ADAU1401 communicates through an  $I^2C^*$  bus or a 4-wire SPI port.

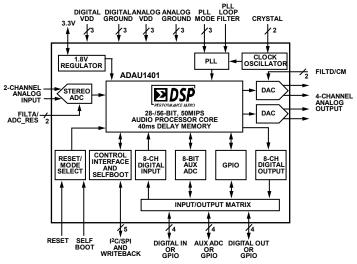

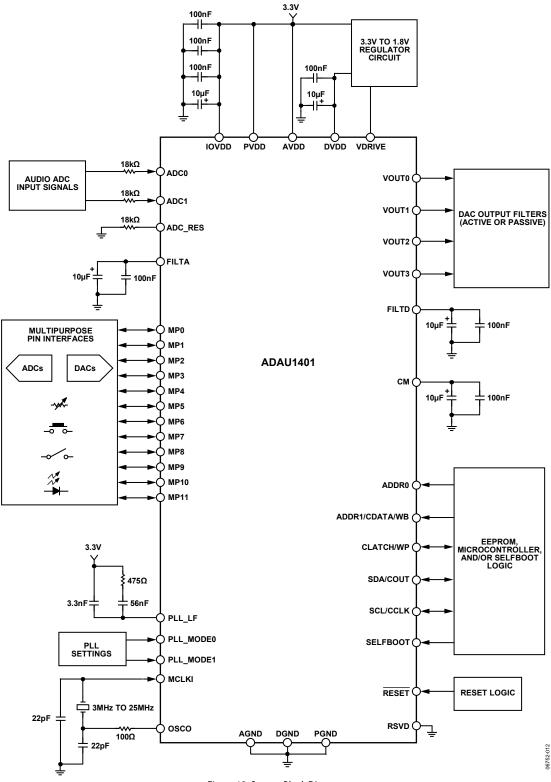

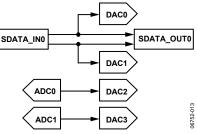

### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

# **TABLE OF CONTENTS**

| Features                                        | . 1 |

|-------------------------------------------------|-----|

| Applications                                    | . 1 |

| General Description                             | . 1 |

| Functional Block Diagram                        | . 1 |

| Revision History                                | 2   |

| Specifications                                  | 3   |

| Analog Performance                              | 3   |

| Digital Input/Output                            | . 4 |

| Power                                           | . 5 |

| Temperature Range                               | 5   |

| PLL and Oscillator                              | 5   |

| Regulator                                       | 5   |

| Digital Timing Specifications                   | . 6 |

| Digital Timing Diagrams                         | 7   |

| Absolute Maximum Ratings                        | . 9 |

| Thermal Resistance                              | . 9 |

| ESD Caution                                     | . 9 |

| Pin Configuration and Function Descriptions     | 10  |

| Typical Performance Characteristics             | 13  |

| System Block Diagram                            | 14  |

| Overview                                        | 15  |

| Initialization                                  | 16  |

| Power-Up Sequence                               | 16  |

| Control Registers Setup                         | 16  |

| Recommended Program/Parameter Loading Procedure | 16  |

| Power-Reduction Modes                           | 16  |

| Using the Oscillator                            | 17  |

| Setting Master Clock/PLL Mode                   | 17  |

| Voltage Regulator                               | 18  |

| Audio ADCs                                      | 19  |

| Audio DACs                                      | 20  |

| Control Ports                                   | 21  |

| I <sup>2</sup> C Port                           | 22  |

| SPI Port                                        | 25  |

| Self-Boot                                       | 26  |

| Signal Processing                               | 28  |

| Numeric Formats                                 | 28  |

| Programming                                     | 28  |

|                                                 |     |

| RAIVIS and Registers                                                     | 27 |

|--------------------------------------------------------------------------|----|

| Address Maps                                                             | 29 |

| Parameter RAM                                                            | 29 |

| Data RAM                                                                 | 29 |

| Read/Write Data Formats                                                  | 29 |

| Control Register Map                                                     | 31 |

| Control Register Details                                                 | 33 |

| 2048 to 2055 (0x0800 to 0x0807)—Interface Registers                      | 33 |

| 2056 (0x808)—GPIO Pin Setting Register                                   | 34 |

| 2057 to 2060 (0x809 to 0x80C)—Auxiliary ADC Data Registers               | 35 |

| 2064 to 2068 (0x0810 to 0x814)—Safeload Data Registers                   | 36 |

| 2069 to 2073 (0x0815 to 0x819) Safeload Address Registers                | 36 |

| 2074 to 2075 (0x081A to 0x081B)—Data Capture Registers                   | 37 |

| 2076 (0x081C)—DSP Core Control Register                                  | 38 |

| 2078 (0x081E)—Serial Output Control Register                             | 39 |

| 2079 (0x081F)—Serial Input Control Register                              | 40 |

| 2080 to 2081 (0x0820 to 0x0821)—Multipurpose Pin Configuration Registers | 41 |

| 2082 (0x0822)—Auxiliary ADC and Power Control                            |    |

| 2084 (0x0824)—Auxiliary ADC Enable                                       | 42 |

| 2086 (0x0826)—Oscillator Power-Down                                      | 42 |

| 2087 (0x0827)—DAC Setup                                                  | 43 |

| Multipurpose Pins                                                        | 44 |

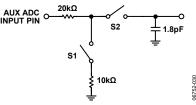

| Auxiliary ADC                                                            | 44 |

| General-Purpose Input/Output Pins                                        |    |

| Serial Data Input/Output Ports                                           | 44 |

| Layout Recommendations                                                   | 47 |

| Parts Placement                                                          | 47 |

| Grounding                                                                | 47 |

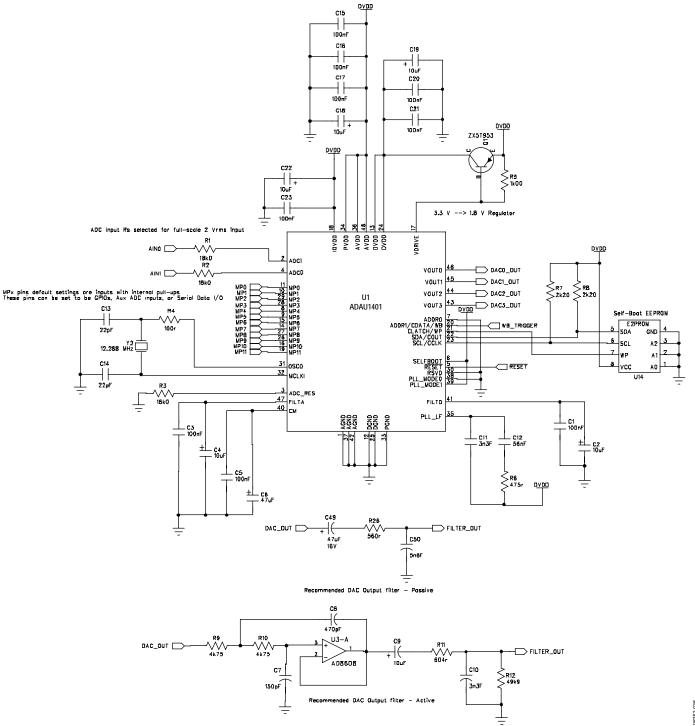

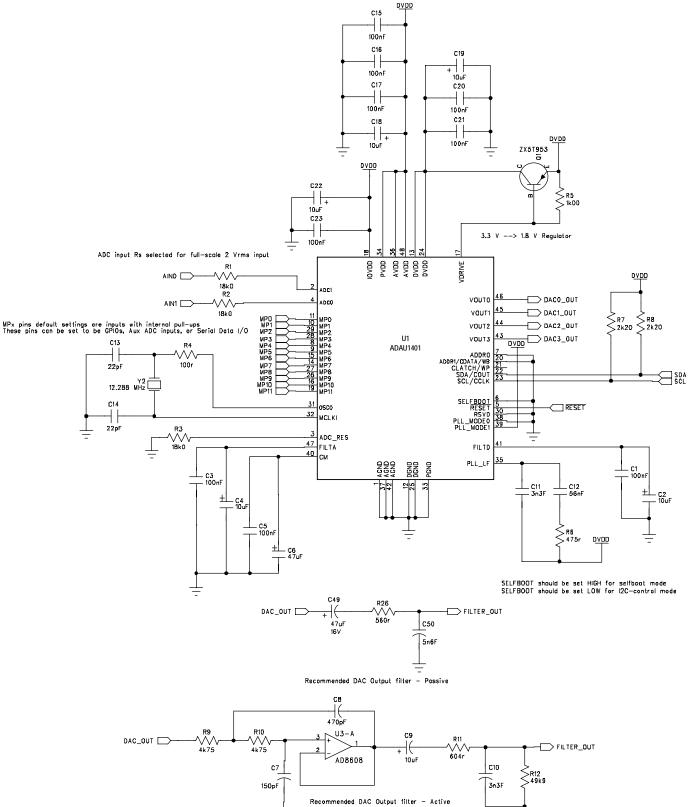

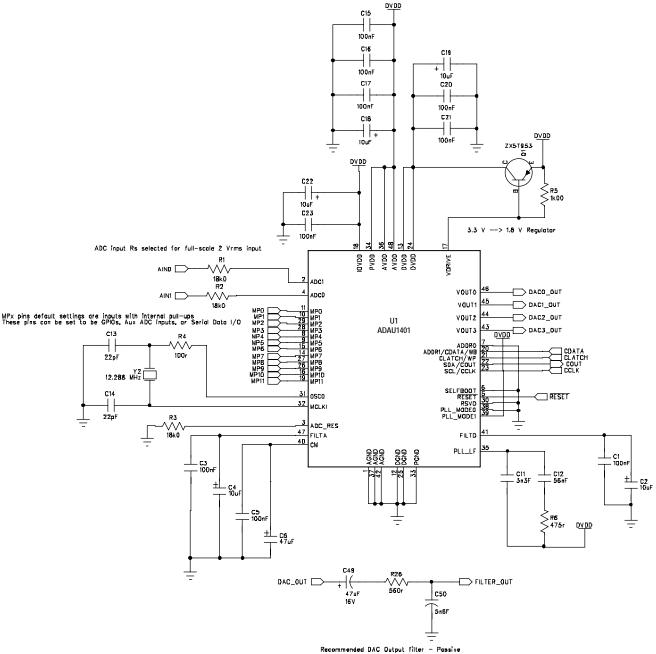

| Typical Application Schematics                                           | 48 |

| Self-Boot Mode                                                           | 48 |

| I <sup>2</sup> C Control                                                 | 49 |

| SPI Control                                                              | 50 |

| Outline Dimensions                                                       | 51 |

| Ordering Guide                                                           | 51 |

### **REVISION HISTORY**

# **SPECIFICATIONS**

AVDD = 3.3 V, DVDD = 1.8 V, PVDD = 3.3 V, IOVDD = 3.3 V, master clock input = 12.288 MHz, unless otherwise noted.

### **ANALOG PERFORMANCE**

Specifications are guaranteed at 25°C (ambient).

Table 1.

| Parameter                         | Min  | Тур       | Max | Unit                       | Test Conditions/Comments                                                                                     |

|-----------------------------------|------|-----------|-----|----------------------------|--------------------------------------------------------------------------------------------------------------|

| ADC INPUTS                        |      |           |     |                            |                                                                                                              |

| Number of Channels                |      | 2         |     |                            | Stereo input                                                                                                 |

| Resolution                        |      | 24        |     | Bits                       |                                                                                                              |

| Full-Scale Input                  |      | 100 (283) |     | μA <sub>rms</sub> (μΑ p-p) | $2 V_{rms}$ input with $20 \text{ k}\Omega$ (18 k $\Omega$ external + 2 k $\Omega$ internal) series resistor |

| Signal-to-Noise Ratio             |      |           |     |                            |                                                                                                              |

| A-Weighted                        |      | 100       |     | dB                         |                                                                                                              |

| Dynamic Range                     |      |           |     |                            | -60 dB with respect to full-scale analog input                                                               |

| A-Weighted                        | 95   | 100       |     | dB                         |                                                                                                              |

| Total Harmonic Distortion + Noise |      | -83       |     | dB                         | -3 dB with respect to full-scale analog input                                                                |

| Interchannel Gain Mismatch        |      | 25        | 250 | mdB                        |                                                                                                              |

| Crosstalk                         |      | -82       |     | dB                         | Analog channel-to-channel crosstalk                                                                          |

| DC Bias                           | 1.4  | 1.5       | 1.6 | V                          |                                                                                                              |

| Gain Error                        | -11  |           | +11 | %                          |                                                                                                              |

| DAC OUTPUTS                       |      |           |     |                            |                                                                                                              |

| Number of Channels                |      | 4         |     |                            | Two stereo output channels                                                                                   |

| Resolution                        |      | 24        |     | Bits                       |                                                                                                              |

| Full-Scale Analog Output          |      | 0.9 (2.5) |     | V <sub>rms</sub> (V p-p)   |                                                                                                              |

| Signal-to-Noise Ratio             |      |           |     |                            |                                                                                                              |

| A-Weighted                        |      | 104       |     | dB                         |                                                                                                              |

| Dynamic Range                     |      |           |     |                            | -60 dB with respect to full-scale analog output                                                              |

| A-Weighted                        | 99   | 104       |     | dB                         |                                                                                                              |

| Total Harmonic Distortion + Noise |      | -90       |     | dB                         | -1 dB with respect to full-scale analog output                                                               |

| Crosstalk                         |      | -100      |     | dB                         | Analog channel-to-channel crosstalk                                                                          |

| Interchannel Gain Mismatch        |      | 25        | 250 | mdB                        |                                                                                                              |

| Gain Error                        | -10  |           | +10 | %                          |                                                                                                              |

| DC Bias                           | 1.4  | 1.5       | 1.6 | V                          |                                                                                                              |

| VOLTAGE REFERENCE                 |      |           |     |                            |                                                                                                              |

| Absolute Voltage (CM)             | 1.4  | 1.5       | 1.6 | V                          |                                                                                                              |

| AUXILIARY ADC                     |      |           |     |                            |                                                                                                              |

| Full-Scale Analog Input           | 2.8  | 3.0       | 3.1 | V                          |                                                                                                              |

| INL S.                            |      | 0.5       |     | LSB                        |                                                                                                              |

| DNL                               |      | 1.0       |     | LSB                        |                                                                                                              |

| Offset                            |      | 15        |     | mV                         |                                                                                                              |

| Input Impedance                   | 17.8 | 30        | 42  | kΩ                         |                                                                                                              |

Specifications are guaranteed at 130°C (ambient).

Table 2.

| Parameter          | Min | Тур       | Max | Unit                       | Test Conditions/Comments                                                             |

|--------------------|-----|-----------|-----|----------------------------|--------------------------------------------------------------------------------------|

| ADC INPUTS         |     |           |     |                            |                                                                                      |

| Number of Channels |     | 2         |     |                            | Stereo input                                                                         |

| Resolution         |     | 24        |     | Bits                       |                                                                                      |

| Full-Scale Input   |     | 100 (283) |     | μA <sub>rms</sub> (μA p-p) | 2 V <sub>rms</sub> input with 20 kΩ (18 kΩ external + 2 kΩ internal) series resistor |

| Parameter                         | Min  | Тур       | Max | Unit                     | Test Conditions/Comments                        |

|-----------------------------------|------|-----------|-----|--------------------------|-------------------------------------------------|

| Signal-to-Noise Ratio             |      |           |     |                          |                                                 |

| A-Weighted                        |      | 100       |     | dB                       |                                                 |

| Dynamic Range                     |      |           |     |                          | –60 dB with respect to full-scale analog input  |

| A-Weighted                        | 92   | 100       |     | dB                       |                                                 |

| Total Harmonic Distortion + Noise |      | -83       |     | dB                       | -3 dB with respect to full-scale analog input   |

| Interchannel Gain Mismatch        |      | 25        | 250 | mdB                      |                                                 |

| Crosstalk                         |      | -82       |     | dB                       | Analog channel-to-channel crosstalk             |

| DC Bias                           | 1.4  | 1.5       | 1.6 | V                        |                                                 |

| Gain Error                        | -11  |           | +11 | %                        |                                                 |

| DAC OUTPUTS                       |      |           |     |                          |                                                 |

| Number of Channels                |      | 4         |     |                          | Two stereo output channels                      |

| Resolution                        |      | 24        |     | Bits                     |                                                 |

| Full-Scale Analog Output          |      | 0.9 (2.5) |     | V <sub>rms</sub> (V p-p) |                                                 |

| Signal-to-Noise Ratio             |      |           |     |                          |                                                 |

| A-Weighted                        |      | 104       |     | dB                       |                                                 |

| Dynamic Range                     |      |           |     |                          | -60 dB with respect to full-scale analog output |

| A-Weighted                        | 98   | 104       |     | dB                       |                                                 |

| Total Harmonic Distortion + Noise |      | -90       |     | dB                       | -1 dB with respect to full-scale analog output  |

| Crosstalk                         |      | -100      |     | dB                       | Analog channel-to-channel crosstalk             |

| Interchannel Gain Mismatch        |      | 25        | 250 | mdB                      |                                                 |

| Gain Error                        | -10  |           | +10 | %                        |                                                 |

| DC Bias                           | 1.4  | 1.5       | 1.6 | V                        |                                                 |

| VOLTAGE REFERENCE                 |      |           |     |                          |                                                 |

| Absolute Voltage (CM)             | 1.4  | 1.5       | 1.6 | V                        |                                                 |

| AUXILIARY ADC                     |      |           |     |                          |                                                 |

| Full-Scale Analog Input           | 2.8  | 3.0       | 3.1 | V                        |                                                 |

| INL                               |      | 0.5       |     | LSB                      |                                                 |

| DNL                               |      | 1.0       |     | LSB                      |                                                 |

| Offset                            |      | 15        |     | mV                       |                                                 |

| Input Impedance                   | 17.8 | 30        | 42  | kΩ                       |                                                 |

### **DIGITAL INPUT/OUTPUT**

Table 3.

| Parameter                                                            | Min | Тур | Max <sup>1</sup> | Unit | Comments                               |

|----------------------------------------------------------------------|-----|-----|------------------|------|----------------------------------------|

| Input Voltage, High (V <sub>H</sub> )                                | 2.0 |     | IOVDD            | V    |                                        |

| Input Voltage, Low (V <sub>IL</sub> )                                |     |     | 0.8              | V    |                                        |

| Input Leakage, High (I⊪)                                             |     |     | 1                | μΑ   | Excluding MCLKI                        |

| Input Leakage, Low (I⊥)                                              |     |     | 1                | μΑ   | Excluding MCLKI and bidirectional pins |

| Bidirectional Pin Pull-Up Current, Low                               |     |     | 150              | μΑ   |                                        |

| MCLKI Input Leakage, High (I <sub>IH</sub> )                         |     |     | 3                | μΑ   |                                        |

| MCLKI Input Leakage, Low (I <sub>IL</sub> )                          |     |     | 3                | μΑ   |                                        |

| High Level Output Voltage (V <sub>OH</sub> ), I <sub>OH</sub> = 2 mA | 2.0 |     |                  | V    |                                        |

| Low Level Output Voltage ( $V_{OL}$ ), $I_{OL} = 2 \text{ mA}$       |     |     | 0.8              | V    |                                        |

| Input Capacitance                                                    |     |     | 5                | рF   |                                        |

| GPIO Output Drive                                                    |     | 2   |                  | mA   |                                        |

$<sup>^{1} \, \</sup>text{Maximum specifications are measured across a temperature range of } -40^{\circ}\text{C to } +130^{\circ}\text{C (case)}, \text{a DVDD range of } 1.62\,\text{V to } 1.98\,\text{V}, \text{and an AVDD range of } 2.97\,\text{V to } 3.63\,\text{V}.$

#### **POWER**

Table 4.

| Parameter                                 | Min | Тур   | Max <sup>1</sup> | Unit |

|-------------------------------------------|-----|-------|------------------|------|

| SUPPLY VOLTAGE                            |     |       |                  |      |

| Analog Voltage                            |     | 3.3   |                  | V    |

| Digital Voltage                           |     | 1.8   |                  | V    |

| PLL Voltage                               |     | 3.3   |                  | V    |

| IOVDD Voltage                             |     | 3.3   |                  | V    |

| SUPPLY CURRENT                            |     |       |                  |      |

| Analog Current (AVDD and PVDD)            |     | 50    | 85               | mA   |

| Digital Current (DVDD)                    |     | 40    | 60               | mA   |

| Analog Current, Reset                     |     | 35    | 55               | mA   |

| Digital Current, Reset                    |     | 1.5   | 4.5              | mA   |

| DISSIPATION                               |     |       |                  |      |

| Operation (AVDD, DVDD, PVDD) <sup>2</sup> |     | 286.5 |                  | mW   |

| Reset, All Supplies                       |     | 118   |                  | mW   |

| POWER SUPPLY REJECTION RATIO (PSRR)       |     |       |                  |      |

| 1 kHz, 200 mV p-p Signal at AVDD          |     | 50    |                  | dB   |

<sup>1</sup> Maximum specifications are measured across a temperature range of -40°C to +130°C (case), a DVDD range of 1.62 V to 1.98 V, and an AVDD range of 2.97 V to 3.63 V.

### **TEMPERATURE RANGE**

Table 5.

| Parameter                | Min | Тур | Max | Unit       |

|--------------------------|-----|-----|-----|------------|

| Functionality Guaranteed | -40 |     | 105 | °C ambient |

### **PLL AND OSCILLATOR**

### Table 6. PLL and Oscillator<sup>1</sup>

| Parameter                                | Min            | Тур | Max            | Unit |

|------------------------------------------|----------------|-----|----------------|------|

| PLL Operating Range                      | MCLK_Nom - 20% |     | MCLK_Nom + 20% | MHz  |

| PLL Lock Time                            |                |     | 20             | ms   |

| Crystal Oscillator Transconductance (gm) |                | 78  |                | mmho |

$<sup>^{1}</sup> Maximum specifications are measured across a temperature range of -40 ^{\circ}C to +130 ^{\circ}C (case), a DVDD range of 1.62 V to 1.98 V, and an AVDD range of 2.97 V to 3.63 V.$

### **REGULATOR**

Table 7. Regulator<sup>1</sup>

| Parameter    | Min | Тур | Max  | Unit |

|--------------|-----|-----|------|------|

| DVDD Voltage | 1.7 | 1.8 | 1.84 | V    |

<sup>&</sup>lt;sup>1</sup> Regulator specifications are calculated using a Zetex Semiconductors FZT953 transistor in the circuit.

<sup>&</sup>lt;sup>2</sup> Power dissipation does not include IOVDD power because the current drawn from this supply is dependent on the loads at the digital output pins.

### **DIGITAL TIMING SPECIFICATIONS**

Table 8. Digital Timing<sup>1</sup>

| Tuble of Digital Timing     | Li               | mit                      |      |                                                                 |

|-----------------------------|------------------|--------------------------|------|-----------------------------------------------------------------|

| Parameter                   | t <sub>MIN</sub> | t <sub>MAX</sub>         | Unit | Description                                                     |

| MASTER CLOCK                |                  |                          |      |                                                                 |

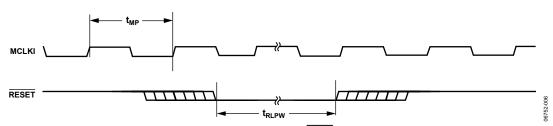

| t <sub>MP</sub>             | 36               | 244                      | ns   | MCLKI period, $512 \times f_s$ mode.                            |

| t <sub>MP</sub>             | 48               | 366                      | ns   | MCLKI period, $384 \times f_s$ mode.                            |

| t <sub>MP</sub>             | 73               | 488                      | ns   | MCLKI period, $256 \times f_s$ mode.                            |

| t <sub>MP</sub>             | 291              | 1953                     | ns   | MCLKI period, $64 \times f_S$ mode.                             |

| SERIAL PORT                 |                  |                          |      |                                                                 |

| t <sub>BIL</sub>            | 40               |                          | ns   | INPUT_BCLK low pulse width.                                     |

| t <sub>BIH</sub>            | 40               |                          | ns   | INPUT_BCLK high pulse width.                                    |

| t <sub>LIS</sub>            | 10               |                          | ns   | INPUT_LRCLK setup. Time to INPUT_BCLK rising.                   |

| t <sub>ын</sub>             | 10               |                          | ns   | INPUT_LRCLK hold. Time from INPUT_BCLK rising.                  |

| t <sub>SIS</sub>            | 10               |                          | ns   | SDATA_INx setup. Time to INPUT_BCLK rising.                     |

| tsıн                        | 10               |                          | ns   | SDATA_INx hold. Time from INPUT_BCLK rising.                    |

| t <sub>LOS</sub>            | 10               |                          | ns   | OUTPUT_LRCLK setup in slave mode.                               |

| <b>t</b> loh                | 10               |                          | ns   | OUTPUT_LRCLK hold in slave mode.                                |

| <b>t</b> <sub>TS</sub>      |                  | 5                        | ns   | OUTPUT_BCLK falling to OUTPUT_LRCLK timing skew.                |

| tsods                       |                  | 40                       | ns   | SDATA_OUTx delay in slave mode. Time from OUTPUT_BCLK falling.  |

| <b>t</b> <sub>SODM</sub>    |                  | 40                       | ns   | SDATA_OUTx delay in master mode. Time from OUTPUT_BCLK falling. |

| SPI PORT                    |                  |                          |      |                                                                 |

| $f_{CCLK}$                  |                  | 6.25                     | MHz  | CCLK frequency.                                                 |

| <b>t</b> ccpl               | 80               |                          | ns   | CCLK pulse width low.                                           |

| t <sub>CCPH</sub>           | 80               |                          | ns   | CCLK pulse width high.                                          |

| t <sub>CLS</sub>            | 0                |                          | ns   | CLATCH setup. Time to CCLK rising.                              |

| t <sub>CLH</sub>            | 100              |                          | ns   | CLATCH hold. Time from CCLK rising.                             |

| <b>t</b> <sub>CLPH</sub>    | 80               |                          | ns   | CLATCH pulse width high.                                        |

| t <sub>CDS</sub>            | 0                |                          | ns   | CDATA setup. Time to CCLK rising.                               |

| <b>t</b> <sub>CDH</sub>     | 80               |                          | ns   | CDATA hold. Time from CCLK rising.                              |

| $t_COD$                     |                  | 101                      | ns   | COUT delay. Time from CCLK falling.                             |

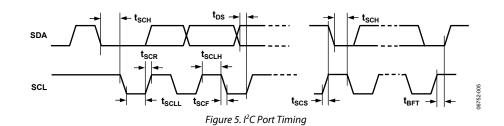

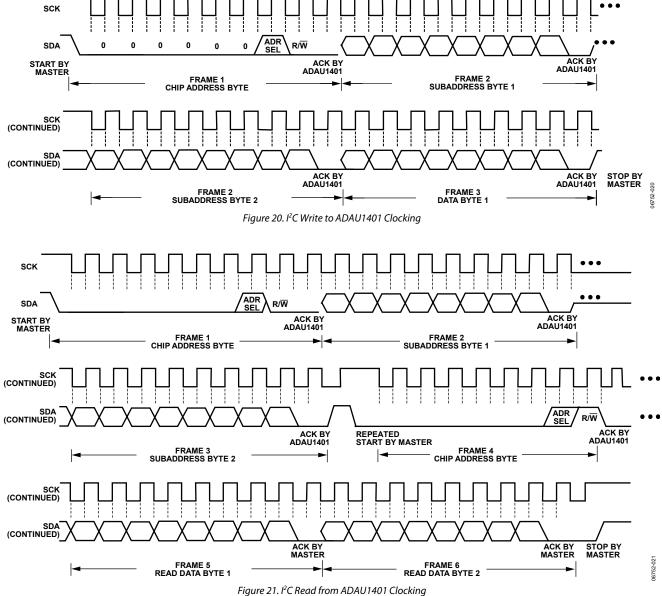

| I <sup>2</sup> C PORT       |                  |                          |      |                                                                 |

| $f_{SCL}$                   |                  | 400                      | kHz  | SCL frequency.                                                  |

| <b>t</b> <sub>SCLH</sub>    | 0.6              |                          | μs   | SCL high.                                                       |

| t <sub>SCLL</sub>           | 1.3              |                          | μs   | SCL low.                                                        |

| t <sub>scs</sub>            | 0.6              |                          | μs   | Setup time, relevant for repeated start condition.              |

| t <sub>SCH</sub>            | 0.6              |                          | μs   | Hold time. After this period, the first clock is generated.     |

| t <sub>DS</sub>             | 100              |                          | ns   | Data setup time.                                                |

| t <sub>SCR</sub>            |                  | 300                      | ns   | SCL rise time.                                                  |

| tscf                        |                  | 300                      | ns   | SCL fall time.                                                  |

| t <sub>SDR</sub>            |                  | 300                      | ns   | SDA rise time.                                                  |

| t <sub>SDF</sub>            |                  | 300                      | ns   | SDA fall time.                                                  |

| t <sub>BFT</sub>            | 0.6              |                          |      | Bus-free time. Time between stop and start.                     |

| MULTIPURPOSE PINS AND RESET |                  |                          |      |                                                                 |

| t <sub>GRT</sub>            |                  | 50                       | ns   | GPIO rise time.                                                 |

| t <sub>GFT</sub>            |                  | 50                       | ns   | GPIO fall time.                                                 |

| t <sub>GIL</sub>            |                  | $1.5 \times 1/f_{\rm S}$ | μs   | GPIO input latency. Time until high/low value is read by core.  |

| t <sub>RLPW</sub>           | 20               |                          | ns   | RESET low pulse width.                                          |

| *KLPW                       | 1 20             |                          | 113  | neserion paise matri                                            |

<sup>&</sup>lt;sup>1</sup> All timing specifications are given for the default (I<sup>2</sup>S) states of the serial input port and the serial output port (see Table 67).

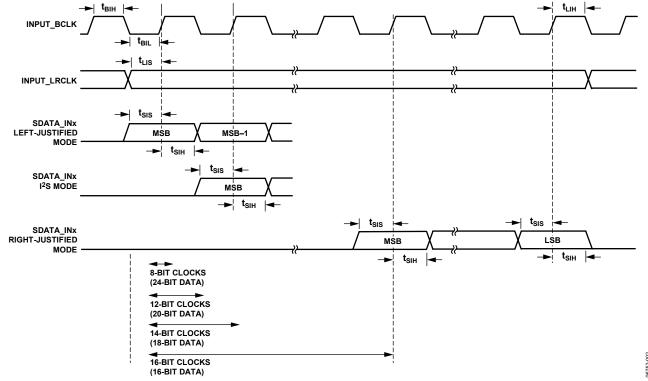

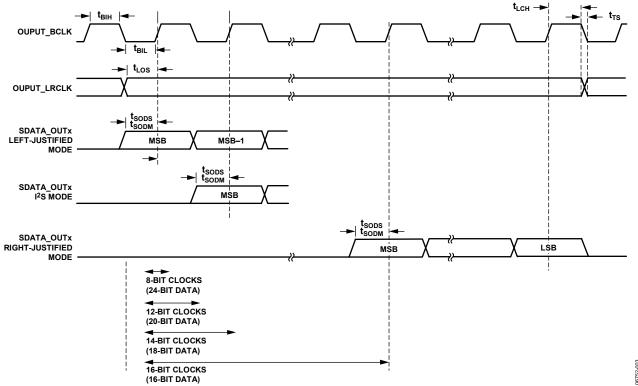

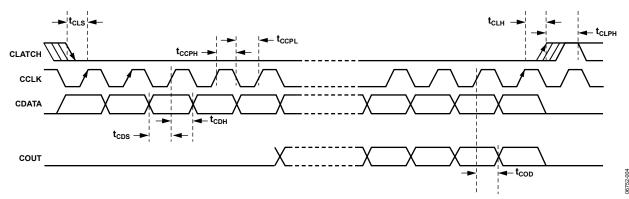

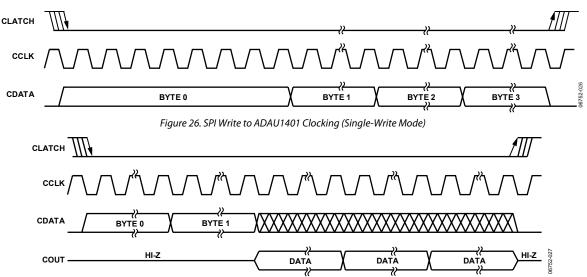

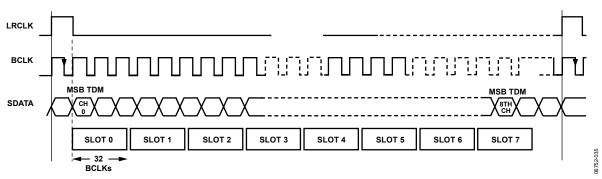

### **DIGITAL TIMING DIAGRAMS**

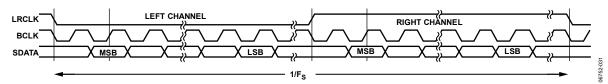

Figure 2. Serial Input Port Timing

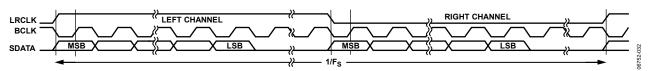

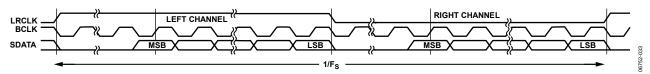

Figure 3. Serial Output Port Timing

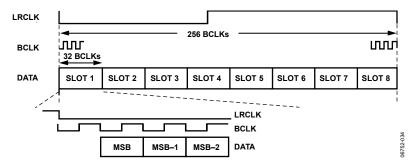

Figure 4. SPI Port Timing

Figure 6. Master Clock and RESET Timing

### **ABSOLUTE MAXIMUM RATINGS**

### Table 9.

| Parameter                    | Rating                      |

|------------------------------|-----------------------------|

| DVDD to GND                  | 0 V to 2.2 V                |

| AVDD to GND                  | 0 V to 4.0 V                |

| IOVDD to GND                 | 0 V to 4.0 V                |

| Digital Inputs               | DGND – 0.3 V, IOVDD + 0.3 V |

| Maximum Junction Temperature | 135°C                       |

| Storage Temperature Range    | −65°C to +150°C             |

| Soldering (10 sec)           | 300°C                       |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### THERMAL RESISTANCE

$\theta_{JA}$  is specified for the worst-case conditions, that is, a device soldered in a circuit board for surface-mount packages.

Table 10. Thermal Resistance

| Package Type | θ <sub>JA</sub> | <b>Ө</b> зс | Unit |

|--------------|-----------------|-------------|------|

| 48-Lead LQFP | 72              | 19.5        | °C/W |

### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

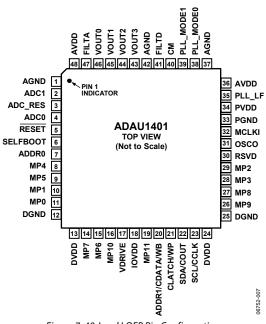

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 7. 48-Lead LQFP Pin Configuration

**Table 11. Pin Function Descriptions**

| Pin No.   | Mnemonic | Type <sup>1</sup> | Page No. | Description                                                                                                                                                                                                                                                                   |

|-----------|----------|-------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 37, 42 | AGND     | PWR               |          | Analog Ground Pin. The AGND, DGND, and PGND pins can be tied directly together in a common ground plane. AGND should be decoupled to an AVDD pin with a 100 nF capacitor.                                                                                                     |

| 2         | ADC1     | A_IN              | 19       | Analog Audio Input 1. Full-scale 100 $\mu A_{rms}$ input. Current input allows input voltage level to be scaled with an external resistor. An 18 k $\Omega$ resistor gives a 2 $V_{rms}$ full-scale input.                                                                    |

| 3         | ADC_RES  | A_IN              | 19       | ADC Reference Current. The full-scale current of the ADCs can be set with an external 18 $k\Omega$ resistor connected between this pin and ground.                                                                                                                            |

| 4         | ADC0     | A_IN              | 19       | Analog Audio Input 0. Full-scale 100 $\mu A_{rms}$ input. Current input allows input voltage level to be scaled with an external resistor. An 18 k $\Omega$ resistor gives a 2 $V_{rms}$ full-scale input.                                                                    |

| 5         | RESET    | D_IN              |          | Active Low Reset Input. Reset is triggered on a high-to-low edge, and the ADAU1401 exits reset on a low-to-high edge. For more information about initialization, see the Power-Up Sequence section.                                                                           |

| 6         | SELFBOOT | D_IN              | 26       | Enable/Disable Self-Boot. SELFBOOT selects control port (low) or self-boot (high). Setting this pin high initiates a self-boot operation when the ADAU1401 is brought out of a reset. This pin can be tied directly to the control voltage or pulled up/down with a resistor. |

| 7         | ADDR0    | D_IN              | 22       | I <sup>2</sup> C and SPI Address 0. In combination with ADDR1, this pin allows up to four ADAU1401s to be used on the same I <sup>2</sup> C bus and up to two ICs to be used with a common SPI CLATCH signal.                                                                 |

| 8         | MP4      | D_IO              | 44       | Multipurpose GPIO or Serial Input Port LRCLK (INPUT_LRCLK).                                                                                                                                                                                                                   |

| 9         | MP5      | D_IO              | 44       | Multipurpose GPIO or Serial Input Port BCLK (INPUT_BCLK).                                                                                                                                                                                                                     |

| 10        | MP1      | D_IO              | 44       | Multipurpose GPIO or Serial Input Port Data 1 (SDATA_IN0).                                                                                                                                                                                                                    |

| 11        | MP0      | D_IO              | 44       | Multipurpose GPIO or Serial Input Port Data 0 (SDATA_IN1).                                                                                                                                                                                                                    |

| 12, 25    | DGND     | PWR               |          | Digital Ground Pin. The AGND, DGND, and PGND pins can be tied directly together in a common ground plane. DGND should be decoupled to a DVDD pin with a 100 nF capacitor.                                                                                                     |

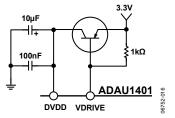

| 13, 24    | DVDD     | PWR               |          | 1.8 V Digital Supply. This can be supplied either externally or generated from a 3.3 V supply with the on-board 1.8 V regulator. DVDD should be decoupled to DGND with a 100 nF capacitor.                                                                                    |

| Pin No. | Mnemonic       | Type <sup>1</sup> | Page No.   | Description                                                                                                                                                                                                                                                                                                                                                                    |

|---------|----------------|-------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14      | MP7            | D_IO              | 44         | Multipurpose GPIO or Serial Output Port Data 1 (SDATA_OUT1).                                                                                                                                                                                                                                                                                                                   |

| 15      | MP6            | D_IO              | 44         | Multipurpose GPIO, Serial Output Port Data 0, or TDM Data Output (SDATA_OUT0).                                                                                                                                                                                                                                                                                                 |

| 16      | MP10           | D_IO              | 44         | Multipurpose GPIO or Serial Output Port LRCLK (OUTPUT_LRCLK).                                                                                                                                                                                                                                                                                                                  |

| 17      | VDRIVE         | A_OUT             | 18         | Drive for 1.8 V Regulator. The base of the voltage regulator external PNP transistor is driven from VDRIVE.                                                                                                                                                                                                                                                                    |

| 18      | IOVDD          | PWR               |            | Supply for Input and Output Pins. The voltage on this pin sets the highest input voltage that should be seen on the digital input pins. This pin is also the supply for the digital output signals on the control port and MP pins. IOVDD should always be set to 3.3 V. The current draw of this pin is variable because it is dependent on the loads of the digital outputs. |

| 19      | MP11           | D_IO              | 44         | Multipurpose GPIO or Serial Output Port BCLK (OUTPUT_BCLK).                                                                                                                                                                                                                                                                                                                    |

| 20      | ADDR1/CDATA/WB | D_IN              | 22, 25, 26 | ADDR1: I <sup>2</sup> C Address 1. In combination with ADDR0, this sets the I <sup>2</sup> C address of the IC so that four ADAU1401s can be used on the same I <sup>2</sup> C bus. CDATA: SPI Data Input.                                                                                                                                                                     |

|         |                |                   |            | WB: EEPROM Writeback Trigger. A rising (default) or falling (if set in the EEPROM messages) edge on this pin triggers a writeback of the interface registers to the external EEPROM. This function can be used to save parameter data on power-down.                                                                                                                           |

| 21      | CLATCH/WP      | D_IO              | 24, 26     | CLATCH: SPI Latch Signal. Must go low at the beginning of an SPI transaction and high at the end of a transaction. Each SPI transaction can take a different number of CCLKs to complete, depending on the address and read/write bit that are sent at the beginning of the SPI transaction.                                                                                   |

|         |                |                   |            | WP: Self-Boot EEPROM Write Protect. This pin is an open-collector output when in self-boot mode. The ADAU1401 pulls this low to prohibit writes to an external EEPROM. This pin should be pulled high to 3.3 V.                                                                                                                                                                |

| 22      | SDA/COUT       | D_IO              | 22, 25     | SDA: $I^2C$ Data. This pin is a bidirectional open-collector. The line connected to this pin should have a 2.2 k $\Omega$ pull-up resistor. COUT: This SPI data output is used for reading back registers and memory                                                                                                                                                           |

| 23      | SCL/CCLK       | D_IO              | 22.25      | locations. It is three-stated when an SPI read is not active.  SCL: I <sup>2</sup> C Clock. This pin is always an open-collector input when in I <sup>2</sup> C control                                                                                                                                                                                                        |

| 23      | SCL/CCLK       | <i>D_</i> 10      | 22, 25     | mode. In self-boot mode, this pin is an open-collector output ( $I^2C$ master). The line connected to this pin should have a 2.2 k $\Omega$ pull-up resistor. CCLK: SPI Clock. This pin can either run continuously or be gated off between SPI transactions.                                                                                                                  |

| 26      | MP9            | D_IO/A_IO         | 44         | Multipurpose GPIO, Serial Output Port Data 3 (SDATA_OUT3), or Auxiliary ADC Input 0.                                                                                                                                                                                                                                                                                           |

| 27      | MP8            | D_IO/A_IO         | 44         | Multipurpose GPIO, Serial Output Port Data 2 (SDATA_OUT2), or Auxiliary ADC Input 3.                                                                                                                                                                                                                                                                                           |

| 28      | MP3            | D_IO/A_IO         | 44         | Multipurpose GPIO, Serial Input Port Data 3 (SDATA_IN3), or Auxiliary ADC Input 2.                                                                                                                                                                                                                                                                                             |

| 29      | MP2            | D_IO/A_IO         | 44         | Multipurpose GPIO, Serial Input Port Data 2 (SDATA_IN2), or Auxiliary ADC Input 1.                                                                                                                                                                                                                                                                                             |

| 30      | RSVD           | Х                 |            | Reserved. Tie to ground, either directly or through a pull-down resistor.                                                                                                                                                                                                                                                                                                      |

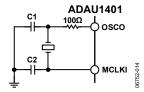

| 31      | osco           | D_OUT             | 17         | Crystal Oscillator Circuit Output. A $100 \Omega$ damping resistor should be connected between this pin and the crystal. This output should not be used to directly drive a clock to another IC. If the crystal oscillator is not used, this pin can be left disconnected.                                                                                                     |

| 32      | MCLKI          | D_IN              | 17         | Master Clock Input. MCLKI can either be connected to a 3.3 V clock signal or be the input from the crystal oscillator circuit.                                                                                                                                                                                                                                                 |

| 33      | PGND           | PWR               |            | PLL Ground Pin. The AGND, DGND, and PGND pins can be tied directly together in a common ground plane. PGND should be decoupled to PVDD with a 100 nF capacitor.                                                                                                                                                                                                                |

| 34      | PVDD           | PWR               |            | 3.3 V Power Supply for the PLL and the Auxiliary ADC Analog Section. This should be decoupled to PGND with a 100 nF capacitor.                                                                                                                                                                                                                                                 |

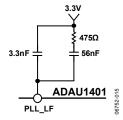

| 35      | PLL_LF         | A_OUT             | 17         | PLL Loop Filter Connection. Two capacitors and a resistor need to be connected to this pin, as shown in Figure 15.                                                                                                                                                                                                                                                             |

| 36, 48  | AVDD           | PWR               |            | 3.3 V Analog Supply. This should be decoupled to AGND with a 100 nF capacitor.                                                                                                                                                                                                                                                                                                 |

| Pin No. | Mnemonic  | Type <sup>1</sup> | Page No. | Description                                                                                                                                                                                                                                                                                                                                                                                                |

|---------|-----------|-------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 38      | PLL_MODE0 | D_IN              | 17       | PLL Mode Setting. PLL_MODE0 and PLL_MODE1 set the output frequency                                                                                                                                                                                                                                                                                                                                         |

| 39      | PLL_MODE1 | D_IN              | 17       | of the master clock PLL. See the Setting Master Clock/PLL Mode section for more details.                                                                                                                                                                                                                                                                                                                   |

| 40      | СМ        | A_OUT             |          | 1.5 V Common-Mode Reference. A 47 $\mu$ F decoupling capacitor should be connected between this pin and ground to reduce crosstalk between the ADCs and DACs. The material of the capacitors is not critical. This pin can be used to bias external analog circuits, as long as those circuits are not drawing current from the pin (such as when CM is connected to the noninverting input of an op amp). |

| 41      | FILTD     | A_OUT             |          | DAC Filter Decoupling Pin. A 10 $\mu$ F capacitor should be connected between this pin and ground. The capacitor material is not critical. The voltage on this pin is 1.5 V.                                                                                                                                                                                                                               |

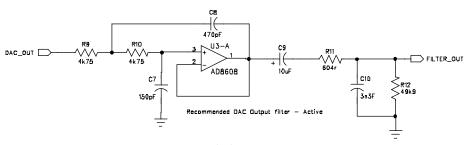

| 43      | VOUT3     | A_OUT             | 20       | VOUT0 to VOUT3 are the DAC Outputs. The full-scale output voltage is                                                                                                                                                                                                                                                                                                                                       |

| 44      | VOUT2     | A_OUT             | 20       | 0.9 V <sub>rms</sub> . These outputs can be used with either active or passive output                                                                                                                                                                                                                                                                                                                      |

| 45      | VOUT1     | A_OUT             | 20       | reconstruction filters.                                                                                                                                                                                                                                                                                                                                                                                    |

| 46      | VOUT0     | A_OUT             | 20       |                                                                                                                                                                                                                                                                                                                                                                                                            |

| 47      | FILTA     | A_OUT             |          | ADC Filter Decoupling Pin. A 10 $\mu$ F capacitor should be connected between this pin and ground. The capacitor material is not critical. The voltage on this pin is 1.5 V.                                                                                                                                                                                                                               |

$<sup>^{1}\,</sup>PWR = power/ground, A\_IN = analog\ input, D\_IN = digital\ input, A\_OUT = analog\ output, D\_IO = digital\ input/output, D\_IO/A\_IO = digital\ input/output\ or\ analog\ input/output.$

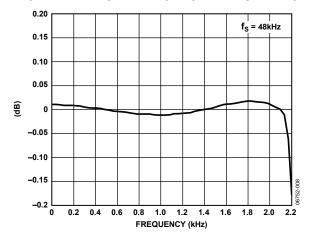

# TYPICAL PERFORMANCE CHARACTERISTICS

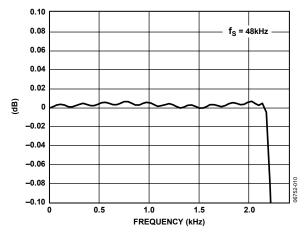

Figure 8. ADC Pass-Band Filter Response

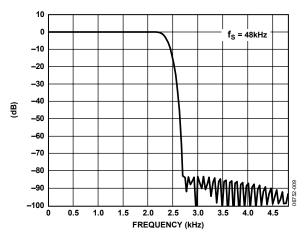

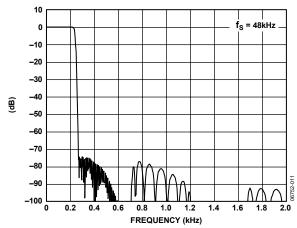

Figure 9. ADC Stop-Band Filter Response

Figure 10. DAC Pass-Band Filter Response

Figure 11. DAC Stop-Band Filter Response

# SYSTEM BLOCK DIAGRAM

Figure 12. System Block Diagram

### **OVERVIEW**

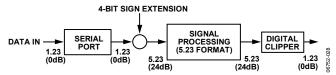

The core of the ADAU1401 is a 28-bit DSP (56-bit with double-precision processing) optimized for audio processing. The program and parameter RAMs can be loaded with a custom audio processing signal flow built by using SigmaStudio graphical programming software from Analog Devices, Inc. The values stored in the parameter RAM control individual signal processing blocks, such as equalization filters, dynamics processors, audio delays, and mixer levels. A safeload feature allows for transparent parameter updates and prevents clicks in the output signals.

The program RAM, parameter RAM, and register contents can be saved in an external EEPROM, from which the ADAU1401 can self-boot on startup. In this standalone mode, parameters can be controlled through the on-board multipurpose pins. The ADAU1401 can accept controls from switches, potentiometers, rotary encoders, and IR receivers. Parameters such as volume and tone settings can be saved to the EEPROM on power-down and recalled again on power-up.

The ADAU1401 can operate with digital or analog inputs and outputs, or a mix of both. The stereo ADC and four DACs each have an SNR of at least +100 dB and a THD + N of at least -83 dB. The 8-channel, flexible serial data input/output ports allow glueless interconnection to a variety of ADCs, DACs, general-purpose DSPs, S/PDIF receivers and transmitters, and sample rate converters. The serial ports of the ADAU1401 can be configured in I<sup>2</sup>S, left-justified, right-justified, or TDM serial port compatible modes.

Twelve multipurpose (MP) pins allow the ADAU1401 to receive external control signals as input and to output flags or controls to other devices in the system. The MP pins can be configured as digital I/Os, inputs to the 4-channel auxiliary ADC, or serial data I/O ports. As inputs, they can be connected to buttons, switches, rotary encoders, potentiometers, IR receivers, or other external circuitry to control the internal signal processing program. When configured as outputs, these pins can be used to drive LEDs, control other ICs, or connect to other external circuitry in an application.

The ADAU1401 has a sophisticated control port that supports complete read/write capability of all memory locations. Control registers are provided to offer complete control of the chip's configuration and serial modes. The ADAU1401 can be configured for either SPI or I<sup>2</sup>C control, or can self-boot from an external EEPROM.

An on-board oscillator can be connected to an external crystal to generate the master clock. In addition, a master clock phase-locked loop (PLL) allows the ADAU1401 to be clocked from a

variety of different clock speeds. The PLL can accept inputs of  $64 \times f_s$ ,  $256 \times f_s$ ,  $384 \times f_s$ , or  $512 \times f_s$  to generate the internal master clock of the core.

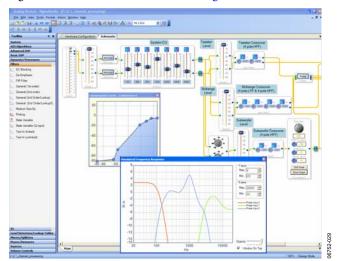

The SigmaStudio software is used to program and control the SigmaDSP® through the control port. Along with designing and tuning a signal flow, the tools can be used to configure all of the DSP registers and burn a new program into the external EEPROM. SigmaStudio's graphical interface allows anyone with digital or analog audio processing knowledge to easily design a DSP signal flow and port it to a target application. At the same time, it provides enough flexibility and programmability for an experienced DSP programmer to have in-depth control of the design. In SigmaStudio, the user can connect graphical blocks (such as biquad filters, dynamics processors, mixers, and delays), compile the design, and load the program and parameter files into the ADAU1401 memory through the control port. Signal processing blocks available in the provided libraries include

- Single- and double-precision biquad filters

- Processors with peak or rms detection for monochannel and multichannel dynamics

- Mixers and splitters

- Tone and noise generators

- Fixed and variable gain

- Loudness

- Delay

- Stereo enhancement

- Dynamic bass boost

- Noise and tone sources

- FIR filters

- Level detectors

- GPIO control and conditioning

Additional processing blocks are always being developed. Analog Devices also provides proprietary and third-party algorithms for applications such as matrix decoding, bass enhancement, and surround virtualizers. Contact Analog Devices for information about licensing these algorithms.

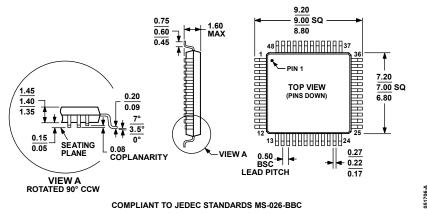

The ADAU1401 operates from a 1.8 V digital power supply and a 3.3 V analog supply. An on-board voltage regulator can be used to operate the chip from a single 3.3 V supply. It is fabricated on a single monolithic, integrated circuit and is packaged in a 48-lead LQFP for operation over the  $0^{\circ}$ C to +70°C temperature range.

### INITIALIZATION

This section details the procedure for properly setting up the ADAU1401. The following five-step sequence provides an overview of how to initialize the IC:

- 1. Apply power to ADAU1401.

- 2. Wait for PLL to lock.

- 3. Load SigmaDSP program and parameters.

- Set up registers (including multipurpose pins and digital interfaces).

- Turn off the default muting of the converters, clear the data registers, and initialize the DAC setup register (see the Control Registers Setup section for specific settings).

To only test analog audio pass-through (ADCs to DACs), Steps 3 and 4 can be skipped and the default internal program can be used.

#### **POWER-UP SEQUENCE**

The ADAU1401 has a built-in power-up sequence that initializes the contents of all internal RAMs on power-up or when the device is brought out of a reset. On the positive edge of RESET, the contents of the internal program boot ROM are copied to the internal program RAM memory, the parameter RAM is filled with values (all 0s) from its associated boot ROM, and all registers are initialized to 0s. The default boot ROM program copies audio from the inputs to the outputs without processing it (see Figure 13). In this program, serial digital Input 0 and Input 1 are output on DAC0 and DAC1 and serial digital Output 0 and Output 1. ADC0 and ADC1 are output on DAC2 and DAC3. The data memories are also zeroed at power-up. New values should not be written to the control port until the initialization is complete.

Table 12. Power-Up Time

| MCLKI Input                               | Init.<br>Time | Max Program/<br>Parameter/Register<br>Boot Time (I <sup>2</sup> C) | Total  |

|-------------------------------------------|---------------|--------------------------------------------------------------------|--------|

| 3.072 MHz (64 $\times$ f <sub>s</sub> )   | 85 ms         | 175 ms                                                             | 260 ms |

| 11.289 MHz (256 $\times$ f <sub>s</sub> ) | 23 ms         | 175 ms                                                             | 198 ms |

| 12.288 MHz (256 $\times$ f <sub>s</sub> ) | 21 ms         | 175 ms                                                             | 196 ms |

| 18.432 MHz (384 $\times$ fs)              | 16 ms         | 175 ms                                                             | 191 ms |

| 24.576 MHz (512 $\times$ f <sub>s</sub> ) | 11 ms         | 175 ms                                                             | 186 ms |

The PLL start-up time lasts for  $2^{18}$  cycles of the clock on the MCLKI pin. This time ranges from 10.7 ms for a 24.576 MHz (512 × f<sub>s</sub>) input clock to 85.3 ms for a 3.072 MHz (64 × f<sub>s</sub>) input clock and is measured from the rising edge of  $\overline{\text{RESET}}$ . Following the PLL startup, the duration of the ADAU1401 boot cycle is about 42 µs for a f<sub>s</sub> of 48 kHz. The user should avoid writing to or reading from the ADAU1401 during this start-up time. For an MCLK input of 12.288 MHz, the full initialization sequence (PLL startup plus boot cycle) is approximately 21 ms. As the device comes out of a reset, the clock mode is immediately set by the PLL\_MODE0 and PLL\_MODE1 pins. The reset is synchronized to the falling edge of the internal clock.

Table 12 lists typical times to boot the ADAU1401 into an application's operational state, assuming a 400 kHz  $I^2C$  clock loading a full program, parameter set, and all registers (about 8.5 kB). In reality, most applications will not fill the RAMs and therefore boot time (Column 3 of Table 12) will be less.

### **CONTROL REGISTERS SETUP**

The following registers must be set as described in this section to initialize the ADAU1401. These settings are the basic minimum settings needed to operate the IC with an analog input/output of 48 kHz. More registers may need to be set, depending on the application. See the RAMs and Registers section for additional settings.

### **DSP Core Control Register (Address 2076)**

Set Bits [4:2] (ADM, DAM, and CR) each to 1.

### DAC Setup Register (Address 2087)

Set Bits [0:1] (DS [1:0]) to 01.

# RECOMMENDED PROGRAM/PARAMETER LOADING PROCEDURE

When writing large amounts of data to the program or parameter RAM in direct write mode, the processor core should be disabled to prevent unpleasant noises from appearing in the audio output.

- 1. Set Bit 3 and Bit 4 (active low) of the core control register to 1 to mute the ADCs and DACs. This begins a volume ramp-down.

- 2. Set Bit 2 (active low) of the core control register to 1. This zeroes the SigmaDSP accumulators, the data output registers, and the data input registers.

- 3. Fill the program RAM using burst mode writes.

- 4. Fill the parameter RAM using burst mode writes.

- 5. Deassert Bit 2 to Bit 4 of the core control register.

Figure 13. Default Program Signal Flow

### **POWER-REDUCTION MODES**

Sections of the ADAU1401 chip can be turned on and off as needed to reduce power consumption. These include the ADCs, DACs, and voltage reference.

The individual analog sections can be turned off by writing to the auxiliary ADC and power control register. By default, the ADCs, DACs, and reference are enabled (all bits set to 0). Each of these can be turned off by writing a 1 to the appropriate bits in this register. The ADC power-down mode powers down both ADCs, and each DAC can be powered down individually. The current savings is about 15 mA when the ADCs are powered down and about 4 mA for each DAC that is powered down. The voltage reference, which is supplied to both the ADCs and DACs, should only be powered down if all ADCs and DACs are powered down. The reference is powered down by setting both Bit 6 and Bit 7 of the control register.

#### **USING THE OSCILLATOR**

The ADAU1401 can use an on-board oscillator to generate its master clock. The oscillator is designed to work with a  $256 \times f_S$  master clock, which is 12.288 MHz for a  $f_S$  of 48 kHz and 11.2896 MHz for a  $f_S$  of 44.1 kHz. The crystal in the oscillator circuit should be an AT-cut, parallel resonator operating at its fundamental frequency. Figure 14 shows the external circuit recommended for proper operation.

Figure 14. Crystal Oscillator Circuit

The 100  $\Omega$  damping resistor on OSCO gives the oscillator a voltage swing of approximately 2.2 V. The crystal shunt capacitance should be 7 pF. Its load capacitance should be about 18 pF, although the circuit supports values of up to 25 pF. The necessary values of the C1 and C2 load capacitors can be calculated from the crystal load capacitance as follows:

$$C_L = \frac{C1 \times C2}{C1 + C2} + C_{stray}$$

where  $C_{stray}$  is the stray capacitance in the circuit and is usually assumed to be approximately 2 pF to 5 pF.

OSCO should not be used to directly drive the crystal signal to another IC. This signal is an analog sine wave, and it is not appropriate to use it to drive a digital input. There are two options for using the ADAU1401 to provide a master clock to other ICs in the system. The first, and less recommended, method is to use a high impedance input digital buffer on the OSCO signal. If this is done, minimize the trace length to the buffer input. The second method is to use a clock from the serial output port. Pin MP11 can be set as an output (master) clock divided down from the internal core clock. If this pin is set to serial output port (OUTPUT\_BCLK) mode in the multipurpose pin configuration register (2081) and the port is set to master in the serial output control register (2078), the desired output frequency can also be set in the serial output control register with Bits OBF [1:0] (see Table 50).

If the oscillator is not utilized in the design, it can be powered down to save power. This can be done if a system master clock is already available in the system. By default, the oscillator is powered on. The oscillator powers down when a 1 is written to the OPD bit of the oscillator power-down register (see Table 61).

### SETTING MASTER CLOCK/PLL MODE

The MCLKI input of the ADAU1401 feeds a PLL, which generates the 50 MIPS SigmaDSP core clock. In normal operation, the input to MCLKI must be one of the following:  $64 \times f_s$ ,  $256 \times f_s$ ,  $384 \times f_s$ , or  $512 \times f_s$ , where  $f_s$  is the input sampling rate. The mode is set on PLL\_MODE0 and PLL\_MODE1 as described in Table 13. If the ADAU1401 is set to receive double-rate signals (by reducing the number of program steps per sample by a factor of 2 using the core control register), the master clock frequency must be  $32 \times f_s$ ,  $128 \times f_s$ ,  $192 \times f_s$ , or  $256 \times f_s$ . If the ADAU1401 is set to receive quad-rate signals (by reducing the number of program steps per sample by a factor of 4 using the core control register), the master clock frequency must be  $16 \times f_s$ ,  $64 \times f_s$ ,  $96 \times f_s$ , or  $128 \times f_s$ . On power-up, a clock signal must be present on MCLK so that the ADAU1401 can complete its initialization routine.

**Table 13. PLL Modes**

| MCLKI Input      | PLL_MODE0 | PLL_MODE1 |

|------------------|-----------|-----------|

| $64 \times f_S$  | 0         | 0         |

| $256 \times f_S$ | 0         | 1         |

| $384 \times f_S$ | 1         | 0         |

| $512 \times f_S$ | 1         | 1         |

The clock mode should not be changed without also resetting the ADAU1401. If the mode is changed during operation, a click or pop can result in the output signals. The state of the PLL\_MODEx pins should be changed while RESET is held low.

The PLL loop filter should be connected to the PLL\_LF pin. This filter, shown in Figure 15, includes three passive components—two capacitors and a resistor. The values of these components do not need to be exact; the tolerance can be up to 10% for the resistor and up to 20% for the capacitors. The 3.3 V signal shown in Figure 15 can be connected to the AVDD supply of the chip.

Figure 15. PLL Loop Filter

#### **VOLTAGE REGULATOR**

The digital voltage of the ADAU1401 must be set to 1.8 V. The chip includes an on-board voltage regulator that allows the device to be used in systems without an available 1.8 V supply but with an available 3.3 V supply. The only external components needed in such instances are a PNP transistor, a resistor, and a few bypass capacitors. Only one pin, VDRIVE, is necessary to support the regulator.

The recommended design for the voltage regulator is shown in Figure 16. The 10  $\mu F$  and 100 nF capacitors shown in this configuration are recommended for bypassing, but are not necessary for operation. Each DVDD pin should have its own 100 nF bypass capacitor, but only one bulk capacitor (10  $\mu F$  to 47  $\mu F$ ) is needed for both DVDD pins. With this configuration, 3.3 V is the main system voltage; 1.8 V is generated at the transistor's collector, which is connected to the DVDD pins. VDRIVE is connected to the base of the PNP transistor. If the regulator is not used in the design, VDRIVE can be tied to ground.

Two specifications must be considered when choosing a regulator transistor: The transistor's current amplification factor ( $h_{\text{FE}}$  or beta) should be at least 100, and the transistor's collector must be able to dissipate the heat generated when regulating from 3.3 V to 1.8 V. The maximum digital current drawn from the ADAU1401 is 60 mA. The equation to determine the minimum power dissipation of the transistor is as follows:

$$(3.3 \text{ V} - 1.8 \text{ V}) \times 60 \text{ mA} = 90 \text{ mW}$$

There are many transistors, such as the FZT953 from Zetex Semiconductors, with these specifications available in small SOT-23 or SOT-223 packages.

Figure 16. Voltage Regulator Configuration

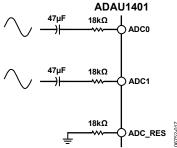

### **AUDIO ADCs**

The ADAU1401 has two  $\Sigma$ - $\Delta$  ADCs. The signal-to-noise ratio (SNR) of the ADCs is 100 dB, and the THD + N is -83 dB.

The stereo audio ADCs are current input; therefore, a voltage-to-current resistor is required on the inputs. This means that the voltage level of the input signals to the system can be set to any level; only the input resistors need to be scaled to provide the proper full-scale current input. The ADC0 and ADC1 input pins, as well as ADC\_RES, have an internal  $2\,k\Omega$  resistor for ESD protection. The voltage seen directly on the ADC input pins is the 1.5 V common mode.

The external resistor connected to ADC\_RES sets the full-scale current input of the ADCs. The full range of the ADC inputs is  $100~\mu A_{rms}$  with an external  $18~k\Omega$  resistor on ADC\_RES (20  $k\Omega$  total, because it is in series with the internal 2  $k\Omega$ ). The only reason to change the ADC\_RES resistor is if a sampling rate other than 48~kHz is used.

The voltage-to-current resistors connected to ADC0/ADC1 set the full-scale voltage input of the ADCs. With a full-scale current input of 100  $\mu A_{rms}$ , a 2.0  $V_{rms}$  signal with an external 18  $k\Omega$  resistor (in series with the 2  $k\Omega$  internal resistor) results in an input using the full range of the ADC. The matching of these resistors to the ADC\_RES resistor is important to the operation of the ADCs. For these three resistors, a 1% tolerance is recommended.

Either the ADC0 and/or ADC1 input pins can be left unconnected if that channel of the ADC is unused.

These calculations of resistor values assume a 48 kHz sample rate. The recommended input and current setting resistors scale linearly with the sample rate because the ADCs have a switched-capacitor input. The total value (2 k $\Omega$  internal plus external resistor) of the ADC\_RES resistor with sample rate fs New can be calculated as follows:

$$R_{total} = 20 \text{ k}\Omega \times \frac{48,000}{f_{s\_NEW}}$$

The values of the resistors (internal plus external) in series with the ADC0 and ADC1 pins can be calculated as follows:

$$R_{Input\ Total} = (RMS\ Input\ Voltage) \times 10\ k\Omega \times \frac{48,000}{f_{S\_NEW}}$$

Table 14 lists the external and total resistor values for common signal input levels at a 48 kHz sampling rate. A full-scale rms input voltage of 0.9 V is shown in the table because a full-scale signal at this input level is equal to a full-scale output on the DACs.

**Table 14. ADC Input Resistor Values**

|   | Full-Scale<br>RMS Input<br>Voltage (V) | ADC_RES<br>Value (kΩ) | ADC0/ADC1<br>Resistor<br>Value (kΩ) | Total ADCO/ADC1<br>Input Resistance<br>(External +<br>Internal) (kΩ) |

|---|----------------------------------------|-----------------------|-------------------------------------|----------------------------------------------------------------------|

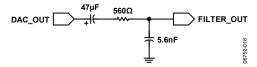

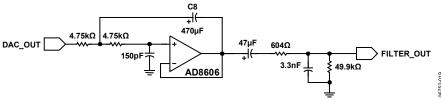

|   | 0.9                                    | 18                    | 7                                   | 9                                                                    |