# Ultralow Noise, High Speed, BiFET Op Amp

**AD745**

FEATURES ULTRALOW NOISE PERFORMANCE 2.9 nV/ $\sqrt{\text{Hz}}$  at 10 kHz 0.38  $\mu$ V p-p, 0.1 Hz to 10 Hz

6.9 fA/ $\sqrt{\text{Hz}}$  Current Noise at 1 kHz

**EXCELLENT AC PERFORMANCE**

12.5 V/ $\mu s$  Slew Rate

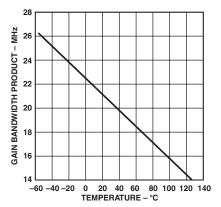

20 MHz Gain Bandwidth Product

THD = 0.0002% @ 1 kHz

Internally Compensated for Gains of +5 (or -4) or Greater

EXCELLENT DC PERFORMANCE

0.5 mV Max Offset Voltage

250 pA Max Input Bias Current

2000 V/mV Min Open Loop Gain

Available in Tape and Reel in Accordance with

**EIA-481A Standard**

**APPLICATIONS**

Sonar

**Photodiode and IR Detector Amplifiers**

**Accelerometers**

Low Noise Preamplifiers

**High Performance Audio**

#### PRODUCT DESCRIPTION

The AD745 is an ultralow noise, high-speed, FET input operational amplifier. It offers both the ultralow voltage noise and high speed generally associated with bipolar input op amps and the very low input currents of FET input devices. Its 20 MHz bandwidth and  $12.5~V/\mu s$  slew rate makes the AD745 an ideal

#### rige

#### REV. D

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

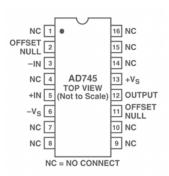

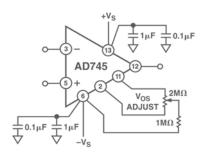

#### **CONNECTION DIAGRAM**

16-Lead SOIC (R) Package

amplifier for high-speed applications demanding low noise and high dc precision. Furthermore, the AD745 does not exhibit an output phase reversal.

The AD745 also has excellent dc performance with 250 pA maximum input bias current and 0.5 mV maximum offset voltage.

The internal compensation of the AD745 is optimized for higher gains, providing a much higher bandwidth and a faster slew rate. This makes the AD745 especially useful as a preamplifier where low level signals require an amplifier that provides both high amplification and wide bandwidth at these higher gains. The AD745 is available in two performance grades. The AD745J and AD745K are rated over the commercial temperature range of 0°C to 70°C, and are available in the 16-lead SOIC package.

Figure 2.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 2002

# AD745—SPECIFICATIONS

### AD745 ELECTRICAL CHARACTERISTICS (@ +25°C and ±15 V dc, unless otherwise noted.)

| Model                                                                                                                                | Conditions                                                                                                                                            | Min                               | AD745J<br>Typ                                     | Max                      | Min                        | AD745K<br>Typ                                     | Max                              | Unit                                                                                        |

|--------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|---------------------------------------------------|--------------------------|----------------------------|---------------------------------------------------|----------------------------------|---------------------------------------------------------------------------------------------|

| INPUT OFFSET VOLTAGE <sup>1</sup> Initial Offset Initial Offset vs. Temp. vs. Supply (PSRR) vs. Supply (PSRR)                        | $T_{MIN} \text{ to } T_{MAX}$ $T_{MIN} \text{ to } T_{MAX}$ $12 \text{ V to } 18 \text{ V}^2$ $T_{MIN} \text{ to } T_{MAX}$                           | 90<br>88                          | 0.25<br>2<br>96                                   | 1.0<br>1.5               | 100<br>98                  | 0.1<br>2<br>106<br>105                            | 0.5<br>1.0                       | mV<br>mV<br>μV/°C<br>dB<br>dB                                                               |

| INPUT BIAS CURRENT <sup>3</sup> Either Input Either Input @ $T_{MAX}$ Either Input Either Input, $V_S = \pm 5 \text{ V}$             | $V_{\rm CM} = 0 \text{ V}$ $V_{\rm CM} = 0 \text{ V}$ $V_{\rm CM} = +10 \text{ V}$ $V_{\rm CM} = 0 \text{ V}$                                         |                                   | 150<br>250<br>30                                  | 400<br>8.8<br>600<br>200 |                            | 150<br>250<br>30                                  | 250<br>5.5<br>400<br>125         | pA<br>nA<br>pA<br>pA                                                                        |

| INPUT OFFSET CURRENT Offset Current @ T <sub>MAX</sub>                                                                               | $V_{CM} = 0 V$ $V_{CM} = 0 V$                                                                                                                         |                                   | 40                                                | 150<br>2.2               |                            | 30                                                | 75<br>1.1                        | pA<br>nA                                                                                    |

| FREQUENCY RESPONSE Gain BW, Small Signal Full Power Response Slew Rate Settling Time to 0.01% Total Harmonic Distortion <sup>4</sup> | G = -4<br>$V_0 = 20 \text{ V p-p}$<br>G = -4<br>f = 1  kHz<br>G = -4                                                                                  |                                   | 20<br>120<br>12.5<br>5                            |                          |                            | 20<br>120<br>12.5<br>5                            |                                  | MHz<br>kHz<br>V/µs<br>µs                                                                    |

| INPUT IMPEDANCE Differential Common Mode                                                                                             |                                                                                                                                                       |                                   | $1 \times 10^{10} \  20$ $3 \times 10^{11} \  18$ |                          |                            | $1 \times 10^{10} \  20$ $3 \times 10^{11} \  18$ |                                  | Ω  pF<br>Ω  pF                                                                              |

| INPUT VOLTAGE RANGE Differential <sup>5</sup> Common-Mode Voltage Over Max Operating Range <sup>6</sup> Common-Mode Rejection Ratio  | $V_{CM} = \pm 10 \text{ V}$ $T_{MIN}$ to $T_{MAX}$                                                                                                    | -10<br>80<br>78                   | ±20<br>+13.3, -10.7                               | +12                      | -10<br>90<br>88            | ±20<br>+13.3, -10.7                               | +12                              | V<br>V<br>V<br>dB                                                                           |

| INPUT VOLTAGE NOISE                                                                                                                  | 0.1 to 10 Hz<br>f = 10 Hz<br>f = 100 Hz<br>f = 1 kHz<br>f = 10 kHz                                                                                    |                                   | 0.38<br>5.5<br>3.6<br>3.2<br>2.9                  | 5.0<br>4.0               |                            | 0.38<br>5.5<br>3.6<br>3.2<br>2.9                  | 1.0<br>10.0<br>6.0<br>5.0<br>4.0 | $\mu V p-p \\ nV/\sqrt{Hz} \\ nV/\sqrt{Hz} \\ nV/\sqrt{Hz} \\ nV/\sqrt{Hz} \\ nV/\sqrt{Hz}$ |

| INPUT CURRENT NOISE                                                                                                                  | f = 1 kHz                                                                                                                                             |                                   | 6.9                                               |                          |                            | 6.9                                               |                                  | fA/√ <u>Hz</u>                                                                              |

| OPEN LOOP GAIN                                                                                                                       | $\begin{aligned} &V_{O}=\pm 10 \text{ V} \\ &R_{LOAD} \geq 2 \text{ k}\Omega \\ &T_{MIN} \text{ to } T_{MAX} \\ &R_{LOAD}=600 \Omega \end{aligned}$   | 1000<br>800                       | 4000<br>1200                                      |                          | 2000<br>1800               | 4000<br>1200                                      |                                  | V/mV<br>V/mV<br>V/mV                                                                        |

| OUTPUT CHARACTERISTICS Voltage Current                                                                                               | $\begin{split} R_{LOAD} &\geq 600~\Omega \\ R_{LOAD} &\geq 600~\Omega \\ T_{MIN}~to~T_{MAX} \\ R_{LOAD} &\geq 2~k\Omega \\ Short~Circuit \end{split}$ | +13, -12<br>+12, -10<br>±12<br>20 | +13.6, -12.6<br>+13.8, -13.1<br>40                |                          | +13, -12<br>+12, -10<br>20 | +13.6, -12.6<br>+13.8, -13.1<br>40                |                                  | V<br>V<br>mA                                                                                |

| POWER SUPPLY Rated Performance Operating Range Quiescent Current                                                                     |                                                                                                                                                       | ±4.8                              | ±15                                               | ±18<br>10.0              | ±4.8                       | ±15                                               | ±18<br>10.0                      | V<br>V<br>mA                                                                                |

| TRANSISTOR COUNT                                                                                                                     | # of Transistors                                                                                                                                      |                                   | 50                                                |                          |                            | 50                                                |                                  |                                                                                             |

-2-REV. D

<sup>&</sup>lt;sup>1</sup>Input offset voltage specifications are guaranteed after five minutes of operations at  $T_A = 25^{\circ}C$ . <sup>2</sup>Test conditions:  $+V_S = 15 \text{ V}$ ,  $-V_S = 12 \text{ V}$  to 18 V and  $+V_S = 12 \text{ V}$  to +18 V,  $-V_S = 15 \text{ V}$ .

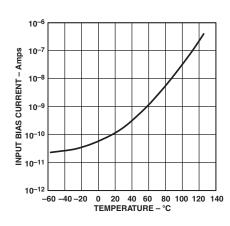

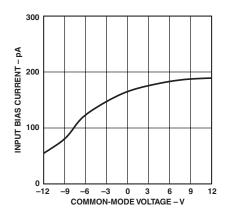

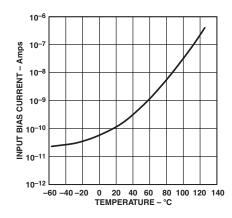

<sup>&</sup>lt;sup>3</sup>Bias current specifications are guaranteed maximum at either input after five minutes of operation at T<sub>A</sub> = 25°C. For higher temperature, the current doubles every 10°C.

$<sup>^4</sup>$ Gain =  $^4$ ,  $R_L$  = 2 k $\Omega$ ,  $C_L$  = 10 pF.  $^5$ Defined as voltage between inputs, such that neither exceeds  $\pm 10$  V from common.

<sup>&</sup>lt;sup>6</sup>The AD745 does not exhibit an output phase reversal when the negative common-mode limit is exceeded.

All min and max specifications are guaranteed.

Specifications subject to change without notice.

#### ABSOLUTE MAXIMUM RATINGS<sup>1</sup>

| Supply Voltage                                  |

|-------------------------------------------------|

| Internal Power Dissipation <sup>2</sup>         |

| SOIC Package 1.2 W                              |

| Input Voltage                                   |

| Output Short-Circuit Duration Indefinite        |

| Differential Input Voltage $+V_S$ and $-V_S$    |

| Storage Temperature Range (R)65°C to +125°C     |

| Operating Temperature Range                     |

| AD745J/K 0°C to 70°C                            |

| Lead Temperature Range (Soldering 60 sec) 300°C |

| NOTES                                           |

<sup>1</sup>Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability.

#### **ESD SUSCEPTIBILITY**

An ESD classification per method 3015.6 of MIL-STD-883C has been performed on the AD745, which is a class 1 device. Using an IMCS 5000 automated ESD tester, the two null pins will pass at voltages up to 1,000 volts, while all other pins will pass at voltages exceeding 2,500 volts.

#### **ORDERING GUIDE**

| Model      | Temperature Range | Package<br>Option* |

|------------|-------------------|--------------------|

| AD745JR-16 | 0°C to 70°C       | R-16               |

| AD745KR-16 | 0°C to 70°C       | R-16               |

<sup>\*</sup>R = Small Outline IC.

#### CAUTION\_

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD745 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high-energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

REV. D -3-

<sup>&</sup>lt;sup>2</sup>16-Pin Plastic SOIC Package:  $\theta_{JA} = 100^{\circ}\text{C/W}$ ,  $\theta_{JC} = 30^{\circ}\text{C/W}$

# AD745 —Typical Performance Characteristics (@ + 25°C, $V_s = \pm 15$ V, unless otherwise noted.)

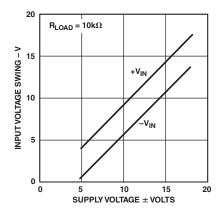

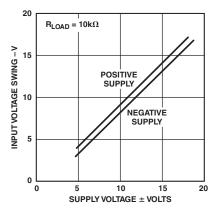

TPC 1. Input Voltage Swing vs. Supply Voltage

TPC 2. Output Voltage Swing vs. Supply Voltage

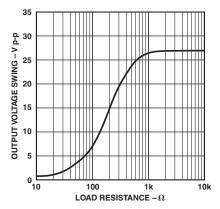

TPC 3. Output Voltage Swing vs. Load Resistance

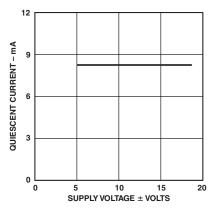

TPC 4. Quiescent Current vs. Supply Voltage

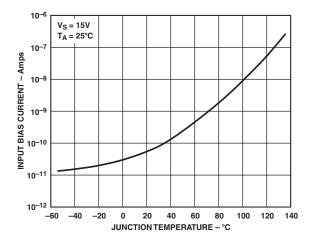

TPC 5. Input Bias Current vs. Temperature

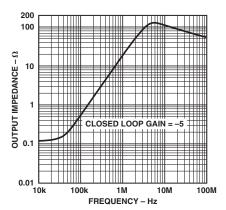

TPC 6. Output Impedance vs. Frequency

TPC 7. Input Bias Current vs. Common-Mode Voltage

TPC 8. Short Circuit Current Limit vs. Temperature

TPC 9. Gain Bandwidth Product vs. Temperature

-4- REV. D

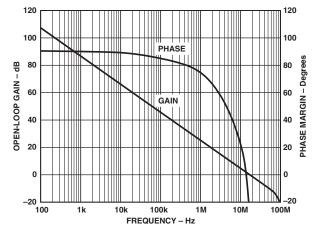

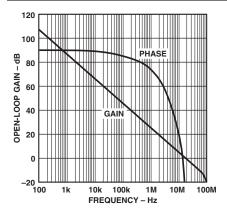

TPC 10. Open-Loop Gain and Phase vs. Frequency

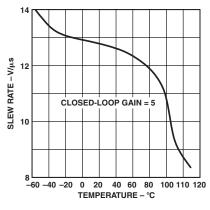

TPC 11. Slew Rate vs. Temperature

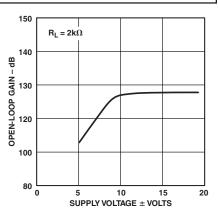

TPC 12. Open-Loop Gain vs. Supply Voltage

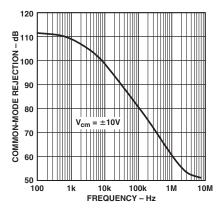

TPC 13. Common-Mode Rejection vs. Frequency

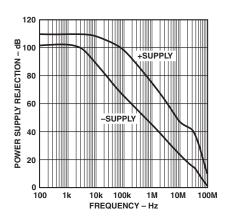

TPC 14. Power Supply Rejection vs. Frequency

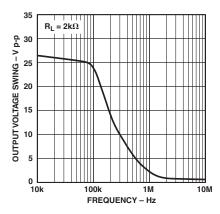

TPC 15. Large Signal Frequency Response

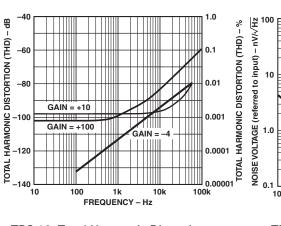

TPC 16. Total Harmonic Distortion vs. Frequency

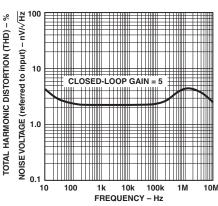

TPC 17. Input Noise Voltage Spectral Density

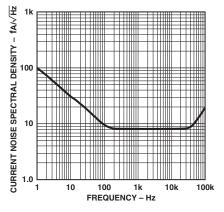

TPC 18. Input Noise Current Spectral Density

REV. D –5–

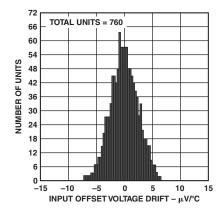

TPC 19. Distribution of Offset Voltage Drift.  $T_A = 25^{\circ}C$  to  $125^{\circ}C$

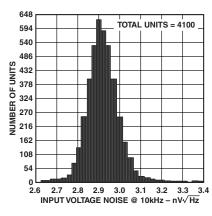

TPC 20. Typical Input Noise Voltage Distribution @ 10 kHz

TPC 21. Offset Null Configuration, 16-Lead Package Pinout

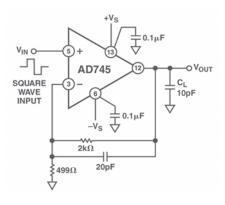

TPC 22a. Gain of 5 Follower, 16-Lead Package Pinout

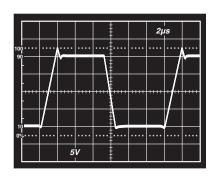

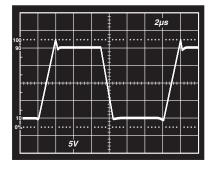

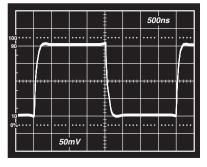

TPC 22b. Gain of 5 Follower Large Signal Pulse Response

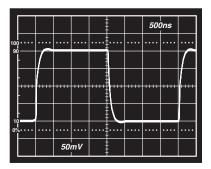

TPC 22c. Gain of 5 Follower Small Signal Pulse Response

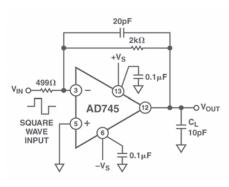

TPC 23a. Gain of 4 Inverter, 16-Lead Package Pinout

TPC 23b. Gain of 4 Inverter Large Signal Pulse Response

TPC 23c. Gain of 4 Inverter Small Signal Pulse Response

-6- REV. D

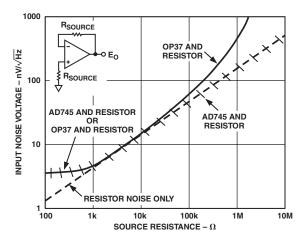

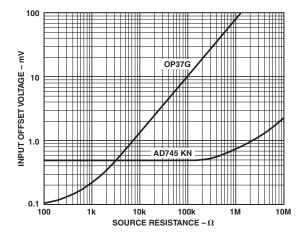

#### OP AMP PERFORMANCE JFET VERSUS BIPOLAR

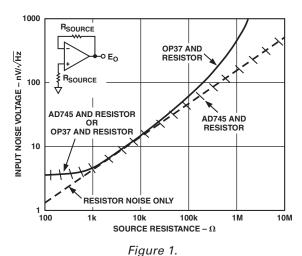

The AD745 offers the low input voltage noise of an industry standard bipolar opamp without its inherent input current errors. This is demonstrated in Figure 3, which compares input voltage noise vs. input source resistance of the OP37 and the AD745 opamps. From this figure, it is clear that at high source impedance the low current noise of the AD745 also provides lower total noise. It is also important to note that with the AD745 this noise reduction extends all the way down to low source impedances. The lower dc current errors of the AD745 also reduce errors due to offset and drift at high source impedances (Figure 4).

The internal compensation of the AD745 is optimized for higher gains, providing a much higher bandwidth and a faster slew rate. This makes the AD745 especially useful as a preamplifier, where low-level signals require an amplifier that provides both high amplification and wide bandwidth at these higher gains.

Figure 3. Total Input Noise Spectral Density @ 1 kHz vs. Source Resistance

Figure 4. Input Offset Voltage vs. Source Resistance

#### DESIGNING CIRCUITS FOR LOW NOISE

An opamp's input voltage noise performance is typically divided into two regions: flatband and low frequency noise. The AD745 offers excellent performance with respect to both. The figure of 2.9 nV/ $\sqrt{\text{Hz}}$  @ 10 kHz is excellent for a JFET input amplifier.

The 0.1 Hz to 10 Hz noise is typically 0.38 µV p-p. The user should pay careful attention to several design details to optimize low frequency noise performance. Random air currents can generate varying thermocouple voltages that appear as low frequency noise. Therefore, sensitive circuitry should be well shielded from air flow. Keeping absolute chip temperature low also reduces low frequency noise in two ways: first, the low frequency noise is strongly dependent on the ambient temperature and increases above 25°C. Second, since the gradient of temperature from the IC package to ambient is greater, the noise generated by random air currents, as previously mentioned, will be larger in magnitude. Chip temperature can be reduced both by operation at reduced supply voltages and by the use of a suitable clip-on heat sink, if possible.

Low frequency current noise can be computed from the magnitude of the dc bias current

$$\left(\widetilde{I}_n = \sqrt{2qI_B\Delta f}\right)$$

and increases below approximately 100 Hz with a 1/f power spectral density. For the AD745 the typical value of current noise is 6.9 fA/ $\sqrt{\text{Hz}}$  at 1 kHz. Using the formula:

$$\widetilde{I}_n = \sqrt{4kT/R\Delta f}$$

to compute the Johnson noise of a resistor, expressed as a current, one can see that the current noise of the AD745 is equivalent to that of a  $3.45 \times 10^8 \,\Omega$  source resistance.

At high frequencies, the current noise of a FET increases proportionately to frequency. This noise is due to the "real" part of the gate input impedance, which decreases with frequency. This noise component usually is not important, since the voltage noise of the amplifier impressed upon its input capacitance is an apparent current noise of approximately the same magnitude.

In any FET input amplifier, the current noise of the internal bias circuitry can be coupled externally via the gate-to-source capacitances and appears as input current noise. This noise is totally correlated at the inputs, so source impedance matching will tend to cancel out its effect. Both input resistance and input capacitance should be balanced whenever dealing with source capacitances of less than 300 pF in value.

#### LOW NOISE CHARGE AMPLIFIERS

As stated, the AD745 provides both low voltage and low current noise. This combination makes this device particularly suitable in applications requiring very high charge sensitivity, such as capacitive accelerometers and hydrophones. When dealing with a high source capacitance, it is useful to consider the total input charge uncertainty as a measure of system noise.

Charge (Q) is related to voltage and current by the simply stated fundamental relationships:

$$Q = CV$$

and  $I = \frac{dQ}{dt}$

As shown, voltage, current and charge noise can all be directly related. The change in open circuit voltage ( $\Delta V$ ) on a capacitor will equal the combination of the change in charge ( $\Delta Q/C$ ) and the change in capacitance with a built-in charge ( $Q/\Delta C$ ).

REV. D -7-

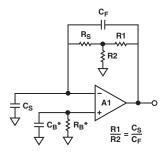

Figures 5 and 6 show two ways to buffer and amplify the output of a charge output transducer. Both require the use of an amplifier that has a very high input impedance, such as the AD745. Figure 5 shows a model of a charge amplifier circuit. Here, amplification depends on the principle of conservation of charge at the input of amplifier A1, which requires that the charge on capacitor  $C_S$  be transferred to capacitor  $C_F$ , thus yielding an output voltage of  $\Delta Q/C_F$ . The amplifiers input voltage noise will appear at the output amplified by the noise gain  $(1+(C_S/C_F))$  of the circuit.

Figure 5. A Charge Amplifier Circuit

Figure 6. Model for A High Z Follower with Gain

The second circuit, Figure 6, is simply a high impedance follower with gain. Here the noise gain (1 + (R1/R2)) is the same as the gain from the transducer to the output. Resistor  $R_B$ , in both circuits, is required as a dc bias current return.

There are three important sources of noise in these circuits. Amplifiers A1 and A2 contribute both voltage and current noise, while resistor  $R_{\rm B}$  contributes a current noise of:

$$\stackrel{\sim}{N} = \sqrt{4 k \frac{T}{R_P}} \Delta f$$

where:

$k = \text{Boltzman's Constant} = 1.381 \times 10^{-23} \text{ Joules/Kelvin}$

T = Absolute Temperature, Kelvin (0°C = 273.2 Kelvin)

$\Delta f$  = Bandwidth – in Hz (Assuming an Ideal "Brick Wall" Filter)

This must be root-sum-squared with the amplifier's own current noise.

Figure 5 shows that these two circuits have an identical frequency response and the same noise performance (provided that  $C_S/C_F = R1/R2$ ). One feature of the first circuit is that a "T" network is used to increase the effective resistance of  $R_B$  and improve the low frequency cutoff point by the same factor.

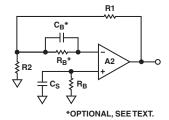

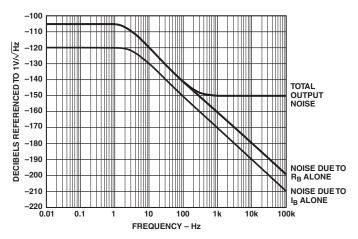

Figure 7. Noise at the Outputs of the Circuits of Figures 5 and 6. Gain = 10,  $C_S$  = 3000 pF,  $R_B$  = 22  $M\Omega$

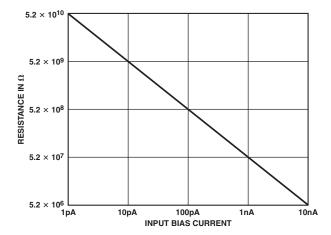

However, this does not change the noise contribution of  $R_B$  which, in this example, dominates at low frequencies. The graph of Figure 8 shows how to select an  $R_B$  large enough to minimize this resistor's contribution to overall circuit noise. When the equivalent current noise of  $R_B$  (( $\sqrt{4~kT}$ )/R) equals the noise of  $I_B$ ( $\sqrt{2qI_B}$ ), there is diminishing return in making  $R_B$  larger.

Figure 8. Graph of Resistance vs. Input Bias Current Where the Equivalent Noise  $\sqrt{4~kT/R}$ , Equals the Noise of the Bias Current  $I_B\left(\sqrt{2qI_B}\right)$

To maximize dc performance over temperature, the source resistances should be balanced on each input of the amplifier. This is represented by the optional resistor  $R_{\rm B}$  in Figures 5 and 6. As previously mentioned, for best noise performance care should be taken to also balance the source capacitance designated by  $C_{\rm B}$  The value for  $C_{\rm B}$  in Figure 5 would be equal to  $C_{\rm S}$  in Figure 6. At values of  $C_{\rm B}$  over 300 pF, there is a diminishing impact on noise; capacitor  $C_{\rm B}$  can then be simply a large mylar bypass capacitor of 0.01  $\mu F$  or greater.

# HOW CHIP PACKAGE TYPE AND POWER DISSIPATION AFFECT INPUT BIAS CURRENT

As with all JFET input amplifiers, the input bias current of the AD745 is a direct function of device junction temperature,  $I_B$  approximately doubling every 10°C. Figure 9 shows the relationship between bias current and junction temperature for the AD745. This graph shows that lowering the junction temperature will dramatically improve  $I_B$ .

Figure 9. Input Bias Current vs. Junction Temperature

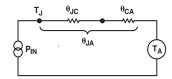

The dc thermal properties of an IC can be closely approximated by using the simple model of Figure 10 where current represents power dissipation, voltage represents temperature, and resistors represent thermal resistance ( $\theta$  in  $^{\circ}$ C/watt).

WHERE:

P<sub>IN</sub> = DEVICE DISSIPATION

T<sub>A</sub> = AMBIENT TEMPERATURE

$T_J = JUNCTIONTEMPERATURE$

$\theta_{JC}$  = THERMAL RESISTANCE – JUNCTION TO CASE  $\theta_{CA}$  = THERMAL RESISTANCE – CASE TO AMBIENT

Figure 10. Device Thermal Model

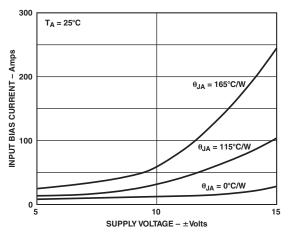

From this model  $T_J = T_A + \theta_{JA} \ P_{IN}$ . Therefore,  $I_B$  can be determined in a particular application by using Figure 9 together with the published data for  $\theta_{JA}$  and power dissipation. The user can modify  $\theta_{JA}$  by use of an appropriate clip-on heat sink such as the Aavid #5801. Figure 11 shows bias current versus supply voltage with  $\theta_{JA}$  as the third variable. This graph can be used to predict bias current after  $\theta_{JA}$  has been computed. Again bias current will double for every  $10^{\circ}\text{C}$ .

Figure 11. Input Bias Current vs. Supply Voltage for Various Values of  $\theta_{JA}$

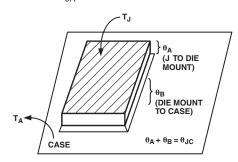

Figure 12. Breakdown of Various Package Thermal Resistance

# REDUCED POWER SUPPLY OPERATION FOR LOWER $I_{\rm B}$

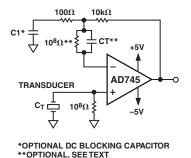

Reduced power supply operation lowers  $I_B$  in two ways: first, by lowering both the total power dissipation and, second, by reducing the basic gate-to-junction leakage (Figure 11). Figure 13 shows a 40 dB gain piezoelectric transducer amplifier, which operates without an ac coupling capacitor, over the  $-40^{\circ}$ C to  $+85^{\circ}$ C temperature range. If the optional coupling capacitor, C1, is used, this circuit will operate over the entire  $-55^{\circ}$ C to  $+125^{\circ}$ C temperature range.

Figure 13. A Piezoelectric Transducer

REV. D -9-

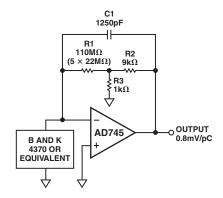

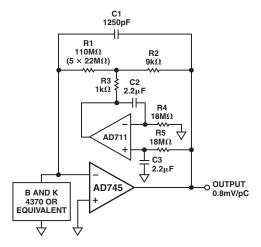

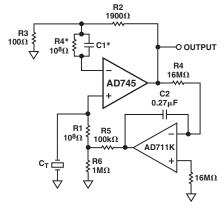

# TWO HIGH PERFORMANCE ACCELEROMETER AMPLIFIERS

Two of the most popular charge-out transducers are hydrophones and accelerometers. Precision accelerometers are typically calibrated for a charge output (pC/g).\* Figures 14 and 15 show two ways in which to configure the AD745 as a low noise charge amplifier for use with a wide variety of piezoelectric accelerometers. The input sensitivity of these circuits will be determined by the value of capacitor C1 and is equal to:

$$\Delta V_{OUT} = \frac{\Delta Q_{OUT}}{C1}$$

The ratio of capacitor C1 to the internal capacitance  $(C_T)$  of the transducer determines the noise gain of this circuit  $(1 + C_T/C1)$ . The amplifiers voltage noise will appear at its output amplified by this amount. The low frequency bandwidth of these circuits will be dependent on the value of resistor R1. If a "T" network is used, the effective value is: R1 (1 + R2/R3).

\*pC = Picocoulombs g = Earth's Gravitational Constant

Figure 14. A Basic Accelerometer Circuit

Figure 15. An Accelerometer Circuit Employing a DC Servo Amplifier

A dc servo loop (Figure 15) can be used to assure a dc output <10 mV, without the need for a large compensating resistor when dealing with bias currents as large as 100 nA. For optimal

low frequency performance, the time constant of the servo loop (R4C2 = R5C3) should be:

$$Time\ Constant \ge 10\ R1 \left(1 + \frac{R2}{R3}\right)C1$$

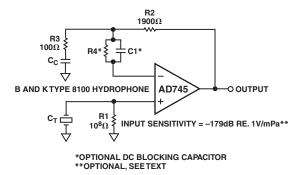

#### A LOW NOISE HYDROPHONE AMPLIFIER

Hydrophones are usually calibrated in the voltage-out mode. The circuit of Figures 16 can be used to amplify the output of a typical hydrophone. If the optional ac coupling capacitor  $C_C$  is used, the circuit will have a low frequency cutoff determined by an RC time constant equal to:

$$Time\ Constant \geq 10\ R1 \frac{1}{2\pi \times C_C \times 100\ \Omega}$$

where the dc gain is 1 and the gain above the low frequency cutoff (1/(2 $\pi$  C<sub>C</sub>(100  $\Omega$ ))) is equal to (1 + R2/R3). The circuit of Figure 17 uses a dc servo loop to keep the dc output at 0 V and to maintain full dynamic range for I<sub>B</sub>'s up to 100 nA. The time constant of R7 and C1 should be larger than that of R1 and C<sub>T</sub> for a smooth low frequency response.

Figure 16. A Low Noise Hydrophone Amplifier

The transducer shown has a source capacitance of 7500 pF. For smaller transducer capacitances ( $\leq$ 300 pF), lowest noise can be achieved by adding a parallel RC network (R4 = R1, C1 =  $C_T$ ) in series with the inverting input of the AD745.

DC OUTPUT ≤ 1mV FOR IB (AD745) ≤ 100nA \*OPTIONAL, SEETEXT

Figure 17. A Hydrophone Amplifier Incorporating a DC Servo Loop

–10– REV. D

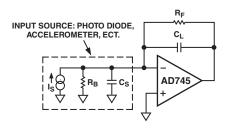

#### **DESIGN CONSIDERATIONS FOR I-TO-V CONVERTERS**

There are some simple rules of thumb when designing an I-V converter where there is significant source capacitance (as with a photodiode) and bandwidth needs to be optimized. Consider the circuit of Figure 18. The high frequency noise gain  $(1+C_{\rm S}/C_{\rm L})$  is usually greater than five, so the AD745, with its higher slew rate and bandwidth is ideally suited to this application.

Here both the low current and low voltage noise of the AD745 can be taken advantage of, since it is desirable in some instances to have a large  $R_{\rm F}$  (which increases sensitivity to input current noise) and, at the same time, operate the amplifier at high noise gain.

Figure 18. A Model for an I-to-V Converter

In this circuit, the  $R_F$   $C_S$  time constant limits the practical bandwidth over which flat response can be obtained, in fact:

$$f_B \approx \sqrt{\frac{f_C}{2\pi R_F C_S}}$$

where:

$f_B$  = signal bandwidth

$f_C$  = gain bandwidth product of the amplifier

With  $C_L\approx 1/(2~\pi R_F~C_S)$  the net response can be adjusted to a provide a two pole system with optimal flatness that has a corner frequency of  $f_B$ . Capacitor  $C_L$  adjusts the damping of the circuit's response. Note that bandwidth and sensitivity are directly traded off against each other via the selection of  $R_F$ . For example, a photodiode with  $C_S=300~pF$  and  $R_F=100~k\Omega$  will have a maximum bandwidth of 360 kHz when capacitor  $C_L\approx 4.5~pF$ . Conversely, if only a 100 kHz bandwidth were required, then the maximum value of  $R_F$  would be 360 k $\Omega$  and that of capacitor  $C_L$  still  $\approx 4.5~pF$ .

In either case, the AD745 provides impedance transformation, the effective transresistance, i.e., the I/V conversion gain, may be augmented with further gain. A wideband low noise amplifier such as the AD829 is recommended in this application.

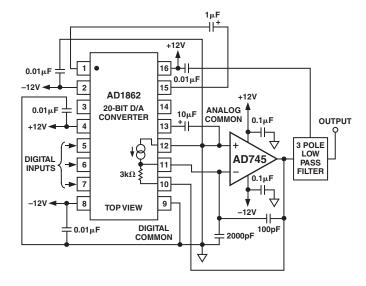

This principle can also be used to apply the AD745 in a high performance audio application. Figure 19 shows that an I-V converter of a high performance DAC, here the AD1862, can be designed to take advantage of the low voltage noise of the AD745 (2.9 nV/ $\sqrt{\rm Hz}$ ) as well as the high slew rate and bandwidth provided by decompensation. This circuit, with component values shown, has a 12 dB/octave rolloff at 728 kHz, with a passband ripple of less than 0.001 dB and a phase deviation of less than 2 degrees @ 20 kHz.

Figure 19. A High Performance Audio DAC Circuit

An important feature of this circuit is that high frequency energy, such as clock feedthrough, is shunted to common via a high quality capacitor and not the output stage of the amplifier, greatly reducing the error signal at the input of the amplifier and subsequent opportunities for intermodulation distortions.

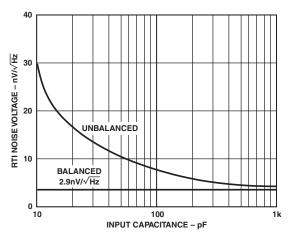

Figure 20. RTI Noise Voltage vs. Input Capacitance

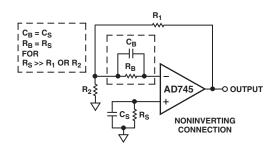

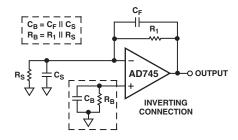

### **BALANCING SOURCE IMPEDANCES**

As mentioned previously, it is good practice to balance the source impedances (both resistive and reactive) as seen by the inputs of the AD745. Balancing the resistive components will optimize dc performance over temperature because balancing will mitigate the effects of any bias current errors. Balancing input capacitance will minimize ac response errors due to the amplifier's input capacitance and, as shown in Figure 20, noise performance will be optimized. Figure 21 shows the required external components for noninverting (A) and inverting (B) configurations.

REV. D –11–

Figure 40. Optional External Components for Balancing Source Impedances

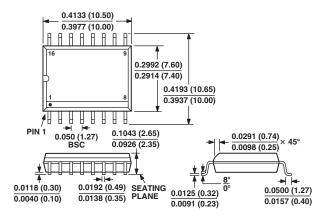

#### **OUTLINE DIMENSIONS**

Dimensions shown in inches and (mm).

#### 16-Lead SOIC (R) Package

# **Revision History**

| Location                                                                                     | Page      |

|----------------------------------------------------------------------------------------------|-----------|

| Data Sheet changed from REV. C to REV. D.                                                    |           |

| Deleted 8-Lead Plastic Mini-DIP (N) and 8-Lead Cerdip (Q) Packages from CONNECTION DIAGRAM . | 1         |

| Edits to PRODUCT DESCRIPTION                                                                 | 1         |

| Edits to ELECTRICAL CHARACTERISTICS                                                          | 2         |

| Edits to ABSOLUTE MAXIMUM RATINGS                                                            |           |

| Edits to ORDERING GUIDE                                                                      |           |

| Deleted to METALIZATION PHOTOGRAPH                                                           |           |

| Deleted text from HOW CHIP PACKAGE TYPE AND POWER DISSIPATION AFFECT INPUT BIAS C            | CURRENT 9 |

| Deleted 8-Lead Plastic Mini-DIP (N) and 8-Lead Cerdip (Q) Packages from OUTLINE DIMENSIONS   | 12        |