## Dual Precision JFET-Input Operational Amplifier

**OP215**

**FEATURES**

High Slew Rate: 10 V/µs Min

Fast Settling Time: 0.9 μs to 0.1% Type Low Input Offset Voltage Drift: 10 μV/°C Max

Wide Bandwidth: 3.5 MHz Min

Temperature-Compensated Input Bias Currents Guaranteed Input Bias Current: 18 nA Max (125°C) Bias Current Specified Warmed Up over Temperature Low Input Noise Current: 0.01 pA/√Hz Type High Common-Mode Rejection Ratio 86 dB Min Pin Compatible with Standard Dual Pinouts Models with MIL-STD-883 Class B Processing Available

#### **GENERAL DESCRIPTION**

The OP215 offers the proven JFET-input performance advantages of high speed and low input bias current with the tracking and convenience advantages of a dual op amp configuration.

Low input offset voltages, low input currents, and low drift are featured in these high-speed amplifiers.

On-chip zener-zap trimming is used to achieve low  $V_{OS}$ , while a bias-current compensation scheme gives a low input bias current

at elevated temperature. Thus, the OP215 features an input bias current of 1.4 nA at 70°C ambient (not junction) temperature which greatly extends the application usefulness of this device.

Applications include high-speed amplifiers for current output DACs, active filters, sample-and-hold buffers, and photocell amplifiers. For additional precision JFET op amps, see the OP249 and AD712 data sheets.

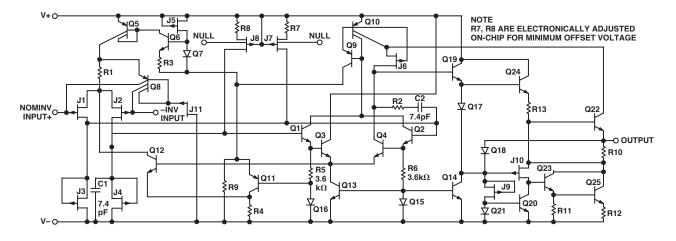

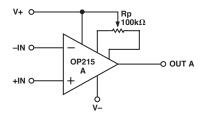

Figure 1. Simplified Schematic (1/2 OP215)

### **OP215—SPECIFICATIONS**

### **ELECTRICAL CHARACTERISTICS** (at $V_S=\pm 15~V,~T_A=25^{\circ}C,~unless~otherwise~noted.)$

|                                        |                  |                                                                                                |               | OP215E            |              |               | OP215G            |              |                                |

|----------------------------------------|------------------|------------------------------------------------------------------------------------------------|---------------|-------------------|--------------|---------------|-------------------|--------------|--------------------------------|

| Parameter                              | Symbol           | Conditions                                                                                     | Min           | Type              | Max          | Min           | Type              | Max          | Unit                           |

| Input Offset Voltage                   | Vos              | $R_S = 50 \Omega$<br>'G' Grade                                                                 |               | 0.2               | 1.0          |               | 2.0<br>2.5        | 4.0<br>6.0   | mV<br>mV                       |

| Input Offset Current <sup>1</sup>      | I <sub>OS</sub>  | T <sub>j</sub> = 25°C<br>Device Operating                                                      |               | 3<br>5            | 50<br>100    |               | 3<br>5            | 100<br>200   | pA<br>pA                       |

| Input Bias Current <sup>1</sup>        | $I_{\mathrm{B}}$ | $T_j = 25^{\circ}C$<br>Device Operating                                                        |               | ±15<br>±18        | ±100<br>±300 |               | ±15<br>±18        | ±300<br>±600 | pA<br>pA                       |

| Input Resistance                       | R <sub>IN</sub>  |                                                                                                |               | 101,2             |              |               | 101,2             |              | Ω                              |

| Large-Signal Voltage<br>Gain           | A <sub>VO</sub>  | $R_{L} \ge 2 \text{ k}\Omega,$ $V_{O} = \pm 10 \text{ V}$                                      | 150           | 500               |              | 50            | 200               |              | V/mV                           |

| Output Voltage Swing                   | Vo               | $R_{L} = 10 \text{ k}\Omega$ $R_{L} = 2 \text{ k}\Omega$                                       | ±12<br>±11    | ±13<br>±12.7      |              | ±12<br>±11    | ±13<br>±12.7      |              | V<br>V                         |

| Supply Current                         | $I_{SY}$         | 'G' Grade                                                                                      |               | 6.0               | 8.5          |               | 7.0<br>7.0        | 10.0<br>12.0 | mA<br>mA                       |

| Slew Rate                              | SR               | $A_{VCL} = 1$                                                                                  | 10            | 18                |              | 5             | 15                |              | V/µs                           |

| Gain Bandwidth<br>Product <sup>3</sup> | GBW              |                                                                                                | 3.5           | 5.7               |              | 3.0           | 5.4               |              | MHz                            |

| Closed-Loop Bandwidth                  | CLBW             | $A_{VCL} = 1$                                                                                  |               | 13                |              |               | 12                |              | MHz                            |

| Setting Time                           | $t_{S}$          | To 0.01%<br>To 0.05% <sup>2</sup><br>To 0.10%                                                  |               | 2.3<br>1.1<br>0.9 |              |               | 2.4<br>1.2<br>1.0 |              | µs<br>µs<br>µs                 |

| Input Voltage Range                    | IVR              |                                                                                                | 10.2<br>-10.2 | 14.8<br>-11.5     |              | 10.1<br>-10.1 | 14.8<br>-11.5     |              | V<br>V                         |

| Common-Mode<br>Rejection Ratio         | CMRR             | $V_{CM} = \pm IVR$<br>E, G Grades                                                              | 82            | 100               |              | 80            | 96                |              | dB                             |

| Power Supply Rejection<br>Ratio        | PSRR             | $V_S = \pm 10 \text{ V to } \pm 16 \text{ V}$<br>$V_S = \pm 10 \text{ V to } \pm 15 \text{ V}$ |               | 10                | 51           |               | 16                | 100          | μV/V<br>μV/V                   |

| Input Noise Voltage<br>Density         | θn               | f <sub>O</sub> = 100 Hz<br>f <sub>O</sub> = 1,000 Hz                                           |               | 20<br>15          |              |               | 20<br>15          |              | $nV/\sqrt{Hz} \\ nV/\sqrt{Hz}$ |

| Input Noise Current<br>Density         | In               | f <sub>O</sub> = 100 Hz<br>f <sub>O</sub> = 1,000 Hz                                           |               | 0.01<br>0.01      |              |               | 0.01<br>0.01      |              | $pA/\sqrt{Hz}$ $pA/\sqrt{Hz}$  |

| Input Capacitance                      | C <sub>IN</sub>  |                                                                                                |               | 3                 |              |               | 3                 |              | pF                             |

#### NOTES

-2- REV. A

<sup>&</sup>lt;sup>1</sup>Input bias current is specified for two different conditions. The  $T_j = 25^{\circ}\text{C}$  specification is with the junction at ambient temperature; the device operating specification is with the device operating in a warmed up condition at  $25^{\circ}\text{C}$  ambient. The warmed up bias-current value is correlated to the junction temperature value via the curves of  $I_s$  versus  $T_j$  and  $I_s$  versus  $T_A$ . PMI has a bias-current compensation circuit that gives improved bias current and bias current over temperature versus standard JFET input op amps.  $I_s$  and  $I_{OS}$  are measured at  $V_{CM} = 0$ .

<sup>&</sup>lt;sup>2</sup>Setting time is defined here for a unity gain inverter connection using  $2 k\Omega$  resistors. It is the time required for the error voltage (the voltage at the inverting input pin on the amplifier) to settle to within a specified percent of its final value from the time a 10 V step input is applied to the inverter. See setting time test circuit.

<sup>3</sup>Sample tested.

Specifications are subject to change without notice.

## **SPECIFICATIONS**

# **ELECTRICAL CHARACTERISTICS** (at $V_S=\pm 15$ V, $0^{\circ}C \le T_A \le 70^{\circ}C$ for E Grade, $-40^{\circ}C \le T_A \le +85^{\circ}C$ for G Grade, unless otherwise noted.)

|                                                                                                   |                                         |                                                                                                | (             | OP215E          |                |               | OP215G         |              |                |

|---------------------------------------------------------------------------------------------------|-----------------------------------------|------------------------------------------------------------------------------------------------|---------------|-----------------|----------------|---------------|----------------|--------------|----------------|

| Parameter                                                                                         | Symbol                                  | Conditions                                                                                     | Min           | Type            | Max            | Min           | Type           | Max          | Unit           |

| Input Offset Voltage                                                                              | V <sub>OS</sub>                         | $R_S = 50 \Omega$                                                                              |               | 0.4             | 1.65           |               | 3.5            | 8.0          | mV             |

| Average Input Offset<br>Voltage Drift<br>Without External Trim <sup>1</sup><br>With External Trim | TCV <sub>OS</sub><br>TCV <sub>OSn</sub> | $R_P = 100 \text{ k}\Omega$                                                                    |               | 3 3             | 15             |               | 6<br>4         |              | μV/°C<br>μV/°C |

| Input Offset Current <sup>2</sup>                                                                 | I <sub>OS</sub>                         | $T_{\rm j}$ = 70°C<br>$T_{\rm A}$ = 70°C<br>Device Operating                                   |               | 0.06<br>0.08    | 0.45<br>0.80   |               | 0.08<br>0.10   | 0.65<br>1.2  | nA<br>nA       |

| Input Bias Current <sup>2</sup>                                                                   | $I_S$                                   | $T_{\rm j}$ = 70°C<br>$T_{\rm A}$ = 70°C<br>Device Operating                                   |               | ±0.12<br>±0.16  | ±0.70<br>±1.40 |               | ±0.14<br>±0.19 | ±0.9<br>±1.8 | nA<br>nA       |

| Input Voltage Range                                                                               | IVR                                     |                                                                                                | 10.2<br>-10.2 | $14.7 \\ -11.4$ |                | 10.1<br>-10.1 | 14.7<br>-11.3  |              | V<br>V         |

| Common-Mode<br>Rejection Ratio                                                                    | CMRR                                    | $V_{CM} = \pm IVR$                                                                             | 80            | 98              |                | 76            | 94             |              | dB             |

| Power Supply Rejection<br>Ratio                                                                   | PSRR                                    | $V_S = \pm 10 \text{ V to } \pm 16 \text{ V}$<br>$V_S = \pm 10 \text{ V to } \pm 15 \text{ V}$ |               | 13              | 100            |               | 20             | 159          | μV/V           |

| Large-Signal<br>Voltage Gain                                                                      | A <sub>VO</sub>                         | $R_{L} \ge 2 k\Omega$ $V_{O} = \pm 10 V$                                                       | 50            | 180             |                | 35            | 130            |              | V/mV           |

| Output Voltage Swing                                                                              | Vo                                      | $R_{\rm L} \ge 10 \ {\rm k}\Omega$                                                             | ±12           | ±13             |                | ±12           | ±13            |              | V              |

#### NOTES

REV. A -3-

<sup>&</sup>lt;sup>1</sup>Sample tested.

<sup>&</sup>lt;sup>2</sup>Input bias current is specified for two different conditions. The  $T_j = 25^{\circ}\text{C}$  specification is with the junction at ambient temperature; the Device Operating specification is with the device operating in a warmed up condition at  $25^{\circ}\text{C}$  ambient. The warmed up bias-current value is correlated to the junction temperature value via the curves of  $I_S$  versus  $T_j$  and  $I_S$  versus  $T_A$ . PMI has a bias-current compensation circuit that gives improved bias current and bias current over temperature versus standard JFET input op amps.  $I_S$  and  $I_{OS}$  are measured at  $V_{CM} = 0$ .

Specifications are subject to change without notice.

### **OP215**

#### ABSOLUTE MAXIMUM RATINGS<sup>1</sup>

| 112002012111111111111111111111111111111             |

|-----------------------------------------------------|

| Supply Voltage                                      |

| OP215E, OP215G ±18 V                                |

| Operating Temperature Range                         |

| OP215E +0°C to +70°C                                |

| OP215G40°C to +85°C                                 |

| Maximum Junction Temperature (T <sub>i</sub> )150°C |

| Differential Input Voltage                          |

| OP215E                                              |

| OP215G±30 V                                         |

| Input Voltage <sup>2</sup>                          |

| OP215E±20 V                                         |

| OP215G±16 V                                         |

| Output Short-Circuit Duration Indefinite            |

| Storage Temperature Range65°C to +150°C             |

| Lead Temperature (Soldering, 60 sec)300°C           |

| Junction Temperature ( $T_i$ )65°C to +150°C        |

| NOTES                                               |

<sup>&</sup>lt;sup>1</sup>Absolute maximum ratings apply to packaged parts, unless otherwise noted.

| Package Type            | θ <sub>JA</sub> * | $\theta_{ m JC}$ | Unit |

|-------------------------|-------------------|------------------|------|

| 8-Lead Hermetic DIP (Z) | 134               | 12               | °C/W |

| 8-Lead Plastic DIP (P)  | 96                | 37               | °C/W |

<sup>\*</sup> $\theta_{JA}$  is specified for worst-case mounting conditions, i.e.,  $\theta_{JA}$  is specified for device in socket for CerDIP and P-DIP packages.

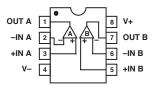

#### PIN CONFIGURATION

#### ORDERING INFORMATION1

| Model                | Package<br>Type    | Temperature<br>Range | $T_A = 25^{\circ}C$ ,<br>$V_{OS} Max (mV)$ |

|----------------------|--------------------|----------------------|--------------------------------------------|

| OP215EZ <sup>2</sup> | 8-Lead CerDIP      | COM                  | 1.0                                        |

| $OP215GP^2$          | 8-Lead Plastic DIP | XIND                 | 6.0                                        |

For military processed devices, please refer to the standard microcircuit drawing (SMD) available at www.dscc.dla.mil/programs/milspec/default.asp

| SMD Part Number             | ADI Equivalent |

|-----------------------------|----------------|

| 5962-8853801GA <sup>2</sup> | OP215AJMDA     |

| 5962-8853801PA              | OP215AZMDA     |

| 5962-8838032A <sup>2</sup>  | OP215BRCMDA    |

#### NOTES

#### CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the OP215 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high-energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

-4- REV. A

<sup>&</sup>lt;sup>2</sup>Unless otherwise specified, the absolute maximum negative input voltage is equal to one volt more positive than the negative power supply voltage.

<sup>&</sup>lt;sup>1</sup>Burn-in is available on commercial and industrial temperature range parts in CerDIP and plastic DIP packages.

<sup>&</sup>lt;sup>2</sup>Not for new design, obsolete April 2002.

### **Typical Performance Characteristics—OP215**

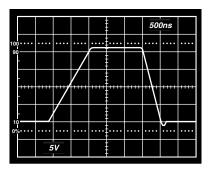

TPC 1. Large-Signal Transient Response

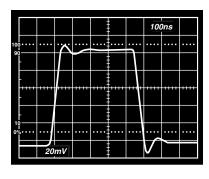

TPC 2. Small-Signal Transient Response

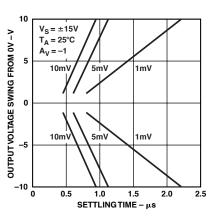

TPC 3. Settling Time

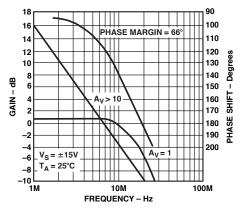

TPC 4. Closed-Loop Bandwidth and Phase Shift vs. Frequency

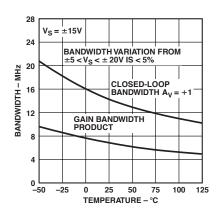

TPC 5. Bandwidth vs. Temperature

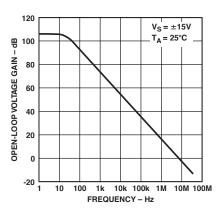

TPC 6. Open-Loop Frequency Response

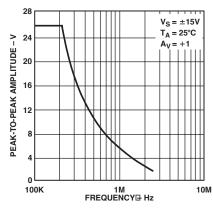

TPC 7. Maximum Output Swing vs. Frequency

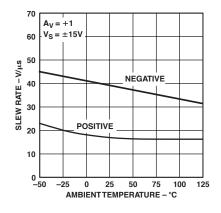

TPC 8. Slew Rate vs. Temperature

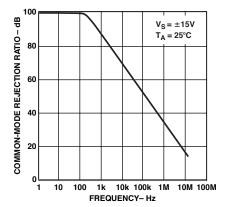

TPC 9. Common-Mode Rejection Ratio vs. Frequency

REV. A -5-

### **OP215**

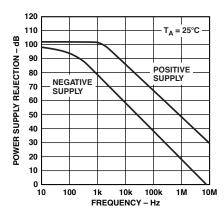

TPC 10. Power Supply Rejection vs. Frequency

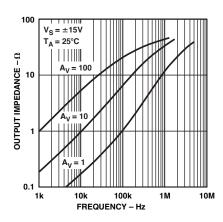

TPC 11. Output Impedance vs. Frequency

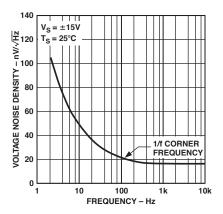

TPC 12. Voltage Noise Density vs. Frequency

#### **BASIC CONNECTIONS**

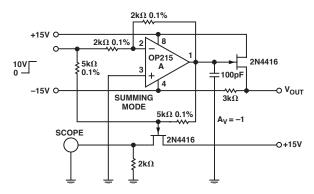

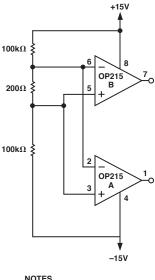

Figure 2. Settling Time Test Circuit

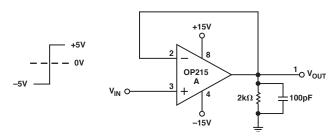

Figure 3. Slew Rate Test Circuit

NOTE  $V_{OS}\,\text{CAN BE TRIMMED WITH POTENTIOMETERS RANGING FROM 10 k\Omega TO 1 M\Omega. FOR MOST UNITS TCV_{OS} WILL BE MINIMUM WHEN <math display="inline">V_{OS}\,\text{IS ADJUSTED WITH A 100k}\Omega$  POTENTIOMETER.

Figure 4. Input Offset Voltage Nulling

#### APPLICATIONS INFORMATION

#### **Dynamic Operating Considerations**

As with most amplifiers, care should be taken with lead dress, component placement, and supply de-coupling in order to ensure stability. For example, resistors from the output to an input should be placed with the body close to the input to minimize "pick up" and maximize the frequency of the feedback pole by minimizing the capacitance from the input to ground.

A feedback pole is created when the feedback around any amplifier is resistive. The parallel resistance and capacitance from the input of the device (usually the inverting input) to ac ground sets the frequency of the pole. In many instances, the frequency of this pole is much greater than the expected 3 dB frequency of the closed-loop gain and, consequently, there is negligible effect on stability margin. However, if the feedback pole is less than approximately six times the expected 3 dB frequency, a lead capacitor should be placed from the output to the negative input of the op amp. The value of the added capacitor should be such that the RC time constant of this capacitor and the resistance it parallels is greater than, or equal to, the original feedback pole time constant.

#### **BASIC CONNECTIONS**

NOTES 1.  $T_A = 125^{\circ}\text{C}$  TO  $150^{\circ}\text{C}$  2. RESISTORS ARE TYPE RN55D,  $\pm$  1%

Figure 5. Burn-In Circuit

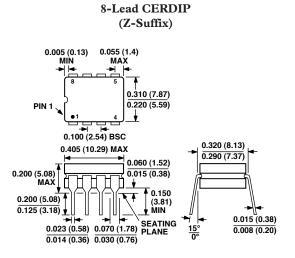

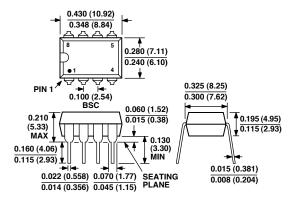

#### **OUTLINE DIMENSIONS**

Dimensions shown in inches and (mm).

### 8-Lead Plastic DIP (P-Suffix)

REV. A -7-

## **OP215**

# **Revision History**

| Location                                   | Page                                                                                                                                                                                   |

|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data Sheet changed from REV. 0 to REV. A.  |                                                                                                                                                                                        |

| Edits to GENERAL DESCRIPTION               | $\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots$ |

| Edits to ELECTRICAL CHARACTERISTICS        |                                                                                                                                                                                        |

| Edits to ORDERING INFORMATION              |                                                                                                                                                                                        |

| Edits to PIN CONNECTIONS                   |                                                                                                                                                                                        |

| Edits to ABSOLUTE MAXIMUM RATINGS          |                                                                                                                                                                                        |

| Edits to PACKAGE TYPE                      |                                                                                                                                                                                        |

| Deleted WAFER TEST LIMITS                  |                                                                                                                                                                                        |

| Deleted DICE CHARACTERISTICS               |                                                                                                                                                                                        |

| Deleted TYPICAL ELECTRICAL CHARACTERISTICS |                                                                                                                                                                                        |

| Edits to BURN-IN CIRCUIT figure            |                                                                                                                                                                                        |