# Power Management & Drives

**Power Management & Drives**

| Revision <b>F</b> | listory: December 2009                       | Version 2.2 |

|-------------------|----------------------------------------------|-------------|

| Previous V        | ersion: 2.1                                  |             |

| Page              | Subjects (major changes since last revision) |             |

| 6                 | 2.2.3 Watchdog Timer                         |             |

| 14                | 4.4.6 Dynamic Characteristics                |             |

|                   |                                              |             |

|                   |                                              |             |

|                   |                                              |             |

|                   |                                              |             |

|                   |                                              |             |

|                   |                                              |             |

|                   |                                              |             |

|                   |                                              |             |

|                   |                                              |             |

|                   |                                              |             |

|                   |                                              |             |

|                   |                                              |             |

|                   |                                              |             |

|                   |                                              |             |

Edition 2009-12-03

Published by Infineon Technologies AG, Campeon 1-12, 85579 Neubiberg, Germany © Infineon Technologies AG 2010. All Rights Reserved.

#### Attention please!

The information herein is given to describe certain components and shall not be considered as a guarantee of characteristics. Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

#### **Information**

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office (www.infineon.com).

## Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

# EICEDRIVER<sup>TM</sup>

## 1ED020I12-F

## **Single IGBT Driver IC**

## **Product Highlights**

- · Coreless transformer isolated driver

- Galvanic Insulation

- Integrated protection features

- Suitable for operation at high ambient temperature

- Cost effective technology

- Approvals: DIN EN 60747-5-2, UL1577

## **Features**

- Single channel isolated IGBT Driver

- For 600V/1200V IGBTs

- 2A rail-to-rail output

- Vcesat-detection

- Active Miller Clamp

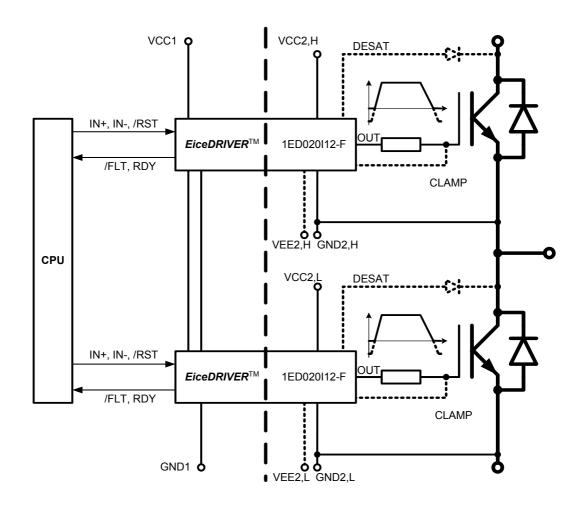

# Typical Application

- AC-Drives

- UPS-Systems

- Welding

Figure 1: Typical Application

| Туре        |  | Gate drive current | Package      |  |  |

|-------------|--|--------------------|--------------|--|--|

| 1ED020I12-F |  | +/- 2A             | PG-DSO-16-15 |  |  |

|             |  |                    |              |  |  |

Datasheet 3 Version 2.2, 2009-12-03

| Table       | e of Contents                                                 | Page |

|-------------|---------------------------------------------------------------|------|

| 1           | Blockdiagram and Application                                  | 5    |

| 2           | Functional Description                                        | 6    |

| 2.1         | Introduction                                                  |      |

| 2.2         | Internal Protection Features                                  |      |

| 2.2.1       | Undervoltage Lockout (UVLO)                                   | 6    |

| 2.2.2       | READY status output                                           | 6    |

| 2.2.3       | Watchdog Timer                                                | 6    |

| 2.2.4       | Active Shut-Down                                              | 6    |

| 2.3         | Non-Inverting and Inverting Inputs                            | 6    |

| 2.4         | Driver Output                                                 | 6    |

| 2.5         | External Protection Features                                  |      |

| 2.5.1       | Desaturation Protection                                       | 7    |

| 2.5.2       | Active Miller Clamping                                        | 7    |

| 2.5.3       | Short Circuit Clamping                                        |      |

| 2.6         | RESET                                                         |      |

| 2           | Pin Configuration and Functionality                           | 0    |

| <b>3</b> .1 | ·                                                             |      |

| 3.2         | Pin Configuration Pin Functionality                           |      |

| 3.2         | •                                                             |      |

| 4           | Electrical Parameters                                         |      |

| 4.1         | Absolute Maximum Ratings                                      |      |

| 4.2         | Operating Parameters                                          |      |

| 4.3         | Recommended Operating Parameters                              |      |

| 4.4         | Electrical Characteristics                                    |      |

| 4.4.1       | Voltage Supply                                                |      |

| 4.4.2       | Logic Input and Output                                        | 12   |

| 4.4.3       | Gate Driver                                                   |      |

| 4.4.4       | Active Miller Clamp                                           |      |

| 4.4.5       | Short Circuit Clamping                                        | 14   |

| 4.4.6       | Dynamic Characteristics                                       |      |

| 4.4.7       | Desaturation protection                                       |      |

| 4.4.8       | Active Shut Down                                              | 15   |

| 5           | Insulation Characteristics                                    | 16   |

| 5.1         | DIN EN 60747-5-2 (VDE 0884 Teil 2): 2003-01. Basic Insulation |      |

| 5.2         | UL 1577                                                       |      |

| 5.3         | Reliability                                                   |      |

|             |                                                               |      |

| 6           | Timing Diagrams                                               |      |

| 7           | Package Outlines                                              |      |

| 8           | Application Notes                                             |      |

| 8.1         | Reference Layout for Thermal Data                             |      |

| 8.2         | Printed Circuit Board Guidelines                              | 20   |

## 1 Blockdiagram and Application

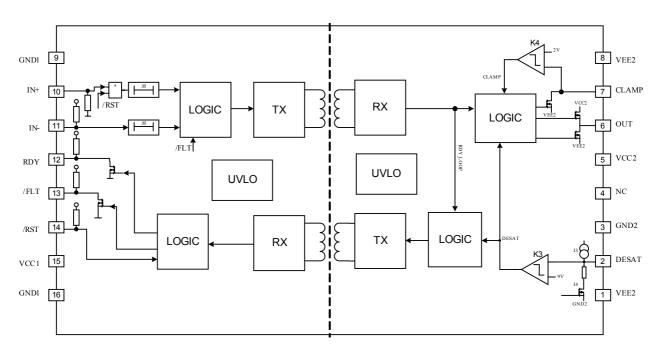

Figure 2: Blockdiagram 1ED020I12-F

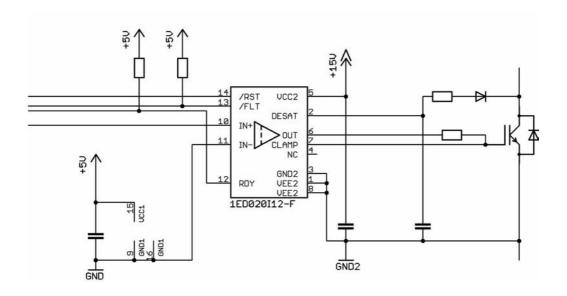

Figure 3: Application example

Datasheet 5 Version 2.2, 2009-12-03

## **2** Functional Description

#### 2.1 Introduction

The 1ED020I12-F is an advanced IGBT gate driver that can be also used for driving power MOS devices. Control and protection functions are included to make possible the design of high reliability systems.

The device consists of two galvanic separated parts. The input chip can be directly connected to a standard 5V DSP or microcontroller with CMOS in/output and the output chip is connected to the high voltage side.

An effective active Miller clamp function avoids the need of negative gate driving in most applications and allows the use of a simple bootstrap supply for the high side driver.

A rail-to-rail driver output enables the user to provide easy clamping of the IGBTs gate voltage during short circuit of the IGBT. So an increase of short circuit current due to the feedback via the Miller capacitance can be avoided. Further, a rail-to-rail output reduces power dissipation.

The device also includes an IGBT desaturation protection with a FAULT status output.

A READY status output reports if the device is supplied and operates correctly.

## 2.2 Internal Protection Features

## 2.2.1 Undervoltage Lockout (UVLO)

To ensure correct switching of IGBTs the device is equipped with an undervoltage lockout for both chips.

If the power supply voltage  $V_{VCC1}$  of the input chip drops below  $V_{UVLOL1}$  a turn-off signal is sent to the output chip before power-down. The IGBT is switched off and the signals at IN+ and IN- are ignored as long as  $V_{VCC1}$  reaches the power-up voltage  $V_{UVLOH1}$ .

If the power supply voltage  $V_{VCC2}$  of the output chip goes down below  $V_{UVLOL2}$  the IGBT is switched off and signals from the input chip are ignored as long as  $V_{VCC2}$  reaches the power-up voltage  $V_{UVLOH2}$ .

### 2.2.2 READY status output

The READY output shows the status of three internal protection features.

- UVLO of the input chip

- UVLO of the output chip after a short delay

- Internal signal transmission

It is not necessary to reset the READY signal since its state only depends on the status of the former protection signals.

#### 2.2.3 Watchdog Timer

The 1ED020I12-F incorporates two level of signal transmission security implemented through two independent watchdog timers. First level ensures the short term signal integrity by resending the (turn on/off) signals with a watchdog period of typical 500ns. The second level monitors during normal operation the internal signal transmission. If the transmission fails for a given time, the IGBT is switched off and the READY output reports an internal error.

#### 2.2.4 Active Shut-Down

The Active Shut-Down feature ensures a safe IGBT off-state if the output chip is not connected to the power supply.

## 2.3 Non-Inverting and Inverting Inputs

There are two possible input modes to control the IGBT. At non-inverting mode IN+ controls the driver output while IN-is set to low. At inverting mode IN- controls the driver output while IN+ is set to high. A minimum input pulse width is defined to filter occasional glitches.

## 2.4 Driver Output

The output driver section uses only MOSFETs to provide a rail-to-rail output. This feature permits that tight control of gate voltage during on-state and short circuit can be maintained as long as the drivers supply is stable. Due to the low internal voltage drop, switching behaviour of the IGBT is predominantly governed by the gate resistor. Furthermore, it reduces the power to be dissipated by the driver.

Datasheet 6 Version 2.2, 2009-12-03

### 2.5 External Protection Features

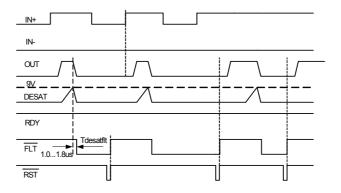

#### 2.5.1 Desaturation Protection

A desaturation protection ensures the protection of the IGBT at short circuit. When the DESAT voltage goes up and reaches 9V, the output is driven low. Further, the /FAULT output is activated. A programmable blanking time is used to allow enough time for IGBT saturation. Blanking time is provided by a highly precise internal current source and an external capacitor.

## 2.5.2 Active Miller Clamping

A Miller clamp allows sinking the Miller current during a high dV/dt situation. Therefore, the use of a negative supply voltage can be avoided in many applications. During turnoff, the gate voltage is monitored and the clamp output is activated when the gate voltage goes below 2V (related to VEE2).

## 2.5.3 Short Circuit Clamping

During short circuit the IGBTs gate voltage tends to rise because of the feedback via the Miller capacitance. An additional protection circuit connected to OUT and CLAMP limits this voltage to a value slightly higher than the supply voltage. A current of maximum 500 mA for 10us may be fed back to the supply through one of this paths. If higher currents are expected or a tighter clamping is desired external Schottky diodes may be added.

#### 2.6 RESET

The reset input has two functions.

Firstly, /RST is in charge of setting back the FAULT output. If /RST is low longer than a given time, /FLT will be reseted at the rising edge of /RST; otherwise, it will remain unchanged. Moreover, it works as enable/shutdown of the input logic.

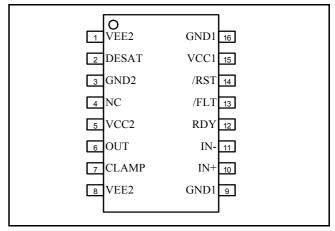

## 3 Pin Configuration and Functionality

### 3.1 Pin Configuration

|     | 1      |                                   |

|-----|--------|-----------------------------------|

| Pin | Symbol | Function                          |

| 1   | VEE2   | Negative power supply output side |

| 2   | DESAT  | Desaturation protection           |

| 3   | GND2   | Signal ground output side         |

| 4   | NC     | Not connected                     |

| 5   | VCC2   | Positive power supply output side |

| 6   | OUT    | Driver output                     |

| 7   | CLAMP  | Miller clamping                   |

| 8   | VEE2   | Negative power supply output side |

| 9   | GND1   | Signal ground input side          |

| 10  | IN+    | Non inverted driver input         |

| 11  | IN-    | Inverted driver input             |

| 12  | RDY    | Ready output                      |

| 13  | FLT    | Fault output                      |

| 14  | RST    | Reset input                       |

| 15  | VCC1   | Positive power supply input side  |

| 16  | GND1   | Signal ground input side          |

Figure 4: PG-DSO-16-15

#### 3.2 Pin Functionality

#### GND1

Ground connection of the input side.

## IN+ Non-inverting driver input

IN+ control signal for the driver output if IN- is set to low. (The IGBT is on if IN+ = high and IN- = low)

A minimum pulse width is defined to make the IC robust against glitches at IN+. An internal Pull-Down-Resistor ensures IGBT Off-State.

#### IN- Inverting driver input

IN- control signal for driver output if IN+ is set to high. (IGBT is on if IN- = low and IN+ = high)

A minimum pulse width is defined to make the IC robust against glitches at IN-. An internal Pull-Up-Resistor ensures IGBT Off-State.

#### /RST (Reset) input

<u>Function 1:</u> Enable/shutdown of the input chip. (The IGBT is off if /RST = low). A minimum pulse width is defined to make the IC robust against glitches at IN-.

Function 2: Resets the DESAT-FAULT-state of the chip if /RST is low for a time  $T_{RST}$ . An internal Pull-Up-Resistor is used to ensure FLT status output.

#### /FLT (Fault output)

Open-drain with internal pull up resistor output to report a desaturation error of the IGBT (/FLT is low if desaturation occurs)

#### RDY (Ready status)

Open-drain with internal pull up resistor output to report the correct operation of the device. (RDY = high if both chips are above the UVLO level and the internal chip transmission is faultless)

#### VCC1

5V power supply of the input chip

#### VEE2

Negative power supply pins of the output chip. If no negative supply voltage is available, both pins have to be connected to GND2.

## **DESAT (Desaturation)**

Monitoring of the IGBT saturation voltage ( $V_{CE}$ ) to detect desaturation caused by short circuits. If OUT is high,  $V_{CE}$  is above a defined value and a certain blanking time has expired, the desaturation protection is activated and the IGBT is switched off. The blanking time is adjustable by an

external capacitor.

### **CLAMP (Clamping)**

Ties the gate voltage to ground after the IGBT has been switched off at a defined voltage to avoid a parasitic switch-on of the IGBT.During turn-off, the gate voltage is monitored and the clamp output is activated when the gate voltage goes below 2V (related to VEE2).

#### CND2

Reference ground of the output chip.

#### **OUT (Driver output)**

Output pin to drive an IGBT. The voltage is switched between VEE2 and VCC2. In normal operating mode Vout is controlled by IN+, IN- and /RST. During error mode (UVLO, internal error or DESAT) Vout is set to VEE2 independent of the input control signals.

#### VCC2

Positive power supply pin of the output side.

## 4 Electrical Parameters

## 4.1 Absolute Maximum Ratings

Note: Absolute maximum ratings are defined as ratings, which when being exceeded may lead to destruction of the integrated circuit. Unless otherwise noted all parameters refer to GND1.

| Parameter                                                      | Symbol Limit          |                        | Values                 | Unit | Remarks                           |  |

|----------------------------------------------------------------|-----------------------|------------------------|------------------------|------|-----------------------------------|--|

|                                                                |                       | min. max.              |                        |      |                                   |  |

| Positive power supply output side                              | $V_{VCC2}$            | -0.3                   | 20                     | V    | 1)                                |  |

| Negative power supply output side                              | $V_{ m VEE2}$         | -12                    | 0.3                    | V    | 1)                                |  |

| Maximum power supply voltage output side $(V_{VCC2}-V_{VEE2})$ | V <sub>max2</sub>     |                        | 28                     | V    |                                   |  |

| Gate driver output                                             | $V_{OUT}$             | $V_{VEE2}$ -0.3        | $V_{max2}+0.3$         | V    |                                   |  |

| Gate driver high output maximum current                        | $I_{OUT}$             |                        | 2.4                    | A    | $t = 2\mu s$                      |  |

| Gate driver low output maximum current                         | $I_{OUT}$             |                        | 2.4                    | A    | $t = 2\mu s$                      |  |

| Maximum short circuit clamping time                            | $t_{CLP}$             |                        | 10                     | us   | $I_{CLAMP/OUT} = 500mA$           |  |

| Positive power supply input side                               | V <sub>VCC1</sub>     | -0.3                   | 6.5                    | V    |                                   |  |

| Logic input voltages (IN+,IN-,\overline{RST})                  | $V_{LogicIN}$         | -0.3                   | 6.5                    | V    |                                   |  |

| Opendrain Logic output voltage (FLT)                           | $V_{\overline{FLT}}$  | -0.3                   | 6.5                    | V    |                                   |  |

| Opendrain Logic output voltage<br>(RDY)                        | $V_{RDY}$             | -0.3                   | 6.5                    | V    |                                   |  |

| Opendrain Logic output current (FAULT)                         | $I_{\overline{FLT}}$  |                        | 10                     | mA   |                                   |  |

| Opendrain Logic output current (RDY)                           | $I_{RDY}$             |                        | 10                     | mA   |                                   |  |

| Pin DESAT voltage                                              | $V_{ m DESAT}$        | -0.3                   | V <sub>VCC2</sub> +0.3 | V    | $^{1)}V_{VEE2} = -8V$             |  |

| Pin CLAMP voltage                                              | $V_{CLAMP}$           | V <sub>VEE2</sub> -0.3 | V <sub>VCC2</sub> +0.3 | V    |                                   |  |

| Junction temperature                                           | $T_{J}$               | -40                    | 150                    | °C   |                                   |  |

| Storage temperature                                            | $T_{S}$               | -55                    | 150                    | °C   |                                   |  |

| Power dissipation, Input chip                                  | P <sub>D, IN</sub>    |                        | 100                    | mW   | $^{3)}$ @TA = 25°                 |  |

| Power dissipation, Output chip                                 | P <sub>D, OUT</sub>   |                        | 700                    | mW   | $^{3)}$ @TA = 25°                 |  |

| Thermal resistance (Input chip active)                         | R <sub>THJA,IN</sub>  |                        | 160                    | K/W  | @TA = 25°C                        |  |

| Thermal resistance (Output chip active)                        | R <sub>THJA,OUT</sub> |                        | 125                    | K/W  | @TA = 25°C                        |  |

| ESD Capability                                                 | $V_{ESD}$             |                        | 1                      | kV   | Human Body<br>Model <sup>4)</sup> |  |

<sup>1)</sup> With respect to GND2.

<sup>2)</sup> may be exceeded during short circuit clamping

<sup>3)</sup> Output IC power dissipation is derated linearly at 10 mW/°C above 62°C. Input IC power dissipation does not require derating. See section 8.1 for reference layouts for these thermal data. Thermal performance may change significantly with layout and heat dissipation of components in close proximity.

<sup>4)</sup> According to EIA/JESD22-A114-B (discharging a 100pF capacitor through a 1.5k $\Omega$  series resistor).

## 4.2 **Operating Parameters**

Note: Within the operating range the IC operates as described in the functional description. Unless otherwise noted all parameters refer to GND1.

| Parameter                                                      | Symbol                          | Symbol Limit Va        |                                 | Unit  | Remarks |

|----------------------------------------------------------------|---------------------------------|------------------------|---------------------------------|-------|---------|

|                                                                |                                 | min.                   | max.                            |       |         |

| Positive power supply output side                              | V <sub>VCC2</sub>               | 13                     | 20                              | V     | 1)      |

| Negative power supply output side                              | $V_{ m VEE2}$                   | -12                    | 0                               | V     | 1)      |

| Maximum power supply voltage output side $(V_{VCC2}-V_{VEE2})$ | V <sub>max2</sub>               |                        | 28                              | V     |         |

| Positive power supply input side                               | V <sub>VCC1</sub>               | 4.5                    | 5.5                             | V     |         |

| Logic input voltages (IN+,IN-,RST)                             | V <sub>LogicIN</sub>            | -0.3                   | 5.5                             | V     |         |

| Pin CLAMP voltage                                              | V <sub>CLAMP</sub>              | V <sub>VEE2</sub> -0.3 | V <sub>VCC2</sub> <sup>2)</sup> | V     |         |

| Pin DESAT voltage                                              | $V_{ m DESAT}$                  | -0.3                   | V <sub>VCC2</sub>               | V     | 1)      |

| Ambient temperature                                            | $T_{A}$                         | -40                    | 105                             | °C    |         |

| Common mode transient immunity <sup>3)</sup>                   | $ \Delta V_{\rm ISO}/{\rm d}t $ | _                      | 50                              | kV/μs | @ 500V  |

<sup>1)</sup> With respect to GND2.

## 4.3 Recommended Operating Parameters

Note: Unless otherwise noted all parameters refer to GND1.

| Parameter                         | Symbol            | Values | Unit | Remarks |

|-----------------------------------|-------------------|--------|------|---------|

|                                   |                   |        |      |         |

| Positive power supply output side | V <sub>VCC2</sub> | 15     | V    | 1)      |

| Negative power supply output side | V <sub>VEE2</sub> | -8     | V    | 1)      |

| Positive power supply input side  | V <sub>VCC1</sub> | 5      | V    |         |

<sup>1)</sup> With respect to GND2.

Datasheet 11 Version 2.2, 2009-12-03

<sup>2)</sup> may be exceeded during short circuit clamping

<sup>3)</sup> The parameter is not subject to production test - verified by design/characterization

## 4.4 Electrical Characteristics

Note: The electrical characteristics involve the spread of values for the supply voltages, load and junction temperatures given below. Typical values represent the median values, which are related to production processes at T=25°C. Unless otherwise noted all voltages are given with respect to GND.

## 4.4.1 Voltage Supply.

| Parameter                     | Symbol           | Limit Values |      |      | Unit | <b>Test Conditions</b> |

|-------------------------------|------------------|--------------|------|------|------|------------------------|

|                               |                  | min.         | typ. | max. |      |                        |

| UVLO Threshold Input Chip     | $V_{UVLOH1}$     | _            | 4.1  | 4.3  | V    |                        |

|                               | $V_{UVLOL1}$     | 3.5          | 3.8  | _    | V    |                        |

| UVLO Hysteresis Input Chip    | $V_{\rm HYS1}$   | 0.15         |      |      | V    |                        |

| $(V_{UVLOH1} - V_{UVLOL1})$   |                  |              |      |      |      |                        |

| UVLO Threshold Output Chip    | $V_{UVLOH2}$     | _            | 12.0 | 12.6 | V    |                        |

|                               | $V_{\rm UVLOL2}$ | 10.4         | 11.0 | _    | V    |                        |

| UVLO Hysteresis Output Chip   | $V_{ m HYS2}$    | 0.7          | 0.9  |      | V    |                        |

| $(V_{UVLOH1} - V_{UVLOL1})$   |                  |              |      |      |      |                        |

| Quiescent Current Input Chip  | $I_{Q1}$         | _            | 7    | 9    | mA   | V <sub>VCC1</sub> =5V  |

|                               |                  |              |      |      |      | IN+ = High, IN- = Low  |

|                               |                  |              |      |      |      | =>OUT = High, RDY =    |

|                               |                  |              |      |      |      | High, /FLT = High      |

| Quiescent Current Output Chip | $I_{Q2}$         | _            | 4    | 6    | mA   | $V_{VCC2} = 15V$       |

|                               |                  |              |      |      |      | $V_{VEE2} = -8V$       |

|                               |                  |              |      |      |      | IN+ = High, IN- = Low  |

|                               |                  |              |      |      |      | =>OUT = High, RDY =    |

|                               |                  |              |      |      |      | High, /FLT = High      |

## 4.4.2 Logic Input and Output

| Parameter                                       | Symbol                                     | Limit Values |      |      | Unit | <b>Test Conditions</b>                        |

|-------------------------------------------------|--------------------------------------------|--------------|------|------|------|-----------------------------------------------|

|                                                 |                                            | min.         | typ. | max. |      |                                               |

| IN+,IN-, RST Low Input Voltage                  | $V_{IN+L,}V_{IN-L,}V_{RSTL}$               | _            | _    | 1.5  | V    |                                               |

| IN+,IN-, RST High Input Voltage                 | $V_{IN+H,}V_{IN-H}$                        | 3.5          | _    | _    | V    |                                               |

| IN-, RST Input Current                          | $I_{\text{IN-},}I_{\overline{\text{RST}}}$ |              | 100  | 400  | uA   | $V_{IN}$ =GND1<br>$V_{\overline{RST}}$ =GND1  |

| IN+ Input Current                               | I <sub>IN+,</sub>                          | _            | 100  | 400  | uA   | V <sub>IN+</sub> =VCC1                        |

| RDY,FLT Pull Up Current                         | $I_{PRDY,\atop \overline{PFLT}}$           |              | 100  | 400  | uA   | $V_{RDY}$ =GND1<br>$V_{\overline{FLT}}$ =GND1 |

| Input Pulse Suppression IN+, IN-                | $T_{MININ+},$ $T_{MININ-}$                 | 30           | 40   | _    | ns   |                                               |

| Input Pulse Suppression RST for ENABLE/SHUTDOWN | T <sub>MINRST</sub>                        | 30           | 40   | _    | ns   |                                               |

| Pulse Width RST for Reseting FLT                | $T_{RST}$                                  | 800          | _    | _    | ns   |                                               |

| FLT Low Voltage                                 | $V_{FLTL}$                                 | _            | _    | 300  | mV   | $I_{SINK(\overline{FLT})} = 5mA$              |

| RDY Low Voltage                                 | $V_{RDYL}$                                 | _            | _    | 300  | mV   | $I_{SINK(RDY)} = 5mA$                         |

## 4.4.3 Gate Driver

| Symbol             |                                                                 | Limit Value             | Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <b>Test Conditions</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------|-----------------------------------------------------------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                    | min.                                                            | typ.                    | max.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| V <sub>OUTH1</sub> | V <sub>VCC2</sub> -1.2                                          | V <sub>VCC2</sub> -0.8  | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | $I_{OUTH} = -20 \text{mA}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| V <sub>OUTH2</sub> | V <sub>VCC2</sub> -2.5                                          | V <sub>VCC2</sub> -2    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | $I_{OUTH} = -200 \text{mA}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| $V_{OUTH3}$        | V <sub>VCC2</sub> -9                                            | V <sub>VCC2</sub> -5    | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | $I_{OUTH} = -1A$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| $V_{OUTH4}$        |                                                                 | V <sub>VCC2</sub> -10   | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | $I_{OUTH} = -2A$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| I <sub>OUTH</sub>  | -1.5                                                            | -2                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | IN+=High, IN-=Low;<br>OUT = High                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| V <sub>OUTL1</sub> |                                                                 | V <sub>VEE2</sub> +0.04 | V <sub>VEE2</sub> +0.09                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | $I_{OUTL} = 20 \text{mA}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| V <sub>OUTL2</sub> |                                                                 | V <sub>VEE2</sub> +0.5  | V <sub>VEE2</sub> +0.85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | $I_{OUTL} = 200 \text{mA}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| V <sub>OUTL3</sub> | _                                                               | V <sub>VEE2</sub> +2.5  | V <sub>VEE2</sub> +5.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | $I_{OUTL} = 1A$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| V <sub>OUTL4</sub> |                                                                 | V <sub>VEE2</sub> +7    | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | $I_{OUTL} = 2A$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| I <sub>OUTL</sub>  | 1.5                                                             | 2                       | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | IN+=Low, IN-=Low;<br>OUT = Low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                    | Vouth1 Vouth2 Vouth3 Vouth4 Iouth  Voutl1  Voutl2 Voutl3 Voutl4 | min.   Vouth1           | min.         typ.           V <sub>OUTH1</sub> V <sub>VCC2</sub> -1.2         V <sub>VCC2</sub> -0.8           V <sub>OUTH2</sub> V <sub>VCC2</sub> -2.5         V <sub>VCC2</sub> -2           V <sub>OUTH3</sub> V <sub>VCC2</sub> -9         V <sub>VCC2</sub> -5           V <sub>OUTH4</sub> -1.5         -2           V <sub>OUTL1</sub> V <sub>VEE2</sub> +0.04           V <sub>OUTL2</sub> V <sub>VEE2</sub> +0.5           V <sub>OUTL3</sub> V <sub>VEE2</sub> +2.5           V <sub>OUTL4</sub> V <sub>VEE2</sub> +7 | min.         typ.         max.           V <sub>OUTH1</sub> V <sub>VCC2</sub> -1.2         V <sub>VCC2</sub> -0.8         —           V <sub>OUTH2</sub> V <sub>VCC2</sub> -2.5         V <sub>VCC2</sub> -2         —           V <sub>OUTH3</sub> V <sub>VCC2</sub> -9         V <sub>VCC2</sub> -5         —           V <sub>OUTH4</sub> V <sub>VCC2</sub> -10         —           I <sub>OUTH</sub> -1.5         -2         —           V <sub>OUTL1</sub> —         V <sub>VEE2</sub> +0.04         V <sub>VEE2</sub> +0.09           V <sub>OUTL2</sub> —         V <sub>VEE2</sub> +0.5         V <sub>VEE2</sub> +0.85           V <sub>OUTL3</sub> —         V <sub>VEE2</sub> +2.5         V <sub>VEE2</sub> +5.0           V <sub>OUTL4</sub> —         V <sub>VEE2</sub> +7         — | $\begin{array}{ c c c c c c c c }\hline & min. & typ. & max. \\ \hline V_{OUTH1} & V_{VCC2}\text{-}1.2 & V_{VCC2}\text{-}0.8 & & V \\ \hline V_{OUTH2} & V_{VCC2}\text{-}2.5 & V_{VCC2}\text{-}2 & & V \\ \hline V_{OUTH3} & V_{VCC2}\text{-}9 & V_{VCC2}\text{-}5 & & V \\ \hline V_{OUTH4} & V_{VCC2}\text{-}10 & & V \\ \hline I_{OUTH} & -1.5 & -2 & & A \\ \hline V_{OUTL1} & & V_{VEE2}\text{+}0.04 & V_{VEE2}\text{+}0.09 & V \\ \hline V_{OUTL2} & & V_{VEE2}\text{+}0.5 & V_{VEE2}\text{+}0.85 & V \\ \hline V_{OUTL3} & & V_{VEE2}\text{+}2.5 & V_{VEE2}\text{+}5.0 & V \\ \hline V_{OUTL4} & & V_{VEE2}\text{+}7 & & V \\ \hline \end{array}$ |

## 4.4.4 Active Miller Clamp

| Parameter               | Symbol               | Limit Values |                         |                         |   | <b>Test Conditions</b>     |  |

|-------------------------|----------------------|--------------|-------------------------|-------------------------|---|----------------------------|--|

|                         |                      | min.         | typ.                    | max.                    |   |                            |  |

| Low Level Clamp Voltage | V <sub>CLAMPL1</sub> |              | V <sub>VEE2</sub> +0.03 | V <sub>VEE2</sub> +0.08 | V | $I_{OUTL} = 20 \text{mA}$  |  |

|                         | $V_{CLAMPL2}$        |              | V <sub>VEE2</sub> +0.3  | V <sub>VEE2</sub> +0.8  | V | $I_{OUTL} = 200 \text{mA}$ |  |

|                         | $V_{CLAMPL3}$        |              | V <sub>VEE2</sub> +1.9  | V <sub>VEE2</sub> +4.8  | V | $I_{OUTL} = 1A$            |  |

| Low Level Clamp Current | I <sub>CLAMPL</sub>  | 2            |                         |                         | A | 1)                         |  |

| Clamp Threshold Voltage | $V_{CLAMP}$          | 1.6          | 2.1                     | 2.4                     | V | Related to VEE2            |  |

<sup>1)</sup> The parameter is not subject to production test - verified by design/characterization

## 4.4.5 Short Circuit Clamping

| Parameter                                                          | Symbol                | I    | Limit Value | es   | Unit | <b>Test Conditions</b>                                                                                 |  |

|--------------------------------------------------------------------|-----------------------|------|-------------|------|------|--------------------------------------------------------------------------------------------------------|--|

|                                                                    |                       | min. | typ.        | max. |      |                                                                                                        |  |

| Clamping voltage (OUT) (V <sub>OUT</sub> -V <sub>VCC2</sub> )      | V <sub>CLPout</sub>   |      | 0.8         | 1.3  | V    | IN+=High, IN-=Low,<br>OUT=High<br>I <sub>OUT</sub> = 500mA (pulse<br>test,t <sub>CLPmax</sub> =10us)   |  |

| Clamping voltage (CLAMP) (V <sub>VCLAMP</sub> -V <sub>VCC2</sub> ) | V <sub>CLPclamp</sub> |      | 1.3         | _    | V    | IN+=High, IN-=Low,<br>OUT=High<br>I <sub>CLAMP</sub> = 500mA (pulse<br>test,t <sub>CLPmax</sub> =10us) |  |

| Clamping voltage (CLAMP)                                           | V <sub>CLPclamp</sub> |      | 0.7         | 1.1  | V    | IN+=High, IN-=Low,<br>OUT=High<br>I <sub>CLAMP</sub> = 20mA                                            |  |

## 4.4.6 **Dynamic Characteristics**

| Parameter                                                                        | Symbol              | Limit Values |      |                   | Unit | <b>Test Conditions</b>                                                                      |

|----------------------------------------------------------------------------------|---------------------|--------------|------|-------------------|------|---------------------------------------------------------------------------------------------|

|                                                                                  |                     | min.         | typ. | max.              |      |                                                                                             |

| Input to output propagation delay ON                                             | T <sub>PDON</sub>   | 165          | 185  | 750 <sup>1)</sup> | ns   | $V_{VCC1} = 5V$ ,                                                                           |

| Input to output propagation delay OFF                                            | T <sub>PDOFF</sub>  | 150          | 170  | 190               | ns   | $V_{VCC2} = 15V, V_{VEE2} = -8V$                                                            |

| Input to output propagation delay distortion                                     | T <sub>PDISTO</sub> | _            | 20   | 555 1)            | ns   | $C_{LOAD} = 100 \text{pF}$<br>$V_{IN+} = 50\%, V_{OUT} = 50\%$<br>@ 25°C                    |

| Input to output propagation delay ON variation due to temp <sup>2)</sup>         | T <sub>PDONt</sub>  | _            | _    | 20                | ns   | V <sub>VCC2</sub> =15V,V <sub>VEE2</sub> =-8V                                               |

| Input to output propagation delay OFF variation due to temp <sup>2)</sup>        | $T_{PDOFFt}$        |              | _    | 35                | ns   | $C_{LOAD} = 100 pF$<br>$V_{IN+} = 50\%$ , $V_{OUT} = 50\%$                                  |

| Input to output propagation delay distortion variation due to temp <sup>2)</sup> | $T_{PDISTOt}$       |              | _    | 20                | ns   |                                                                                             |

| Rise Time                                                                        | T <sub>RISE</sub>   | _            | 60   | _                 | ns   | V <sub>VCC2</sub> =15V,V <sub>VEE2</sub> =-8V<br>C <sub>LOAD</sub> = 1nF<br>VL 10% ,VH 90%  |

|                                                                                  |                     | _            | 400  | _                 | ns   | V <sub>VCC2</sub> =15V,V <sub>VEE2</sub> =-8V<br>C <sub>LOAD</sub> = 34nF<br>VL 10% ,VH 90% |

| Fall Time                                                                        | T <sub>FALL</sub>   | _            | 60   | _                 | ns   | V <sub>VCC2</sub> =15V,V <sub>VEE2</sub> =-8V<br>C <sub>LOAD</sub> = 1nF<br>VL 10% ,VH 90%  |

|                                                                                  |                     |              | 600  |                   | ns   | V <sub>VCC2</sub> =15V,V <sub>VEE2</sub> =-8V<br>C <sub>LOAD</sub> = 34nF<br>VL 10%,VH 90%  |

<sup>1)</sup> The maximum value of input to output propagation delay ON occures only in case of electromagnetic interferences, typically the input to output delay is 205ns at TA =25°C, one worst case watchdog clock cycle shorter (see chapter 2.2.3). The turn OFF-signal is prioritized/dominant and will not show up this behavior.

<sup>2)</sup> The parameter is not subject to production test - verified by design/characterization

## 4.4.7 **Desaturation protection**

| Parameter                            | Symbol                | Limit Values |      |      | Unit | <b>Test Conditions</b>                                                                         |  |

|--------------------------------------|-----------------------|--------------|------|------|------|------------------------------------------------------------------------------------------------|--|

|                                      |                       | min.         | typ. | max. |      |                                                                                                |  |

| Blanking Capacitor Charge Current    | I <sub>DESATC</sub>   | 215          | 250  | 295  | uA   | $V_{\text{VCC2}} = 15\text{V}, V_{\text{VEE2}} = -8\text{V}$<br>$V_{\text{DESAT}} = 2\text{V}$ |  |

| Blanking Capacitor Discharge Current | I <sub>DESATD</sub>   | 1            | 2    | _    | mA   | $V_{VCC2}$ =15V, $V_{VEE2}$ =-8V<br>$V_{DESAT}$ =6V                                            |  |

| Desaturation Reference Level         | $V_{DESAT}$           | 8.3          | 9    | 9.5  | V    | $V_{VCC2} = 15V, V_{VEE2} = -8V$                                                               |  |

| Desaturation Reference Level         | V <sub>DESAT</sub>    | 7.6          | 8.6  | 9.5  | V    | V <sub>VCC2</sub> =15V,V <sub>VEE2</sub> =0V                                                   |  |

| Desaturation Sense to OUT Low Delay  | T <sub>DESATOUT</sub> | _            | 100  | 150  | ns   | $V_{OUT}$ =90%<br>$C_{LOAD}$ = 1nF                                                             |  |

| Desaturation Sense to FLT Low Delay  | T <sub>DESATFLT</sub> | _            | _    | 2.25 | us   | $V_{\overline{FLT}}=10\%; I_{\overline{FLT}}=5mA$                                              |  |

| Desaturation Low Voltage             | V <sub>DESATL</sub>   | 0.4          | 0.6  | 0.95 | V    | IN+=Low, IN-=Low,<br>OUT=Low                                                                   |  |

## 4.4.8 Active Shut Down

| Parameter                | Symbol                           | Limit Values |      |      | Unit | <b>Test Conditions</b>                             |  |

|--------------------------|----------------------------------|--------------|------|------|------|----------------------------------------------------|--|

|                          |                                  | min.         | typ. | max. |      |                                                    |  |

| Active Shut Down Voltage | V <sub>ACTSD</sub> <sup>1)</sup> |              |      | 4    | V    | I <sub>OUT</sub> =-200mA,<br>V <sub>CC2</sub> open |  |

<sup>1)</sup> With reference to VEE2

**Insulation Characteristics**

## 5 Insulation Characteristics

## 5.1 DIN EN 60747-5-2 (VDE 0884 Teil 2): 2003-01. Basic Insulation

| Description                                                            | Symbol            | Characteristic | Unit              |  |

|------------------------------------------------------------------------|-------------------|----------------|-------------------|--|

| Installation classification per EN 60664-1, Table 1                    |                   |                |                   |  |

| for rated mains voltage $\leq 150 \text{ V}_{RMS}$                     |                   | I-IV           |                   |  |

| for rated mains voltage $\leq 300 \text{ V}_{RMS}$                     |                   | I-III          |                   |  |

| for rated mains voltage $\leq$ 600 $V_{RMS}$                           |                   | I-II           |                   |  |

| Climatic Classification                                                |                   | 55/105/21      |                   |  |

| Pollution Degree (EN 60664-1)                                          |                   | 2              |                   |  |

| Minimum External Clearance                                             | CLR               | 8.12           | mm                |  |

| Minimum External Creepage                                              | CPG               | 8.24           | mm                |  |

| Minimum Comparative Tracking Index                                     | CTI               | 175            |                   |  |

| Maximum Repetitive Insulation Voltage                                  | V <sub>IORM</sub> | 1420           | $V_{PEAK}$        |  |

| Input to Output Test Voltage, Method b <sup>1)</sup>                   | $V_{PR}$          | 2663           | $V_{PEAK}$        |  |

| $V_{IORM} * 1.875 = V_{PR}$ , 100% Production Test with $t_m = 1$ sec, |                   |                |                   |  |

| Partial Discharge < 5pC                                                |                   |                |                   |  |

| Input to Output Test Voltage, Method a <sup>1)</sup>                   | $V_{PR}$          | 2272           | $V_{PEAK}$        |  |

| $V_{IORM} * 1.6 = V_{PR}$ , Type and sample Test, $t_m = 60$ sec,      |                   |                | T Exit            |  |

| Partial Discharge < 5pC                                                |                   |                |                   |  |

| Highest Allowable Overvoltage <sup>1)</sup>                            | V <sub>IOTM</sub> | 6000           | V <sub>PEAK</sub> |  |

| Maximum Surge Insulation Voltage                                       | V <sub>IOSM</sub> | 6000           | V                 |  |

| Insulation Resistance at $T_s$ , $V_{IO} = 500 \text{ V}$              | R <sub>IO</sub>   | >109           | Ω                 |  |

<sup>1)</sup> Refer to VDE 0884 for a detailed description of Method a and Method b partial discharge test profiles.

### 5.2 UL 1577

| Description                         | Symbol           | Characteristic | Unit             |

|-------------------------------------|------------------|----------------|------------------|

| Insulation Withstand Voltage / 1min | V <sub>ISO</sub> | 3750           | V <sub>rms</sub> |

| Insulation Test Voltage / 1sec      | V <sub>ISO</sub> | 4500           | V <sub>rms</sub> |

## 5.3 Reliability

For Qualification Report please contact your local Infineon Technologies office.

<sup>\*</sup>Note 1:Insulation characteristics are guaranteed only within the safety maximum ratings which must be ensured by protective circuits in application. Surface mount classification is class A in accordance with CECCOO802.

<sup>\*</sup>Note 2: This coupler is suitable for "basic insulation" only within the safety ratings. Compliance with the safety ratings shall be ensured by means of suitable protective circuits.

**Timing Diagrams**

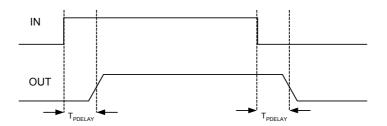

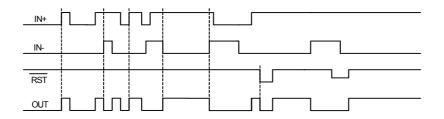

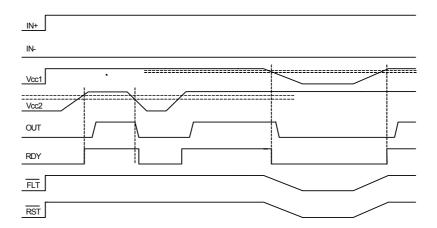

# 6 Timing Diagrams

Figure 5: Propagation Delay

Figure 6: Turn-on and Turn-off

Figure 7: Desaturation Fault

Datasheet 17 Version 2.2, 2009-12-03

**Timing Diagrams**

Figure 8: UVLO

**Package Outlines**

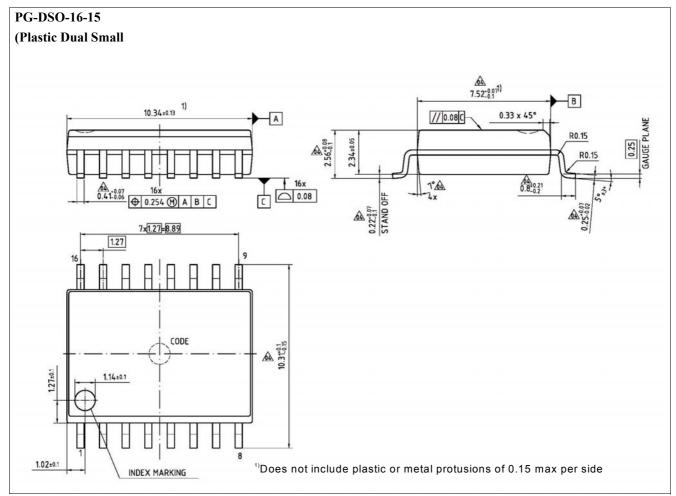

# 7 Package Outlines

Figure 9: PG-DSO-16-15

**Application Notes**

## **8** Application Notes

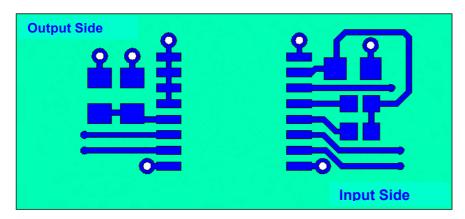

## 8.1 Reference Layout for Thermal Data

The PCB layout shown in figure 12 represents the reference layout used for the thermal characterisation. Pins 9 and 16 (GND1) and pins 1 and 8 (VEE2) require ground plane connections for achiving maximum power dissipation. The 1ED020I12-F is conceived to dissipate most of the heat generated through this pins.

PCB + Top-Layer

PCB + Bottom-Layer

Total Area =  $374.4 \text{ mm}^2$

Figure 10: Reference layout for thermal data (Copper thickness 105μm)

## **8.2** Printed Circuit Board Guidelines

Following factors should be taken into account for an optimum PCB layout.

- Sufficient spacing should be kept between high voltage isolated side and low voltage side circuits.

- The same minimum distance between two adjacent high-side isolated parts of the PCB should be maintained to increase the effective isolation and reduce parasitic coupling.

- In order to ensure low supply ripple and clean switching signals, bypass capacitor trace lengths should be kept as short as possible.

Datasheet 20 Version 2.2, 2009-12-03

**Application Notes**

## **Total Quality Management**

Qualität hat für uns eine umfassende Bedeutung. Wir wollen allen Ansprüchen in der bestmöglichen Weise gerecht werden. Es geht uns also nicht nur die Produktqualität um unsere Anstrengungen gelten gleichermaßen der Lieferqualität und Logistik, dem Service sowie allen und Support sonstigen Beratungs- und Betreuungsleistungen.

Dazu gehört eine bestimmte Geisteshaltung unserer Mitarbeiter. Total Quality im Denken und Handeln gegenüber Kollegen, Lieferanten und Ihnen, unserem Kunden. Unsere Leitlinie ist jede Aufgabe mit "Null Fehlern" zu lösen – in offener Sichtweise auch über den eigenen Arbeitsplatz hinaus – und uns ständig zu verbessern.

Unternehmensweit orientieren wir uns dabei auch an "top" (Time Optimized Processes), um Ihnen durch größere Schnelligkeit den entscheidenden Wettbewerbsvorsprung zu verschaffen.

Geben Sie uns die Chance, hohe Leistung durch umfassende Qualität zu beweisen.

Wir werden Sie überzeugen.

Quality takes on an allencompassing significance at Semiconductor Group. For us it means living up to each and every one of your demands in the best possible way.

So we are not only concerned with product quality. We direct our efforts equally at quality of supply and logistics, service and support, as well as all the other ways in which we advise and attend to you.

Part of this is the very special attitude of our staff. Total Quality in thought and deed, towards co-workers, suppliers and you, our customer. Our guideline is "do everything with zero defects", in an open manner that is demonstrated beyond your immediate workplace, and to constantly improve.

Throughout the corporation we also think in terms of Time Optimized Processes (top), greater speed on our part to give you that decisive competitive edge.

Give us the chance to prove the best of performance through the best of quality – you will be convinced.

www.infineon.com/gatedriver